1

Изобретение относится к области автоматики и вычислительной техники и предназначено для реализации логических ф;ункций.

Известны настраиваемые логические автоматы, которые реалиavtoT переключательн ю функцию (ПФ), зависящую от соответствующего набора включенных переключателей или комбинации настраивающих управляющих сигналов. После введения кодов настройки такое устройство выполняет роль комбинационной схемы, выходные сигналы ( L 1,2,3... АП. ) которой связаны с входными сигналами Xs (S 1,2,3,., /гх) системой логических уравнений

(Xi,X2,X3, ...,Xg,... , X ),)

Известный логический автомат содержит ( Лх-/)-разрядный счетчик (где /ь- число переменных, / : п- ), выходы которого соедирнены со входами распределителя, а выходы распределителя соединены со входами блока ввода чисел настройки, первый управляющий триггер, единичный и нулевой выходы которого соединены с блокирующим входом счетчика и первой схемы совпадения соответственно, а нулевой вход этого триггера соединен с соответствующим выходом распределителя, второй управляющий триггер, единичный вход которого соединен с выходом второй схемы совпадения, а выход соединен со

входом первой схемы совпадения, единичный вход первого и нулевой вход второго управляющих триггеров соединены с шиной запуска устройства, соединенной со входом

двоичного счетчика, блок формировария переключательных функций

2. переменных и блок формирования конъюнкций / переменных.

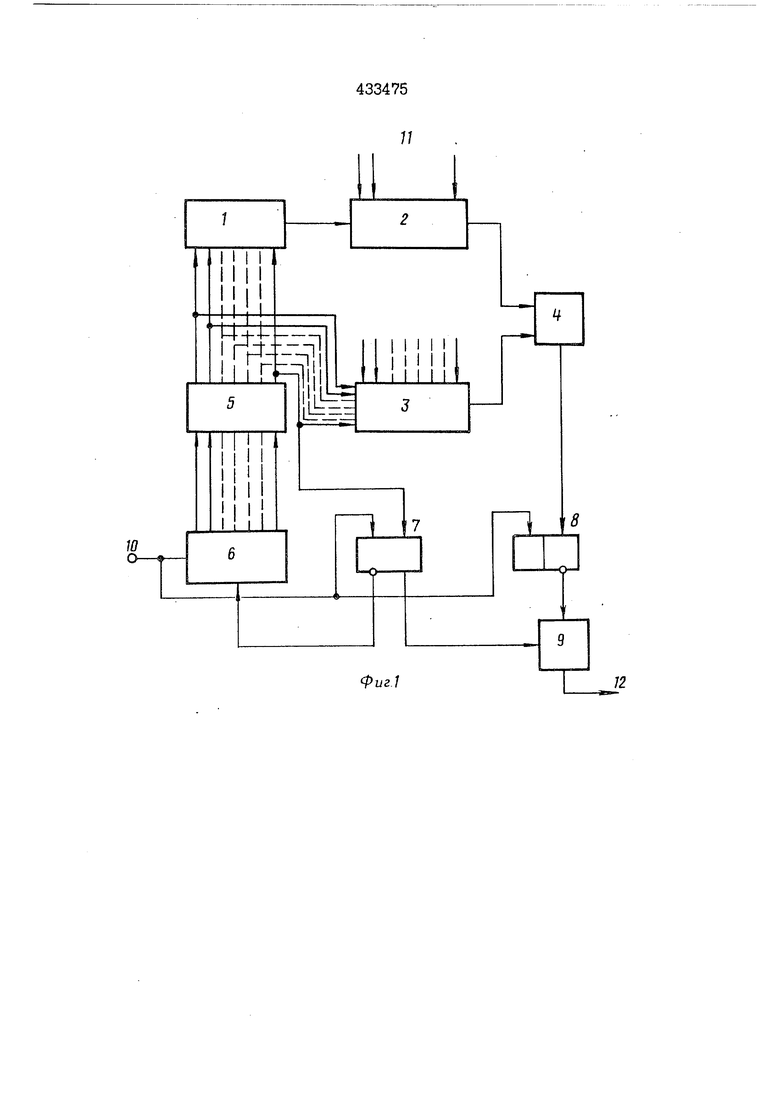

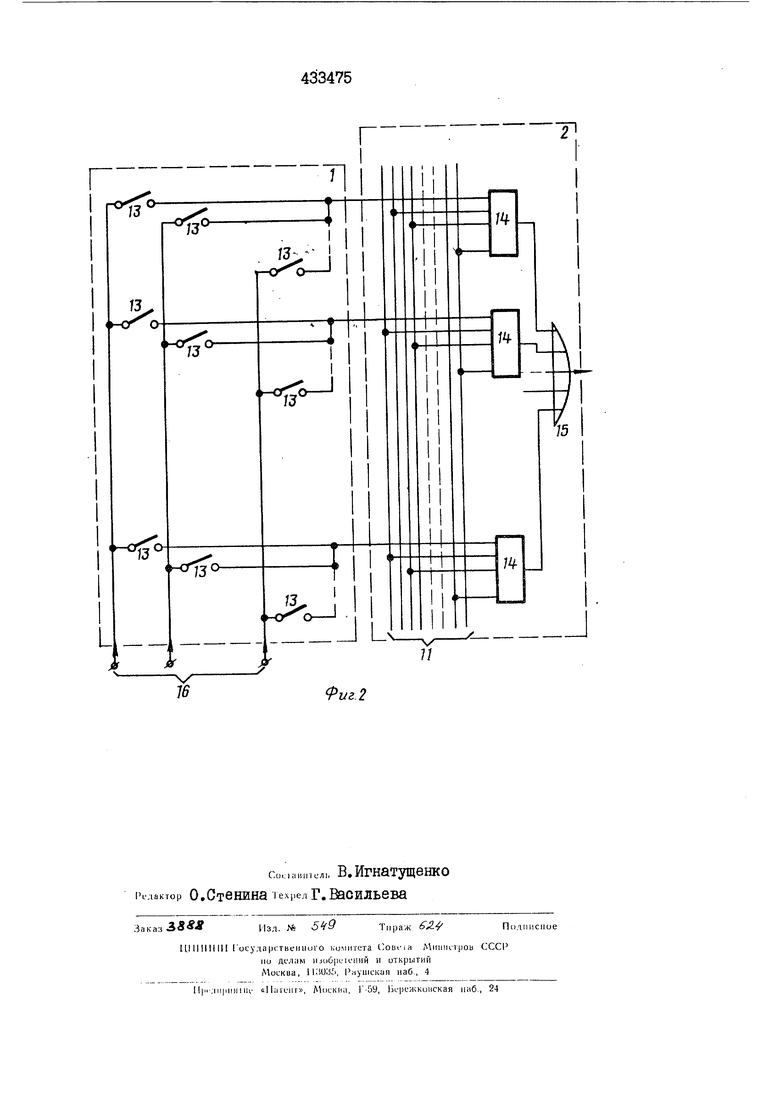

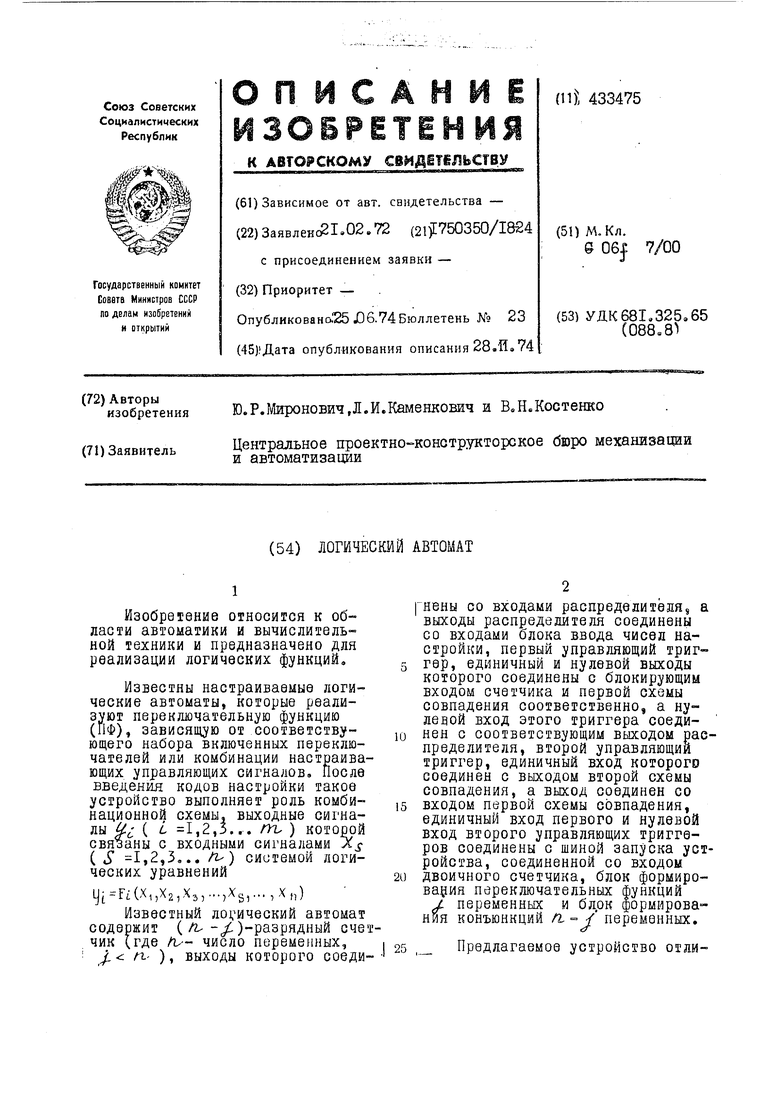

, Предлагаемое устройство отличается oi известного sew, что выходы распределителя соединены со входом бло{са формирования конъюнкций /L.- . переменных, выход которого сб динен со входом второй схемы совпадения, выходы блока ввода чисел настройки соединены со входами блока формирования переключательных функций J. переменных, выход которого соединен с другим входом второй схемы совпадения. Это позволяет повысить быстро действие устройства, функционирование которого базируется на следующих предпосылках. Вводимый временный.интервал Т разбивается на . элементарных интервалов tol (подциклов), в течение каждого из которых формируются сигналы согласно выражениям toifji-( .. Xi), и их логического произведения (конъюнкции) пх.torlj-L. Логическое суммирование.(дизъюнкция) этих конъюнкций приводит к ряду разложения ПФ , F(Xi,.Vo,,..,Xn,t-To) по п- j переменным f toifj/(A2 03lj24.c 2 -Jto2 -J fjl -i При где o(L-,n.4s-Xn-Xn-v-Xj-i , л обобщение обозначения входноИ переменной и ее.йнверсии. На фигл изображена схема пре лагаемого устройства. Устройство .содержит блок I ввода чисел настройки, блок 2 формирования переключательных функций переменных (типа с, /V/ ), блок 3 формирования конъюнкций (/1-/ ) переменных (типа for П s 5i схему сов падения , распределител 5, (Л-у )-разрядный счетчик 6, (где/2-- число переменных,/г-У управляюш.ие триггеры 7 и 8, схему совпадении 9, шину запуска 10, вх ды II для подачи переменных Хт, Хро, о ,1. ; , выход 12, СНа фиго2 представлена функцио нальная схема блока ввода чисел н стройки и блока формирования пере ключательных функций / переменных. Устройство функционирует слеующим образом. В исходном состоянии триггеры 7 и 8 установлены, как показано на фигД, т.е. двоичный счетчик 6 заблокирован по счетному входу нулевым потенциалом с правого выхода триггера 7. С подачей пускового импульса по шине 10 изменяет свое состояние триггер 7 (триггер 8 изменяет свое состояние толь ко в том случае, если он на предыдущем цикле сигналом с выхода схемы 4 был становлен в единичное состояние), в результате чего деблокируется счетчик 6, по второму входу блокируется схема совпадения 9. Счетчик б начинает отсче импульсов, и выходные сигналы разрядов счетчика подаются на входы распределителя 5 импульсов. Выходные сигналы последнего подаются одновременно на соответствующие входы управления блока I ввода чисел настройки и блока 3, формирующего функции toigft/S С поступлением каждого нового тактирующего импульса вырабатывается новое число настройки (по установлинной программе); таким образом, каждому формируемому интервалу времени соответствует своя переключатольная функция (11Ф) cL rj-i- i формируемая блоком 2, Аналогачно, в блоке 3 с какдым новым импульсом формируется новая /« функции Loi/Jc Lf,i подаются на входы таемы совпадения ; следовательно, на ее B|jxoA6 формируются функции 4. У/с При состоянии триггеров 7 и 8, принятых ими после очередного пускового импуль9а (с выполнапием условия tai -}LL I для произвольного фиксированного i, ), в триггер 8 записывается единица, которая с его выхода подается на первый вход схемы совпадения 9. Очевидно, при tf,iJ;io(.L О в триггер о записывается нуль. Последним импульсом распределителя 5 триггер 7 возвращается в исходное состояние, вследствие чего блокируется счетчик б и деблокируется по второму входу схема 9, на выходе которой форми|/уэгся значение функции Лп,-То) F(X,,X It п.

при заданном наборе входных переменных Хт,Хр,.,,Хл , Х/

После смены комбинаций значений входных переменных схема находится в состоянии готовности к приему следующего пускового импульса.

БЛОКИ I и 2 состоят из , переключателей 15 ( 2% которые формируют требуемую последовательность чисел настройки, подаваемых на входы логических элементов 14 (число которых равно 2), формирующих единичные конституенты на наборе переменных ХтДр,...Х/ . Выходы элементов 14 соединены со входами схемы ИМ 15. В качестве элементов 14 могут быть использованы схемы И, ИЛИ-НЕ и подобные.

С помощью переключателей 13 обеспечивается возможность исключения необходимого множества единичных конституент. Так. например, при использовании схем И в качестве элементов 14. на управляющие входы 16 блока. (число которых равно 2. ) следует коммутировать нули на те входы, которые соответствуют исключаемым конетитуентам.

Количество аппаратуры для технической реализации предложенного устройства находится в функциональной зависимости не только от числа входных переменных /г , но также от параметра J- разбиения /г входных переменных на две группы. Оптимальное разбиение определяется по формуле

j,, I,43tn (/

n+3

2+2 -I,43)-I,

при котором требуется минимальное количество оборудования для построт ения устройства.

Повышение быстродействия логического автомата обеспечивается гем, что время просмотра программы задания фиксиррванной ПФ равно не

2 Л/гV тактам.

ПРЕДМЕТ ИЗОБРЕТЕНИЯ

Логический автомат, содержащий (/г-- ;/- )-разрядный счетчик (где /Z-- число переменных,),

выходы которого соединены со вхо- дами распределителя, а выходы распределителя соединены со входами блока ввода чисел настройки, первый управляющий триггер, единичный и нулевой выходы которого соединены с блокирующим входом счетчика и первой схемы совпадения соответственно, а нулевой вход этого триггера соединен с

соответствующим выходом распределителя, второй управляющий триггер, единичный вход которого соединен с выходом второй схемы совпадения, а выход соединен со

входом первой схемы совпадения, единичный вход первого и нулевой вход второго управляющих триггеров соединены с шиной запуска устройства, соединенной со входом

двоичного счетчика, блок формирог вания переключательных функций Jпеременных, блок, формирования конъюнкций/ь- переменных, отличающийся тем. что, с целью повышения быстродействия, выходы распределителя соединены со входом блока формирования конъюнкций /г-сА переменных, выход которого соединен со входом второй

схемы совпадения, выходы блока ввода чисел настройки соединены со входами блока формирования переключательных функций J. переменных, выход которого соединен ,

с другим входом второй схемы сов-, падения.

433475 11

75

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ МИНИМИЗАТОР БУЛЕВЫХ ФУНКЦИЙ | 1970 |

|

SU271897A1 |

| Устройство для вычисления булевых дифференциалов | 1988 |

|

SU1689942A1 |

| УСТРОЙСТВО для ИССЛЕДОВАНИЯ НАДЕЖНОСТИ ФУНКЦИОНИРОВАНИЯ СИСТЕМ | 1968 |

|

SU206918A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Функциональный преобразователь | 1978 |

|

SU781822A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ | 1991 |

|

RU2030781C1 |

| Формирователь последовательности импульсов | 1980 |

|

SU949782A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Автоматический синтезатор релейных схем | 1978 |

|

SU723586A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

Даты

1974-06-25—Публикация

1972-02-21—Подача