(54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ КОНЕЧНЫХ

1

Изобретение относится к цифровой вычислительной технике и может быть использовано при моделировании конечных автоматов с учетом неисправностей.

Известно специализированное цифровое вычислительное устройство, содержащее ЦВМ, блок запоминания логических значений, блок запоминания описания логической схемы, блок выделения логических значений, блок управления, два коммутатора, блок вентилей, входной регистр, блок логических элементов и блок сравнений 1.

Недостатком указанного устройства являются большие аппаратурные затраты, обусловленные использованием, ЦВМ, работающей совместно с устройством, а также использованием блока логических элементов для формирования значений логических функций. Кроме того, недостатком указанного устройства является невозможность автоматического моделирования цифровых схем, содержащих неисправности из заданного списка неисправностей.

Наиболее близким по технической сущности к изобретению является устройство для моделирования конечных автоматов, содержащее два счетчика, два блока памяти.

АВТОМАТОВ

два дешифратора, два регистра, блок сравнения, мультиплексор, сумматор по модулю два, коммутатор, блок задержки и блок вычисления булевых функций 2.

Недостатком известного устройства яв ляется быстродействие, обусловленное по.следовательным вычислением конъюнкций (дизъюнкций) нескольких переменных, входящих в выражения функций.

Цель изобретения - повышение быстродействия устройства для моделирования конечных автоматов.

Поставленная цель достигается тем, что в устройство для моделирования конечных автоматов, содержащее коммутатор, первый управляющий вход которого является входом устройства, первый и второй блоки памяти, первые выходы которых подключены соответственно к первому и второму входам первого счетчика, выход которого соединен с первым входом блока сравнения, в .Ч)рой

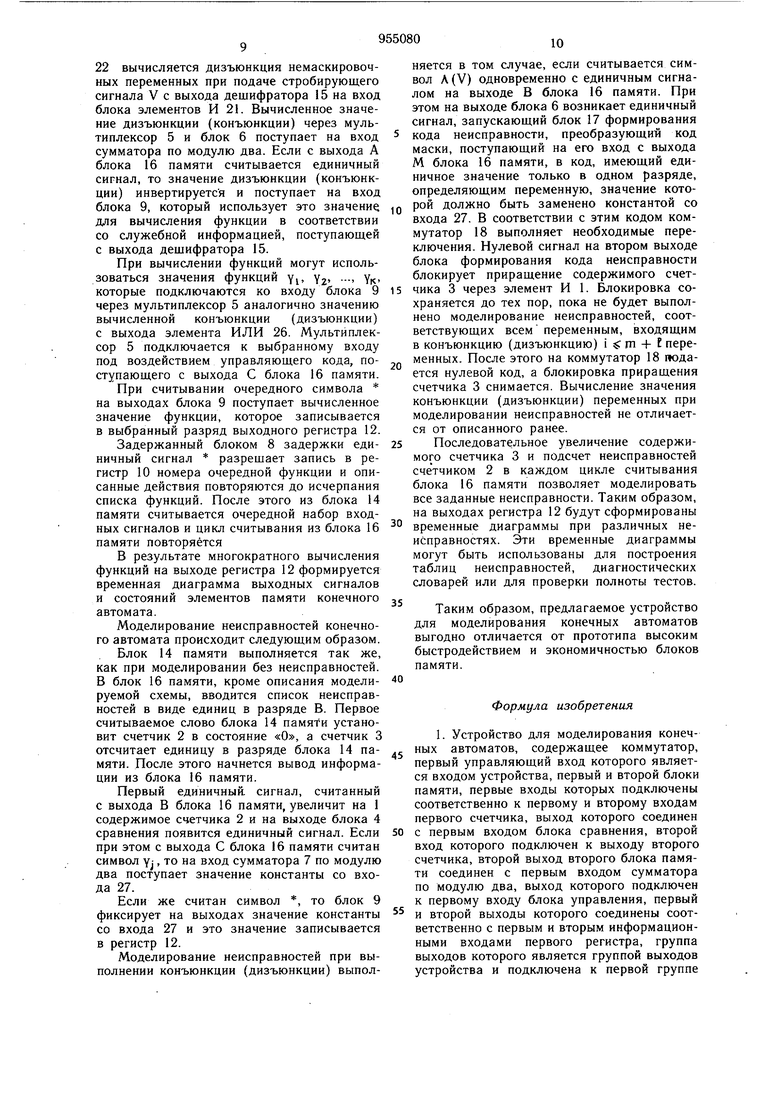

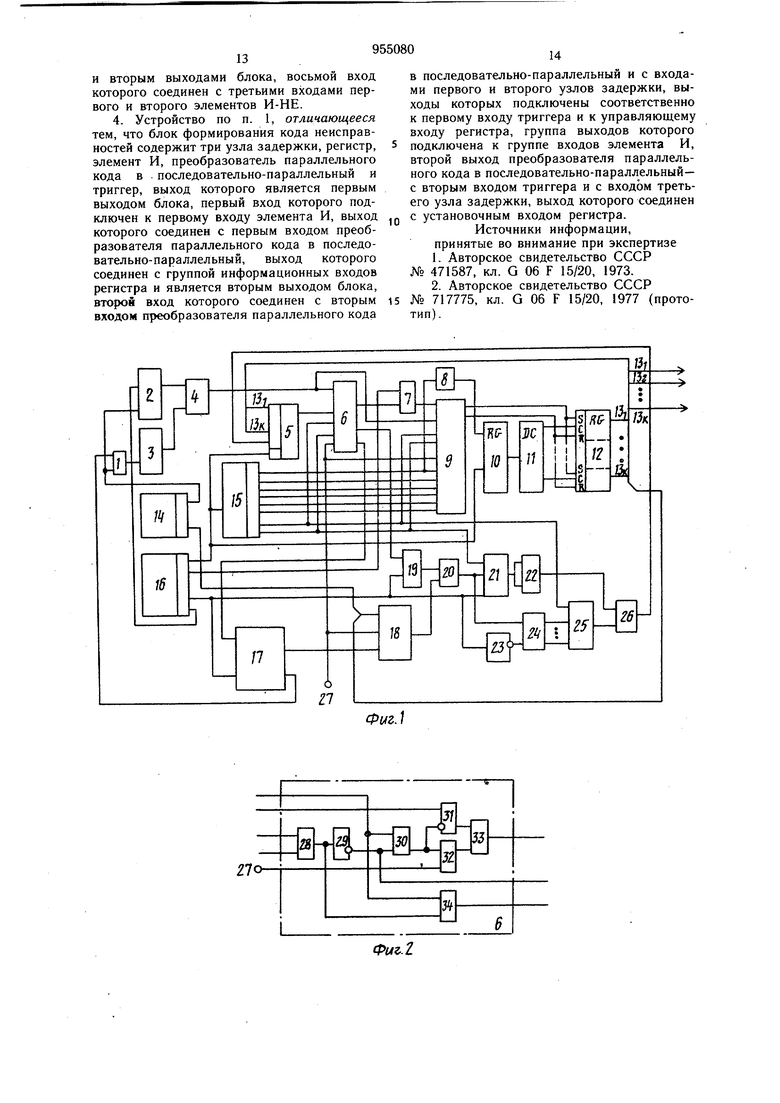

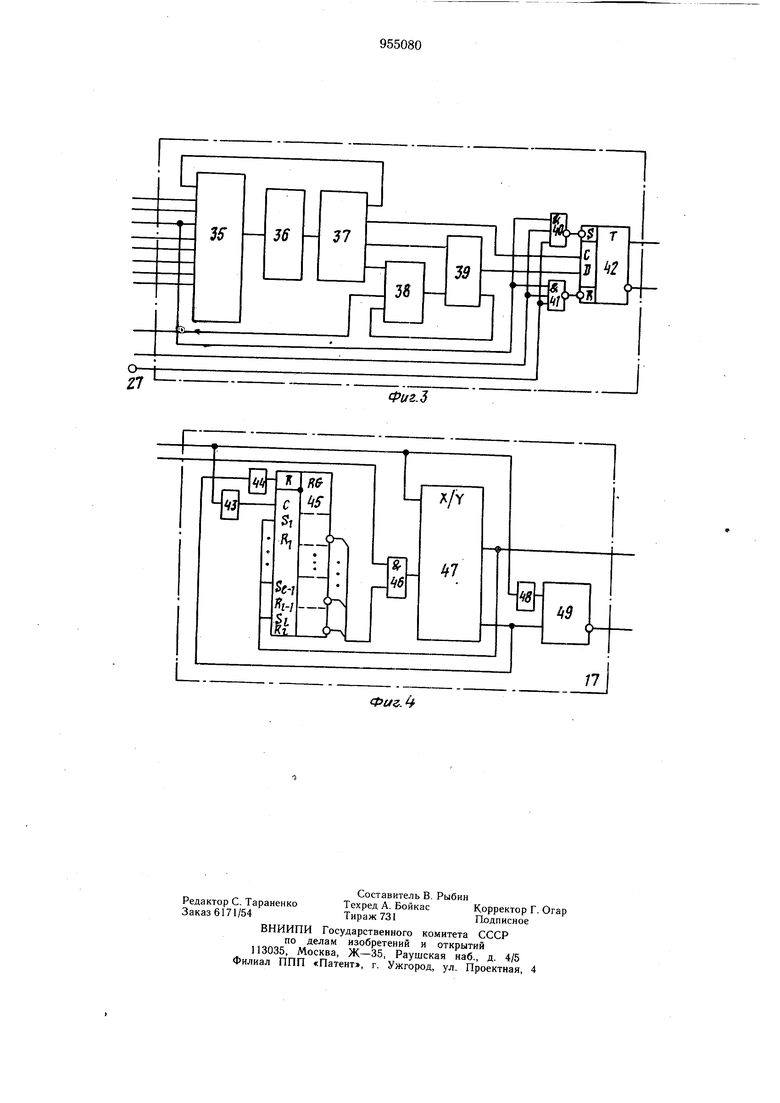

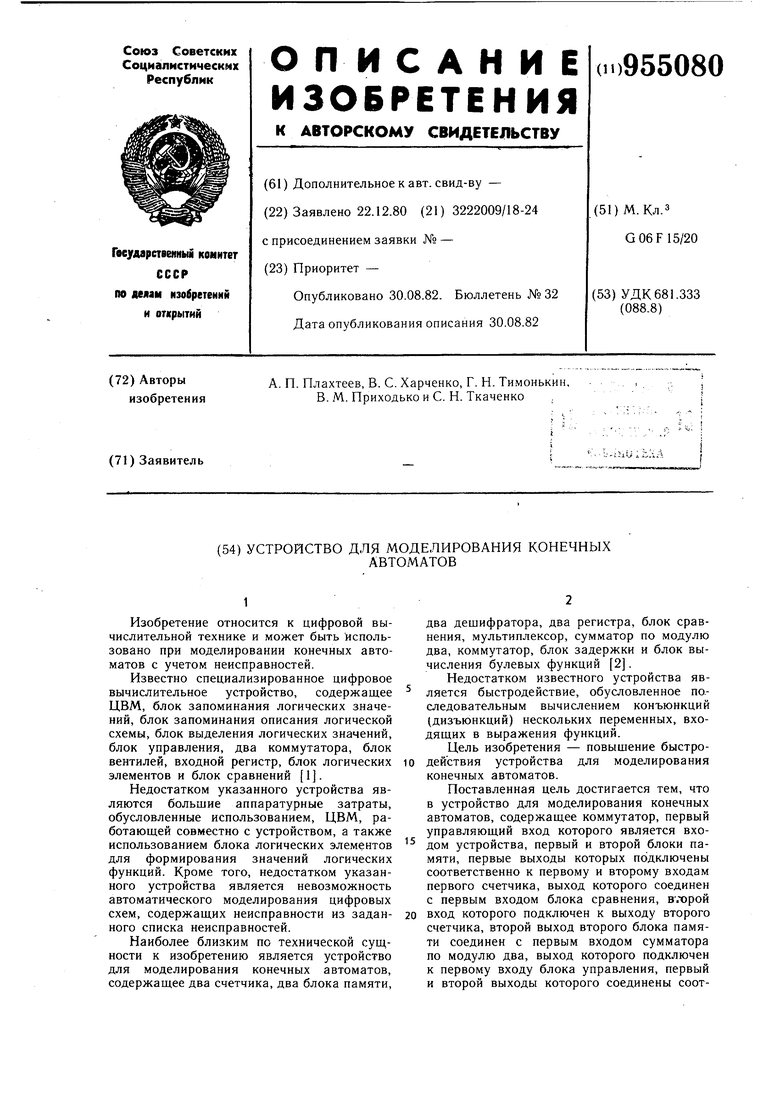

20 вход которого подключен к выходу второго счетчика, второй выход второго блока памяти соединен с первым входом сумматора по модулю два, выход которого подключен к первому входу блока управления, первый и второй выходы которого соединены соответственно с nepBbiirf и вторым информационными входами первого регистра, группа выходов которого является группой выходов устройства и подключена к первой группе входов мультиплексора, первый дешифратор, первый, второй, третий, четвертый, пятый и шестой выходы которого соединены соответственно с вторым, третьим, четвертым, пятым, шестым и седьмым входами блока управления, второй вход которого соединен с входом блока задержки, выход которого подключен к управляющему входу второго регистра, группа выходов которого соединена с группой входов второго дешифратора, группа выходов которого подключена к группе управляющих входов первого регистра. введены два элемента И, два элемента ИЛИ, блок элементов И, блок элементов ИЛИ, блок элементов НЕ, блок сумматоров по модулю два, третий регистр, блок выбора режима работы и блок формирования кода неисправности, причем третий выход второго блока памяти соединен с информационным входом второго регистра, с управляющим входом мультиплексора и с информационным входом первого дешифратора, седьмой и восьмой выходы которого подключены соответственно к первому и второму входам блока выбора режима работы и к первым входам первого элемента И и блока элементов И, группа выходов которого соединена с группой входов первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен со стробирующим входом мультиплексора, выход которого подключен к т ретьему входу блока выбора режима работы, четвертый вход которого соединен с выходом блока сравнения и подключен к десятому входу блока управления, одиннадцатый вход которого соединен с входом устройства и подключен к пятому входу блока выбора режима работы, первый выход которого соединен с вторым входом сумматора по модулю два, четвертый выход второго блока памяти соединен с входом блока элементов НЕ, с вторым входом блока элементов И, с информационным бходом третьего регист)эа и с первым входом блока формирования кода неисправности, первый выход которого подключен к первому входу второго элемента И, второй вход которого соединен с первым выходом первого блока памяти, группа информационных выходов которого подключена в первой группе информационных входов коммутатора, вторая группа информационных входов которого соединена с группой выходов первого регистра, второй выход блока формирования кода неисправностей подключен к второму управляющему входу коммутатора, выход которого соединен с первым входом блока сумматоров по модулю два, выход которого подключен к третьему входу блока элементов И и к первому входу блока элементов ИЛИ, второй вход которого соединен с выходом блока элементов НЕ, группа выходов блока элементов ИЛИ подключена к группе входов первого элемента И, второй и третий выходы блока выбора режима работы соединены соответственно с вторым входом блока формирования кода неисправности и управляющим входом третьего регистра, выход которого подключен к второму входу блока сумматоров по модулю два. Кроме того, блок выбора режима работы содержит три элемента И, два элемента ИЛИ, элемент НЕ и элемент запрета, прямой вход которого является третьим входом блока, четвертый вход которого подключен к первым входам первого и второго элементов И, выход второго элемента И является вторым выходом блока, пятый вход которого соединен с первым входом третьего элемента И, второй вход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом первого элемента И и подключен к инверсному входу элемента запрета, выход которого подключен к первому входу первого элемента ИЛИ, выход которого является первым выходом блока, первый и второй входы которого соединены соответственно с первым и вторым входом второго элемента ИЛИ, выход которого подключен к второму входу второго элемента И и соединен с входом элемента НЕ, выход которого является третьим выходом блока и подключен к второму входу первого элемента И; Кроме того, блок управ ления содержит дешифратор, блок памяти, узел вычисления булевых функций, регистр, два элемента И-НЕ, Д-триггер и преобразователь параллельного кода в последовательно-паралельный, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого являются соответственно первым, десятым, восьмым, девятым, одиннадцатым, вторым, третьим и четвертым входами блока, пятый вход которого соединен с первым входом узла вычисления булевых функций, выход которого подключен к первому входу регистра, первый выход которого соединен с вторым входом узла вычисления булевых функций, третий вход которого подключен к первому выходу блока памяти, второй выход которого соединен с вторым входом регистра, второй выход которого подключен к информационному входу Д-триггера, управляющий вход которого соединен с третьим выходом блока пам:яти, четвертый выход которого подключен к девятому входу преобразователя параллельного кода в последовательно-параллельный, выход которого соединен с входом дешифратора, выход которого соединен с входом блока памяти, шестой и седьмой входы блока соединены соответственно с объединенными первым и вторым входами первого и второго элементов И-НЕ, выходы которых подключены соответственно к первому и второму установочным входам Д-триггера, прямой и инверсный выходы которого являются соответственно первым и вторым выходами блока, восьмой вход которого соединен с третьими входами первого и второго элементов И-НЕ. Кроме того, блок формирования кода неисправностей содержит три узла задержки, регистр, элемент И, преобразователь параллельного кода в последовательно-параллельный и триггер, выход которого является первым выходом блока, первый вход которого подключен к первому входу элемента И, выход которого соединен с первым входом преобразователя параллельного к;ода в последовательно-параллельный, выход которого соединен с группой информационных входов регистра и является вторым выходом блока, второй вход которого соединен с вторым входом преобразователя параллельного кода в последовательно-параллельный и с входами первого и второго узлов задержки выходы которых подключены соответственно к первому входу триггера и к управляющему входу регистра, группа выходов которого подключена к группе входов элемента И, второй выход преобразователя параллельного кода в последовательно-параллельный- с вторым входом триггера и с входом третьего узла задержки, выход которого соединен с установочным входом регистра. На фиг. 1 представлена функциональная схема устройства для моделирования конечных автоматов; на фиг. 2 - функциональная схема блока выбора режима работы; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - функциональная схема блока формирования кода неисправности. Устройство содержит элемент И 1, счетчики 2 и 3, блок 4 сравнения, мультиплексор 5, блок 6 выбора режима работы, сумматор 7 по модулю два, блок 8 задержки, блок 9 управления, регистр 10, дещифратор 11, регистр 12, выходы устройства 13i - 13к, блок 14 памяти, дещифратор 15, блок 16 памяти, блок 17 формирования кода неисправности, коммутатор 18, регистр 19, блок 20 сумматоров по модулю два, блок 21 элементов И, элемент ИЛИ 22, блок 23 элементов НЕ, блок 24 элементов ИЛИ, элемент И 25, элемент ИЛИ 26, вход 27 константы-аргумента. Блок 6 выбора режима работы содержит элемент ИЛИ- 28, элемент НЕ 29, элементы И 30, элемент 31 запрета, элементы 32, элемент ИЛИ 33, элемент И 34. Блок 9 управления содержит преобразователь 35 параллельного кода в последовательно-параллельный, дещифратор 36, блок 37 памяти, узел 38 вычисления булевых функций, регистр 39, элементы И-НЕ 40 и 41, Д-триггер 42. Блок 17 формирования кода неисправноети содержит узлы 43 и 44 задержки, регистр 45, элемент И 46, преобразователь 47 параллельного кода в последовательнопараллельный узел 48 задержки, триггер 49. Устройство работает следующим образом. Устройство имеет два режима работы: модулирование конечных автоматов безнеисправностей и модулирование различных неисправностей конечных автоматов. Единичный сигнал на первом выходе блока 6 выбора режима работы возникает при подаче единичного сигнала на его четвертый, а также на один из входов элемента ИЛИ 28. На первый выход через элемент И 31 и элемент ИЛИ 33 блока 6 поступает сигнал с первого входа при нулевом сигнале на четвертом входе либо нулевых сигналов на входах элемента ИЛИ 28. При единичном сигнале на одном из входов элемента ИЛИ 28 и единичном сигнале, поступающем на входы элементов И 30 и 34, на второй выход блока 6 через элементы И 32 и элемент ИЛИ 33 поступает сигнал с входа 27 устройства. Единичный сигнал на третьем выходе блока 6 возникает при подаче ну.яевы. сигналов на входы элемента ИЛИ 28. Управляющие входные сигналы блока 9 управления и код следующего адреса с выхода блока 37 памяти поступают на входы преобразователя 35. На его выходе формируется адрес очередной микрокоманды, который через дешифратор 36 поступает на адресный вход блока 37 памяти. Микрокоманды, считываемые из блока 37 памяти, содержат поле следующего адреса, разряд управления приемом значения функции в триггер 42, поле управления блоком регистра 39 и поле управления блоком 38. Блок 38 под воздействием управляющих кодов выполняет вычисление логических функций, оперируя с информационными сигналами, поступающими на вход блока 9 и промежуточными результатами, поступающими из блока регистров. Результаты вычисления записывются в регистр 39. Узел 38 выполняет операции И, ИЛИ, НЕ. Конечный результат вычисления функций записывается в триггер 42. Если на первый и восьмой входы вычислителя 9 функций поступают единичные сигналы, то триггер 42 через элементы И 40 и 41 устанавливается в состояние, определяемое значением сигнала на входе 27. При поступлении единичного сигнала синхронизации на входы элемента, узла 43 и 48 задержки и преобразователя 47, на выходе преобразователя возникает (т + t)разрядный код, в котором только в одном разряде содержится единица. Этот разряд соответствует самому младщему разряду входного кода, имеющему единичное значение. Выходной код преобразователя 47 поступает на выход блока 17 формирования кода неисправности и на единичные входы регистра 45. При поступлении синхронизации задержанного узла 43 задержки единичного сигнала регистр 45 выполняет операцию ИЛИ над записанным в нем кодом и входным кодом. При этом на соответствующем инверсном выходе регистра 45 возникает нулевой сигнал, который посредством блока элементов И 46 маскирует единичное значение разряда входного кода (младшую единицу). При поступлении очередного единичного сигнала на вход преобразователя 47 кодов выделяется следующая единица входного кода и т. д. Одновременно через узел 48 задержки триггер 49 устанавливается в единичное состояние. Если на входе преобразователя 47 нулевой код, то при поступлении сигнала синхронизации на первом выходе преобразователя возникает нулевой сигнал, а на втором выходе - единичный сигнал, который удерживает триггер 49 в нулевом состоянии и через узел 44 задержки устанавливает регистр- 45 в нулевое состояние. Единичные выходные сигналы регистра позволяют передавать без маскирования код со входа формирователя кода неисправности на вход преобразователя 47. Моделируемый конечный автомат онисывается в виде системы булевых функций. Эти функции должны быть представлены в форме, при которой знаки отрицания относятся либо только к одному аргументу дизъюнкции (конъюнкции) ism + В переменных, либо ко всему аналитическому выражению функции, знак равенства удаляется, а перед символом функции и в конце всей системы ставится символ . Например,система функций YI Хз(х,Х2Ух,Х2); YZ (xiVx5)(x2Vx) будет представлена следующим образом Y,At(A2lA5)Y2V,V2, где Л| Xj; Л2 Aj V, X |Vx,; V2 XiV x. Записанная таким образом система функций кодируется позначно и вводится в блок 16 памяти. В первый блок 14 памяти вводится массив, отражающий временную диаграмму входных сигналов моделируемого автомата в виде меняющихся переменных х,, Х2, Xj. При моделировании конечного автомата без неисправностей в блок 14 памяти вводится единица в разряде А первого слова, а в блоке 16 памяти в разряде В будут нули. В начале моделирования счетчики 2 и 3 устанавливаются соответственно в состояния «О и «1, которые сохраняются до конца моделирования, т. е. до полного считывания блока 14 памяти. На выходе блока 4 сравнения будет нулевой сигнал, который запрещает моделирование неисправностей. Информация из блока 16 памяти будет считываться циклически, причем каждому циклу соответствует один набор входных сигналов, считываемых из блока 14 памяти. В каждом цикле считывания из блока 16 памяти будет вычисляться значение булевых функций,. После выполнения заданного числа циклов для каждого набора аргументов будет вычислен набор значений функций. Это происходит следующим образом. Первый выведенный из блока 14 памяти символ будет дешифрирован дешифратором 15, который подаст сигнал на блок 9 управления и элемент 8 задержки, с выхода которого задержанный сигнал разрешает запись в регистр 10 кода функций, следующего за знаком . Код функции будет дешифрирован дешифратором 11 и на вход синхронизации соответствующего разряда выходного регистра 12 будет подан единичный сигнал, т. е. будет выбрана вычисляемая функция. Следующая за знаком функции информация из поля С блока 16 памяти подается на дешифратор 15, который выделяет служебные символы 1;&-, (;);1;л; V, обеспечивающие выполнение функций, заданных в блоке 16 памяти. В блоке 16 памяти используется следующий формат слов. С выхода С считывается служебная информация, где символы Ли V указывают , что вычисляется значение конъюнкции (дизъюнкции) i m + Е переменных. С выхода А считывается сигнал, вызывающий инвертирование аргумента, поступающего через сумматор 7 по модулю два на вход блока 9. С выхода М считывается код маски, если на выходе С - символ Л или V и код инвертирования, записываемый в регистр 19, в противном случае, если с выхода С блока памяти 16 считывается символ Л(У), то на выходе блока 6 возникает нулевой сигнал, запрещающий запись информации в регистр 19. Таким образом, в регистр 19 фиксируется код, определяющий значения каких переменных должны инвертироваться при вычислении конъюнкции (дизъюнкции) i .$: гп + Е. переменных. С выхода X блока 14 памяти считываются значекия ш входных переменных, которые совместно с В внутренними переменными (выходными сигналами I элементов памяти автомата) с выхода регистра 12 через коммутатор 18 поступают на блок 20 сумматора по модулю два. Значения переменных, определенных кодом инвертирования, записанным в регистре 19, инвертируются. С выхода М блока 16 памяти считывается код маски. содержащии единицы в разрядах, соответствующих переменным, входящим в вычис-яемую конъюнкцию (дизъюнкцию) переменных. Маскирование осуществляется с помощью блока 21 элементов И при вычислении дизъюнкции переменных или блоком 25 элементов НЕ и блоком 24 элементов ИЛИ при вычислении конъюнкции переменных. Конъюнкция немаскированных перемен вычисляется с помощью элемента И 25 при подаче стробирующего сигнала Л с выхода дешифратора 15. С помощью элемента ИЛИ

22 вычисляется дизъюнкция немаскировочных переменных при подаче стробирующего сигнала V с выхода дешифратора 15 на вход блока элементов И 21. Вычисленное значение дизъюнкции (конъюнкции) через мультиплексор 5 и блок 6 поступает на вход сумматора по модулю два. Если с выхода А блока 16 памяти считывается единичный сигнал, то значение дизъюнкции (конъюнкции) инвертируется и поступает на вход блока 9, который использует это значение для вычисления функции в соответствии со служебной информацией, поступающей с выхода дешифратора 15.

При вычислении функций могут использоваться значения функций YI. Yz YKкоторые подключаются ко входу блока 9 через мультиплексор 5 аналогично значению вычисленной конъюнкции (дизъюнкции) с выхода элемента ИЛИ 26. Мультиплексор 5 подключается к выбранному входу под воздействием управляющего кода, поступающего с выхода С блока 16 памяти.

При считывании очередного символа на выходах блока 9 поступает вычисленное значение функции, которое записывается в выбранный разряд выходного регистра 12.

Задержанный блоком 8 задержки единичный сигнал разрешает запись в регистр 10 номера очередной функции и описанные действия повторяются до исчерпания списка функций. После этого из блока 14 памяти считывается очередной набор входных сигналов и цикл считывания из блока 16 памяти повторяется

В результате многократного вычисления функций на выходе регистра 12 формируется временная диаграмма выходных сигналов и состояний элементов памяти конечного автомата.

Моделирование неисправностей конечного автомата происходит следующим образом.

Блок 14 памяти выполняется так же, как при моделировании без неисправностей. В блок 16 памяти, кроме описания моделируемой схемы, вводится список неисправностей в виде единиц в разряде В. Первое считываемое слово блока 14 памяти установит счетчик 2 в состояние «О, а счетчик 3 отсчитает единицу в разряде блока 14 памяти. После этого начнется вывод информации из блока 16 памяти.

Первый единичный, сигнал, считанный с выхода В блока 16 памяти, увеличит на 1 содержимое счетчика 2 и на выходе блока 4 сравнения появится единичный сигнал. Если при этом с выхода С блока 16 памяти считан символ YJ , то на вход сумматора 7 по модулю два поступает значение константы со входа 27.

Если же считан символ , то блок 9 фиксирует на выходах значение константы со входа 27 и это значение записывается в регистр 12.

Моделирование неисправностей при выполнении конъюнкции (дизъюнкции) выполняется в том случае, если считывается символ Л (V) одновременно с единичным сигналом на выходе В блока 16 памяти. При этом на выходе блока 6 возникает единичный сигнал, запускающий блок 17 формирования кода неисправности, преобразующий код маски, поступающий на его вход с выхода М блока 16 памяти, в код, имеющий единичное значение только в одном разряде, определяющим переменную, значение которой должно быть заменено константой со входа 27. В соответствии с этим кодом коммутатор 18 выполняет необходимые переключения. Нулевой сигнал на втором выходе блока формирования кода неисправности блокирует приращение содержимого счетчика 3 через элемент И 1. Блокировка сохраняется до тех пор, пока не будет выполнено моделирование неисправностей, соответствующих всем переменным, входящим в конъюнкцию (дизъюнкцию) i $: гп + переменных. После этого на коммутатор 18 подается нулевой код, а блокировка приращения счетчика 3 снимается. Вычисление значения конъюнкции (дизъюнкции) переменных при моделировании неисправностей не отличается от описанного ранее.

Последовательное увеличение содержимого счетчика 3 и подсчет неисправностей счетчиком 2 в каждом цикле считывания блока 16 памяти позволяет моделировать все заданные неисправности. Таким образом, на выходах регистра 12 будут сформированы временные диаграммы при различных неисправностях. Эти временные диаграммы могут быть использованы для построения таблиц неисправностей, диагностических словарей или для проверки полноты тестов.

Таким образом, предлагаемое устройство для моделирования конечных автоматов выгодно отличается от прототипа высоким быстродействием и экономичностью блоков памяти.

Формула изобретения

1. Устройство для моделирования конечных автоматов, содержащее коммутатор, первый управляющий вход которого является входом устройства, первый и второй блоки памяти, первые входы которых подключены соответственно к первому и второму входам первого счетчика, выход которого соединен с первым входом блока сравнения, второй вход которого подключен к выходу второго счетчика, второй выход второго блока памяти соединен с первым входом сумматора по модулю два, выход которого подключен к первому входу блока управления, первый и второй выходы которого соединены соответственно с первым и вторым информационными входами первого регистра, группа выходов которого является группой выходов устройства и подключена к первой группе

входов мультиплексора, первый дешифратор, первый, второй, третий, четвертый, пятый и шестой выходы которого соединеиы соответственно с вторым, третьим, четвертым, пятым, шестым и седьмым входами блока управления, второй вход которого соединен с входом блока задержки, выход которого подключен к управляющему входу второго регистра, группа выходов которого соединена с группой входов второго дешифратора, группа выходов которого подключена к группе управляющих входов первого регистра, отличающееся тем, что, с целью повышения быстродействия, в него введены два элемента И, два элемента ИЛИ, блок элементов И, блок элементов ИЛИ, блок элементов НЕ, блок сумматоров по модулю два, третий регистр, блок выбора режима работы и блок формирования кода неисправности, причем третий выход второго блока памяти соединен с информационным входом второго регистра, с управляющим входом мультиплексора и с информационным входом первого дешифратора, седьмой н восьмой выходы которого подключены соответственно к первому н второму входам блока выбора режима работы и к первым входам первого элемента И и блока элементов И, группа выходов которого соединена с группой входов первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен со стробируюшнм входом мультиплексора, выход которого подключен к третьему входу блока выбора режима работы, четвертый вход которого соединен с выходом блока сравнения и подключен к десятому входу блока управления, одиннадцатый вход которого соединен с входом устройства и подключен к пятому входу блока выбора режима работы, первый выход которого соединен с вторым входом сумматора по модулю два, четвертый выход второго блока памяти соединен с входом блока элементов НЕ, с вторым входом блока элементов И, с информационным входом третьего регистра и с первым входом блока формирования кода неисправности, первый выход которого подключен к первому входу второго элемента И, второй вход которого соединен с первым выходом первого блока памяти, группа информационных выходов которого подключена к первой группе информационных входов коммутатора, вторая группа информационных входов которого соединена с группой выходов первого регистра, второй выход блока формирования кода неисправностей подключен к второму управляющему входу коммутатора, выход которого соединен с первым входом блока сумматоров по модулю два, выход которого подключен к третьему входу блока элементов И и к первому входу блока элементов ИЛИ, второй вход которого соединен с выходом блока элементов НЕ, группа выходов блока элементов ИЛИ подключена к группе входов

первого элемента И, второй и третий выходы блока выбора режима работы соединены соответственно с вторым входом блока формирования кода неисправности и управляющим входом третьего регистра, выход которого, подключен к второму входу блока сумматоров по модулю два.

2.Устройство по п. 1, отличающееся тем, что блок выбора режима работы содержит три элемента И, два элемента ИЛИ, элемент НЕ и элемент запрета, прямой вход которого является третьим входом блока, четвертый вход которого подключен к первым входам первого и второго элементов И, выход второго элемента И является вторым выходом блока, пятый вход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом первого элемента И и подключен к инверсному входу элемента запрета, выход которого подключен к первому входу первого элемента ИЛИ, выход которого является первым выходом блока, первый н второй входы которого соединены соответственно с первым и вторым входом второго элемента ИЛИ, выход которого подключен к второму входу второго элемента И н соединен с входом элемента НЕ, выход которого является третьим выходом блока и подключен к второму входу первого элемента И.

3.Устройство по п. 3, отличающееся тем, что блок управления содержит дешифратор, блок памяти, узел вычисления булевых функций, регистр, два элемента И-НЕ, Д-триггер н преобразователь параллельного кода в последовательно-параллельный, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого являются соответственно первым, десятым, восьмым, девятым, одиннадцатым, вторым, третьим и четвертым входами блока, пятый вход которого соединен с первым входом узла вычисления булевых функций, выход которого подключен к первому входу регистра, первый выход которого соединен с вторым входом узла вычисления булевых функций, третий вход которого подключен к первому выходу блока памяти, второй выход которого соединен с вторым входом регистра, второй выход которого подключен к информационному входу Д-триггера, управляющий вход которого соединен с третьим выходом блока памяти, четвертый выход которого подключен к девятому входу преобразователя параллельного кода в последовательQ но-параллёльный, выход которого соединен с входом дешнфратора, выход которого соединен с входом блока памяти, шестой и седьмой входы блока соединены соответственно с объединенными первым и вторым входами первого и второго элементов И-НЕ,

5 выходы которых подключены соответственно к первому и второму установочным входам Д-триггера, прямой и инверсный выходы которого являются соответственно первым

и вторым выходами блока, восьмой вход которого соединен с третьими входами первого и второго элементов И-НЕ.

4. Устройство по п. 1, отличающееся тем, что блок формирования кода неисправностей содержит три узла задержки, регистр, элемент И, преобразователь параллельного кода в . последовательно-параллельный и триггер, выход которого является первым выходом блока, первый вход которого подключен к первому входу элемента И, выход которого соединен с первым входом преобразователя параллельного кода в последовательно-параллельный, выход которого соединен с группой информационных входов регистра и является вторым выходом блока, второй вход которого соединен с вторым входом преобразователя параллельного кода

в последовательно-параллельный и с входами первого и второго узлов задержки, выходы которых подключены соответственно к первому входу триггера и к управляющему входу регистра, группа выходов которого

подключена к группе входов элемента И, второй выход преобразователя параллельного кода в последовательно-параллельный- с вторым входом триггера и с входом третьего узла задержки, выход которого соединен

с установочным входом регистра. Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 471587. кл. G Об F 15/20, 1973.

2.Авторское свидетельство СССР

№ 717775, кл. G 06 F 15/20, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Устройство для реализации булевых функций | 1982 |

|

SU1032451A1 |

| Устройство для моделирования конечных автоматов | 1977 |

|

SU717775A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для определения значений булевых функций | 1987 |

|

SU1508204A1 |

| Устройство для определения значений булевых функций | 1990 |

|

SU1805462A1 |

| Устройство для вычисления булевыхфуНКций | 1978 |

|

SU807272A1 |

| Устройство для вычисления булевых функций | 1984 |

|

SU1254462A1 |

| Устройство для вычисления булевых функций | 1982 |

|

SU1049898A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1444762A1 |

Фиг.

Авторы

Даты

1982-08-30—Публикация

1980-12-22—Подача