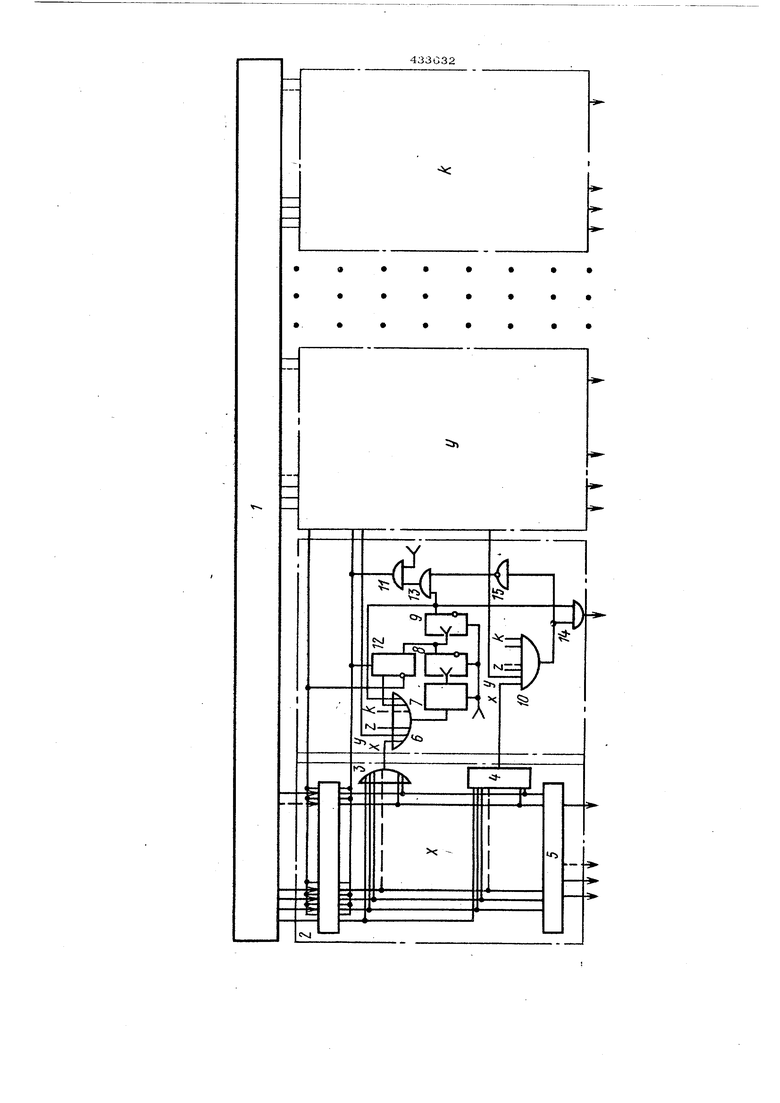

II (Обретение может эффективно исиользЬиги1)Сч в MHfjr()мерн1)1ч ана/шзагорах при ста1 iif.-iимсоком ана.чиче углоылх распределений ялериых части, а также при н.чмерении интенсивности нз. учен11Й во .многих точках иространсгва с помощью .многи.х детекторов. Мчвеслен нреобра.эователь, содержащий кодирующее устройство, выполненное в виде k-кo)pдlп anloй матрицы, в узлах которой расиоложемы датчики, адресный регистр и логический блок, состоящий из инвертора, дпзьюпкюров и конъюнкторов. Однако известное устройство сложно в поclpotHfui, полност1зЮ избавиться от появления ложиаЧ) адреса из-за влияния «резаных имну/и.сов. имеющихся при нендсальной работе .хемь определения этих импульсов, невозМГ)ЖН), Предложемнор устройство отличается от из.вестпмо тем, что, с иелыо упрощения устройства и исключения ложного адреса )И н.редаче инфо)маиии из-за влияния резан)1х имнульсов, вы.ходы координатной матриц) но каждой координате через адрес1И.Й регистр нодключеиы к соответствующим к;1ждой координате шифраторам, кроме I младшего разряда, дифференциальным дисмфиминаторам и дизъюнкторам, выходы дизъюнкторов соединены с общ-им дизъюикгором логического блока, уиравляющим генератором тактовы.ч и.мнульсов, выход последнего через первый триггер подключен ко входу BTopopfj триггера, инверсный выход которого соединен с унравляющп.ми входами адресного регистра, а )1еннверсцый выход с одним из входов общего дизъюнктора логического блока, н ко входу третьего триггера, выход которого соединен с одним из входов общего дизыонктора логического блока и с одними в.ходами дву.х конъюнкторов, вы.ход ifiepeoro из которькх через дизъюнктор соединен с входами установки «О адресного регистра и второго триггера, а второй вход второго конbK)HKTOj)a через нивертор иодключен ко второму входу первого ко1гыонктора и к выходу общего конъюнктора логического блока, входы кото1)ого соединены с выходами дифференциальны.к дискриминаторов каждой координаты. На чертеже представлена блок-схема предлагаемого устройства. Устройство состоит из кодирук)Н1его усгройства I, выполненного в виде /г- координатрк)11 матрицы, в узлах которой расположены датчики, адресного регистра 2, вход каждого риггера которого подключен к соответствующей шине соответствующей координаты, а выход каждого триггера соединяется с одним из входов дизъюнктора 3, с одним из входов дифференциального дискриминатора 4, функция которого заключается в обеспечении «I на выходе при появлении «1 только на одном из его входов и с одним из входов шифратора 5, исключая первый триггер, логического блока, состоящего из дизъюнктора 6, предназначенного для управления генератором 7 тактовых импульсов, счетных триггеров 8, 9 конъюнктора 10, входы которого соединены с выходами дифференциального дискриминатора 4 всех преобразователей координат, дизъюнктора 11, предназначенного для установки в «О триггеров адресного регистра 2 и триггера 12, конъюикторов 13, 14 и инвертора ;15.

Устройство работает следующим образом.

Прп возникновении имт1ульса в датчике появляются импульсы на одной из каждой координаты. Эти импульсы устанавливают в состояние «-I соответствующие триггеры адресного регистра 2. Информация по каждой координате считается правильной, если только один из триггеров этой координаты находится в состоянии «1. В этом случае на выходе дифференциального дискриминатора 4 появляется логическая «1. При случайном характере поступления входной информации во/можно появление и.мпульсов с двух или более датчиков одновременно, отсутствие импульса по какой-либо координате или неправильная установка триггеров адресного регистра в момент сов,падеция имнульса «конец регистрации с импульсами датчика. В этих случаях происходит установка в «1 более чем одного триггера, хотя бы по одной координате, или возможен случай, когда ни один из триггеров не устанотпся в «I. При этом па выходе дифференциального дискриминатора 4 остается «О.

В любом случае, даже если информация нсказптся так, что установится в «1 только один из триггеров адресного регистра 2, на выходе дизъюнктора 3 хотя бы одной из координат появляется «I. Появлен ие «1 на входе дизъюнктора б -при наличии «I на входе «Внешняя блокнровка приводит к тому, что начинает работать генератор тактовых импульсов 7. Длительность импульсов Т„ генератора 7 устанавливается равной максимально возможному времени задержки прихода импульса по одной координате относительно прихода импульса по другой коордпнате, так как по заднему фронту первого импульса устанавливается в «I триггер 12, блокируя входы триггеров адресного регистра 2. Максимальное время установления уровня на выхояекоиьюнктора 1О определяет лериод Тг следования импульсов с генератора тактовых импульсов 7, так как через время Т:,+Тг на входе конъюнктора 14 появляется импульс с триггера 9, образуя на выходе импульс «конец преобразования, если па -всех входах копъюнктора 10 присутствуют «1. Импульс «конец преобразования является им пульсом разрещения д.тя регистрации двоичного кода, .получаемого на выходе шифратора 5 каждой координаты.

В момент репистрации на вход «внеш няя блокировка подается логический «О, устанавливающий в исходное состояние триггеры 8, 9.

Установка триггеров адресного регистра 2 и триггера 12 в исходное состояние производится 110 акоичанин регистрации импульсом

«конец регистрации.

Если инфор1мация, гпостулающая на триггеры адресного регистра, неправильпая, то «1 присутствует не ,па всех входах конъюнктора 10. На выходе инвертора 15 при этом присутствует «1 и при 1появлеп.йи импульса

с триггера 9 на выходе конъюнктогра М появляется импульс установки адресного регистра 1 п триггера 12в исходное положение. Для того чтобы с триггера 9 выдавался полноценный ,по дл1ительпасти импульс, с его вы.хода на вход дизъюнктора 6 заведена обратная связь, благодаря которой поддерживается уровень «1 на входе генератора тактовых импульсов 7, разрешая его работу до тех пор, (ПОка уровень на выходе триггера 9 не станет «О.

Помехозащищенность схемы обеспечена тем, что при взведении любого триггера адресного регистра 2 пли триггера 12 от помехи наЧ|Инает работать генератор 7, и импульс Tpnrreipa 9 /производит устаноаку триггеров адресного регистра 2 в исходное состояние.

Так как проверка ипфор.мации осуществляется на адресном регистре и проверяется ее правильность через время Тн+Г,., равное времени окопчапия переходных процессов, то iiMefUio этим исключается передача ложной информации, получающаяся в момент совпадения пм.пульса «конец регистрации с входными импульсами.

Схема входного устройства -преобразователя может быть легко реализовапа на потанцпальпых логических элемен1ах.

Il р е д м е т изобретения

Преобразователь номера датчика в цифровой код, содержащий кодирующее устройство,

вьиюлненпое в виде ft-координатной матрицы, в узлах которой рас.положепы датчики, адресный регистр -и логичеекпй блок, состоящий из |ИП1зертора, дпзъюнкторов и конъюнкторов, отличающийся тем, что, с целью упрощения устройства и исключения ложного адреса При передаче инфор.мации из-за влияния «резаных им1пульсов, выходь координатной матрицы по каждой координате через адресный регистр подключены к соответствующим каждой координате шифраторам,

кроме младшего разряда, дифференциальным дискриминаторо.м и дизъюнкторам, выходы дизъюнкторов соединены с общим дизъюнктором логического блока, управляющим генератором тактовых импульсов, выход последнего через первый триггер подключен ко

входу второго триггера, инверсный выход коToporo соединен с управляющими входами адресного регистра, а нешшерсный выход - с одним iu входов общего дизъюнктора логического блока, и ко входу третьего триггера, выход которого соединен с одним из входов общего диэъювктора логического блока и с одними входа.ми двух ко гыонкторов, выход первого из KOTopvK через дизъюнктор

соединен с входами установки О адресного регистра и второго триггера, а второй вход через инвертор подключен ко второму входу дизъкшктора и к выходу общего конъкиктора логического блока, входы которого соединены с выхода.«1 дифференциальных дискрим шаторов каждой координаты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая система измерения глубинного положения морской пьезосейсмографной косы | 1976 |

|

SU894640A1 |

| УСТРОЙСТВО ДЛЯ СОРТИРОВКИ ДВУМЕРНОГО МАССИВА ДАННЫХ (ВАРИАНТЫ) | 2003 |

|

RU2252447C2 |

| СПОСОБ АДАПТИВНОЙ АДРЕСНОЙ СИГНАЛИЗАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2209468C2 |

| ИМИТАТОР УГЛА ПОВОРОТА АНТЕННЫ РЛС | 1987 |

|

SU1841003A1 |

| СПОСОБ УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЕМ ТРЕХФАЗНОГО НАПРЯЖЕНИЯ В ВЫСОКОЧАСТОТНОЕ ОДНОФАЗНОЕ И УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2007 |

|

RU2337462C1 |

| Устройство для измерения угловых перемещений | 1986 |

|

SU1392350A1 |

| Устройство для психологических исследований | 1989 |

|

SU1621883A1 |

| Устройство для измерения геометрических размеров движущихся объектов | 1982 |

|

SU1037064A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| Устройство для контроля скорости изменения частоты | 1979 |

|

SU885884A2 |

Авторы

Даты

1974-06-25—Публикация

1972-10-17—Подача