Изобретение относится к измерительной техники и может быть использовано в устройствах обнаружения и оценки параметров периодических импульсных сигналов в условиях наличия аддитивного шума и импульсных помех, а также при неизвестном периоде повторения импульсов, например, в радиоастрономии, радиофизике и других областях науки и техники, использующих периодические процессы, а также при анализе временных рядов.

Целью изобретения является повышение достоверности обнаружения периодических импульсных последовательностей при неизвестном периоде повторения импульсов и увеличение быстродействия.

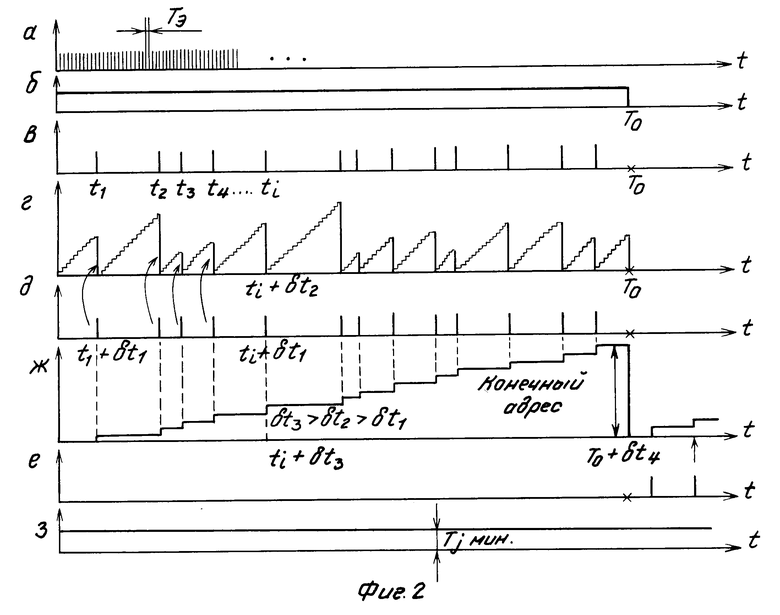

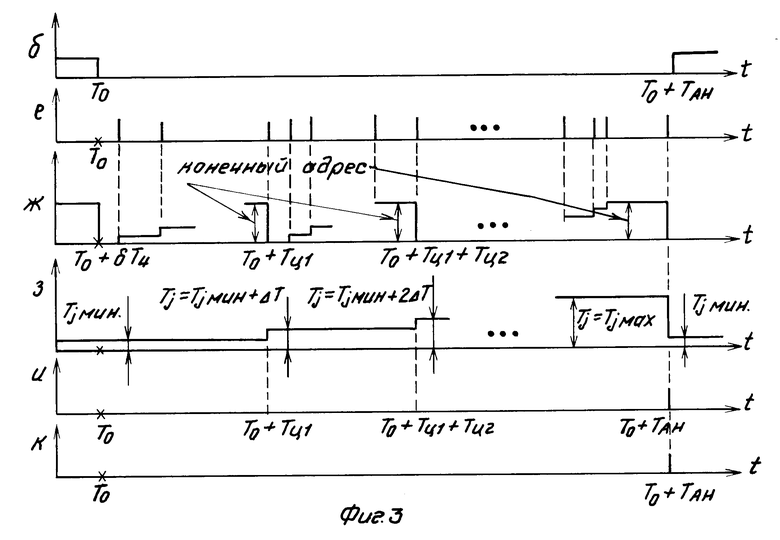

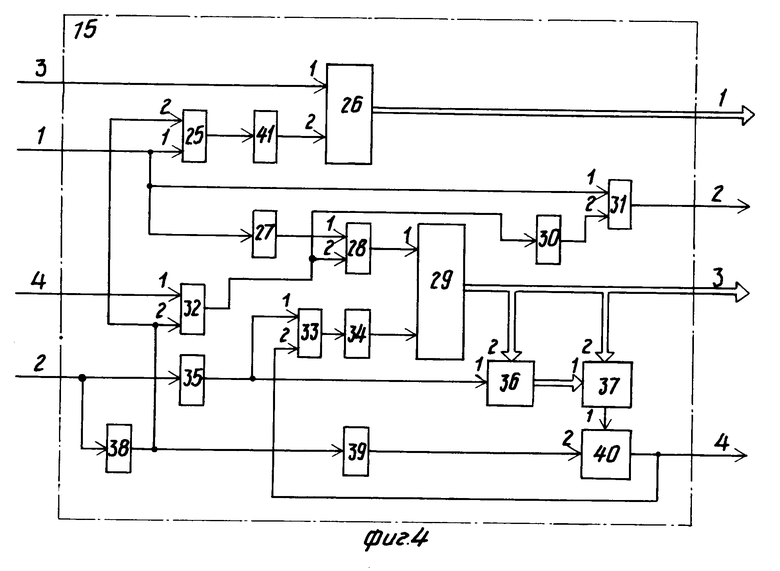

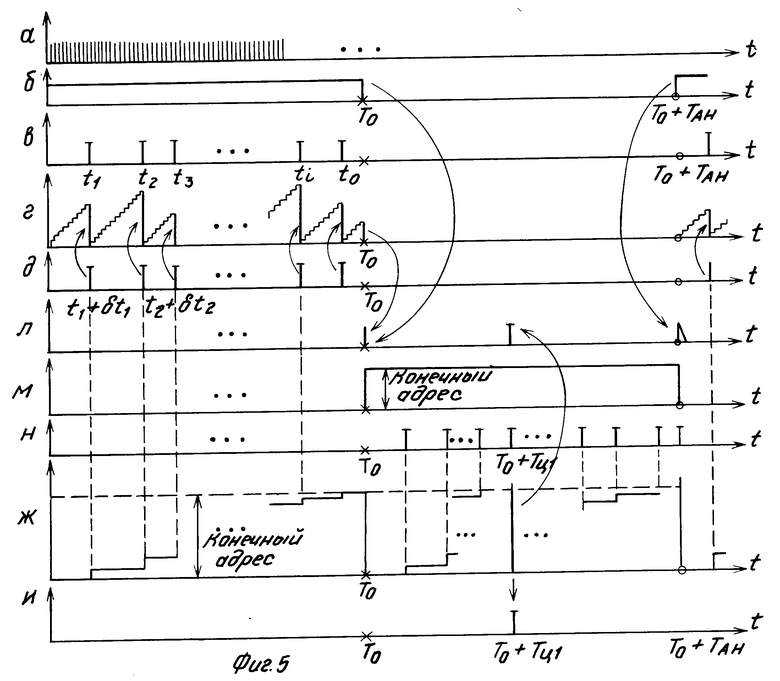

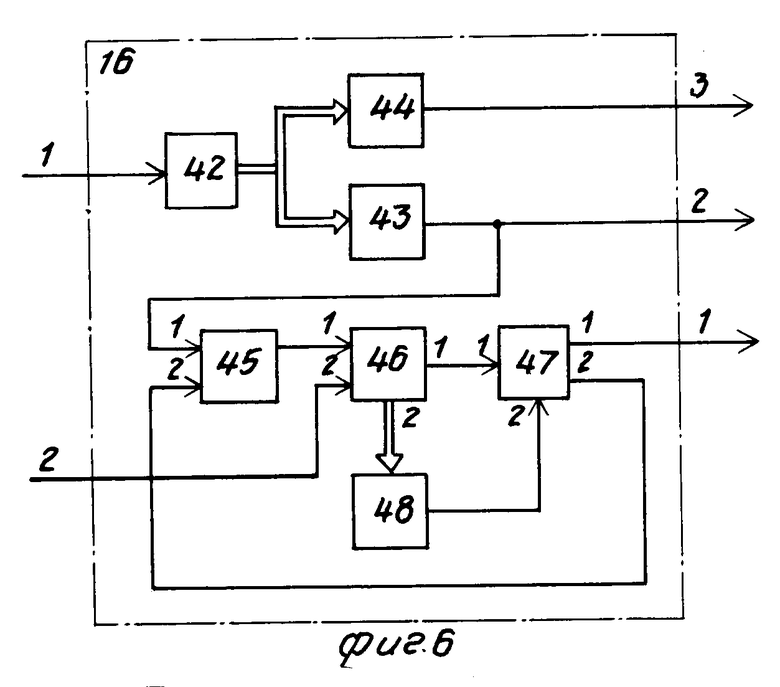

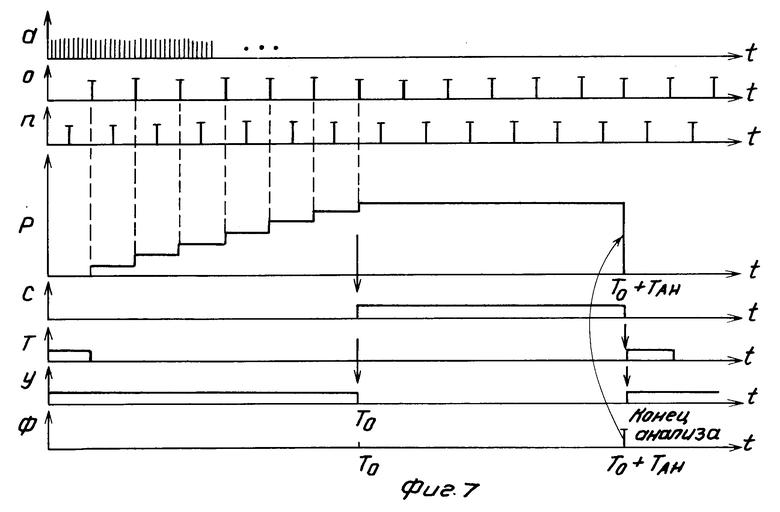

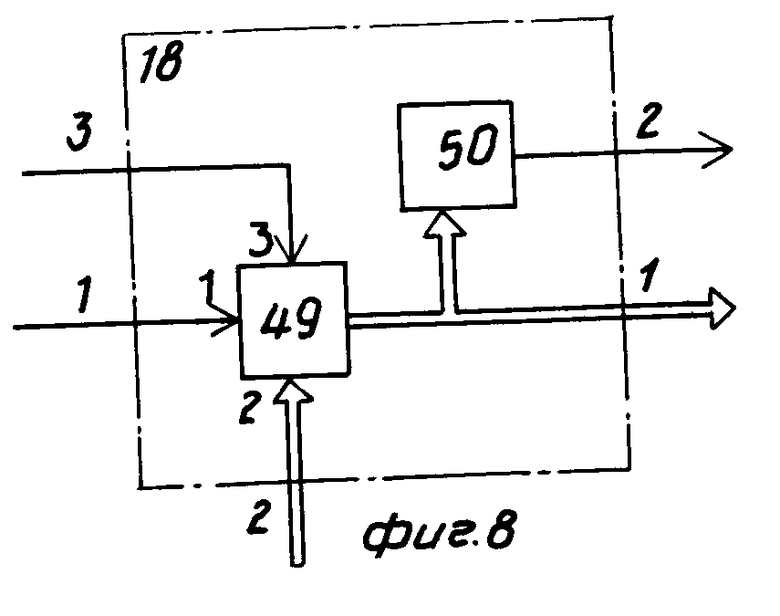

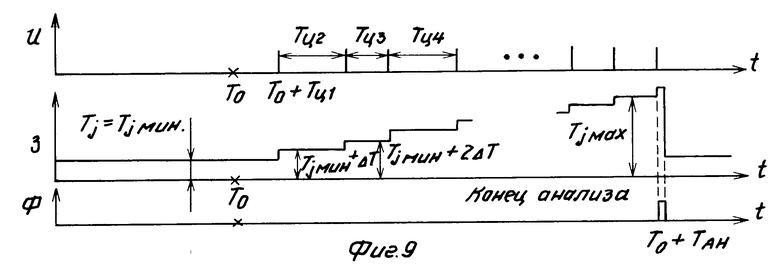

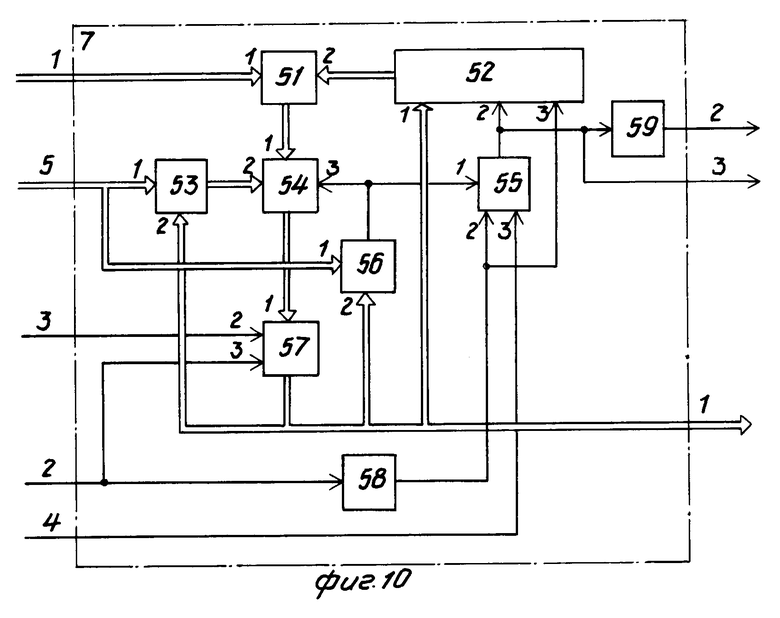

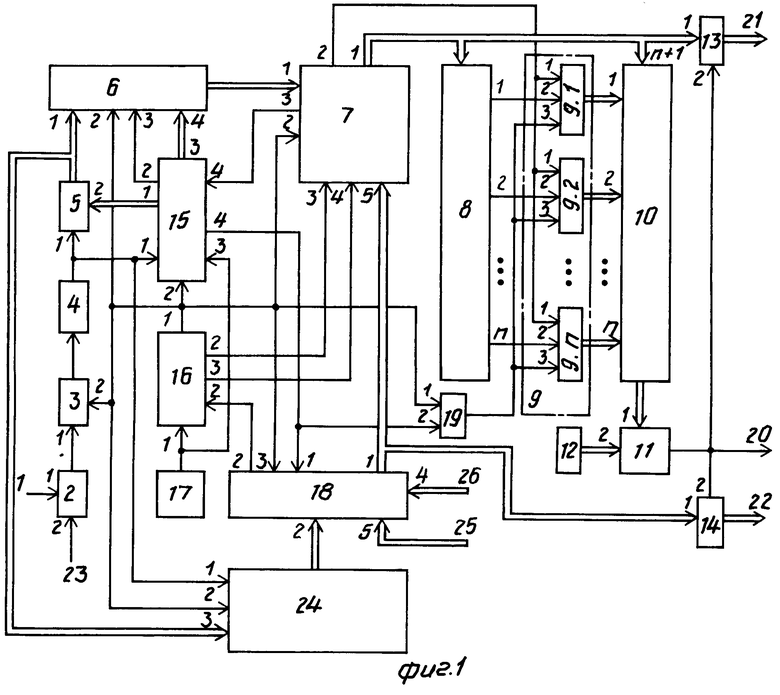

На фиг.1 представлена функциональная схема устройства; на фиг.2 показаны временные диаграммы процессов в устройстве на первом этапе его работы (этапе накопления массива временных интервалов); на фиг.3 временные диаграммы процессов в устройстве на втором этапе его работы (этапе анализа накопленного массива временных интервалов); на фиг.4 представлена функциональная схема блока управления; на фиг.5 показаны временные диаграммы процессов, происходящих в блоке управления; на фиг.6 представлена функциональная схема синхронизатора; на фиг.7 показаны временные диаграммы процессов, происходящих в синхронизаторе; на фиг. 8 представлена функциональная схема блока задания модуля; на фиг. 9 показаны временные диаграммы процессов, происходящих в блоке задания модулей; на фиг.10 представлена фунциональная схема модульного преобразователя.

Устройство (фиг.1) имеет входную шину 1, квантователь 2, блок 3 стробирования, формирователь 4 импульсов, ключ 5 интервала, блок 6 памяти, модульный преобразователь 7, дешифратор 8, счетчики 9,1.9.n, мультиплексор 10, пороговый блок 11, блок 12 задания порога, ключ 13 вычета, ключ 14 модуля, блок 15 управления, синхронизатор 16, генератор 17 тактовых импульсов, блок 18 задания модуля, блок ИЛИ 19, шину 20 обнаружения, шину 21 вычета, шину 22 модуля, шину 23 порога квантования и шину 24 минимального модуля.

Работает устройство следующим образом.

Сигнал по входной шине 1 поступает на первый вход квантователя 2, где подвергается бинарному квантованию путем сравнения с пороговым напряжением, подавае- мым на второй вход квантователя по шине 23. С выхода квантователя квантованный по амплитуде сигнал поступает на первый вход блока 3 стробирования, который пропускает через себя сигнал в течение определенного времени То, называемого стробом анализа, который генерируется на первом выходе синхронизатора 16. Этот интервал времени определяет первый этап работы устройства. Он заключается в накоплении в блоке 6 памяти массива интервалов t(i-1),i} между импульсами во входном потоке в пределах интервала анализа То.

В пределах интервала То (фиг. 2), определяемого длительностью строба анализа на первом выходе синхронизатора (первый этап работы), блоки, начиная с преобразователя 7 и кончая ключом 14, а также дешифтор 8 находятся в исходном состоянии и участия в работе устройства не принимают, так как строб анализа на втором входе модульного преобразователя 7 удерживает его узлы в исходном состоянии, поэтому на его первом выходе действует нулевой двоичный код, импульсы на втором и третьем выходах отсутствуют.

Отсутствуют также управляющие импульсы на первом входе блока 18 задания модуля с четвертого выхода блока 15 управления. Поэтому на его первом выходе установлен код Tj Tjmin, а на втором выходе импульсы, подаваемые на второй вход синхронизатора 16, также отсутствуют. Счетчики (9.1.9.n) установлены в нулевое состояние стробом анализа через блок ИЛИ 19.

На фиг.2 а импульсы на выходе генератора 17 тактовых импульсов; б строб анализа на первом выходе синхронизатора 16, в анализируемая последовательность импульсов на первом входе ключа 5 интервала, г двоичный код на втором входе ключа 5 интервала с первого выхода блока управления, д последовательность импульсов записи временных интервалов в блок 6 памяти на его третьем входе; е импульсы с третьего выхода модульного преобразователя 7, определяющие работу счетчика адреса на втором этапе работе устройства этапе анализа (даны здесь для связи временных диаграмм с этапом анализа), ж изменение адреса ячейки блока 5 памяти на его четвертом входе, з двоичный код Tjmin на первом выходе блока 18 задания модуля.

Квантованный сигнал, стробированный стробом анализа в блоке 3, поступает на вход формирователя 4 импульсов, где преобразуется в последовательность коротких импульсов одинаковой длительности и амплитуды (фиг.2в), моменты появления которых с точностью до времени задержки в квантователе 2, блоке 3 и формирователе 4 совпадают с положением передних фронтов входных импульсов. Каждый из выходных импульсов формирователя 4 в момент их появления на входе ключа 5 интервала открывает его и пропускает с его второго входа на выход и далее на информационный (первый) вход блока 6 памяти код временного интервала, который сформирован счетчиком временного интервала (фиг.2г), входящим в состав блока управления. Этим же импульсом счетчик временного интервала сбрасывается в ноль и начинает отсчет нового временного интервала с тактом Тз, определяемым частотой следования импульсов с выхода генератора 17 тактовых импульсов (фиг.2а).

Сигнальные импульсы, поступающие на первый вход блока 15 управления, также используются для изменения адреса (двоичного кода на третьем выходе блока 15 управления, фиг.2ж, подаваемого на четвертый адресный вход блока 6 памяти. В момент начала работы на этом входе присутствует адрес нулевой ячейки блока 6 памяти и первый сигнальный импульс записывает в эту ячейку двоичный код интервала между началом строба анализа и моментом появления этого импульса. Этот импульс после записи информации в нулевую ячейку наращивает на единицу содержимое счетчика адреса в блоке 15, и таким образом подготавливает блок памяти к записи следующего временного интервала между первым и вторым входными импульсами в первую ячейку и т.д. в результате чего к моменту окончания интервала анализа в последовательно расположенные по адресам ячейки памяти, начиная с нулевой, записаны значения всех временных интервалов между импульсами в анализируемой реализации.

Вследствие наличия в составе входного потока импульсов помех и неизвестности периода повторения импульсов в сигнальной компоненте число занятых ячеек блока 6 будет случайным. На основании априорных знаний статиcтических характеристик входного потока импульсов выбирается необходимый полный объем памяти, обеспечивающий допустимо малую вероятность его переполнения.

В составе блока 15 управления есть специальный регистр конечного адреса, который предназначен для сохранения на втором этапе работы устройства (этапы анализа) конечного адреса массива исходных данныхt(i-1),i} хранимых в блоке 6, конечный адрес необходим для многократного использования массива при анализе. На этапе анализа данные извлекаются поочередно из блока 6 памяти. Режимы работы блока 6 запись-чтение определяются стробом анализа, подаваемым на его второй вход (в пределах строба анализа запись, за его пределами чтение).

В момент окончания строба анализа завершается первый этап работы устройства, и оно переходит к второму этапу этапу анализа накопленного массива временных интерваловt(i-1),i} с последующим накоплением одинаковых значений вычетов в счетчиках (9.1.9.n), а также решением задачи обнаружения (порогового испытания) в пороговом блоке с выдачей на выходные шины 20, 21 и 22 соответствующих обнаруженному сигналу признака обнаружения (логическая "1" на шине 20) и двоичных кодов временного положения и периода повторения.

Анализ массиваt(i-1),i} циклически повторяется, начиная с минимального значения пробного периода Tj Тjmin, и наращиванием Tj в каждом цикле на Δ Т завершается циклом, в котором Tj Tjmаx. При этом завершается этап анализа, блок управления формирует новый строб анализа То и устройство переходит к обработке новой реализации входного потока импульсов.

Каждый цикл анализа (при конкретном одном значении пробного периода Tj) завершается сбросом счетчика адреса в блоке управления в нулевое состояние и сбросом счетчиков (9.1.9.n), таким образом анализирующая часть устройства подготавливается к началу анализа в каждом цикле.

Диаграмма и на фиг.3 представляет собой последовательность импульсов на четвертом выходе блока 15 управления. Импульсы на этом выходе появляются только на этапе анализа. Они соответствуют моментам, когда завершается каждый цикл анализа, т.е. когда завершается перебор адресов массиваt(i-1),i} и содержимое счетчика адреса в блоке 15 превышает значение конечного адреса этого массива, хранимого в регистре конечного адреса блока 15. Импульсы с четвертого выхода блока 15 используются для приведения счетчиков 9.1.9.n в исходную готовность к накоплению в новом цикле анализа, а также наращивают в блоке 18 задания модуля пробный период Tj на Δ Т для нового цикла анализа (фиг.3з).

Итак, в момент окончания строба анализа (фиг.3б) блок 6 памяти переводится в режим считывания, счетчик адреса в блоке 15 управления устанавливается в нулевое состояние, а модульный преобразователь 7, блок 18 задания модуля и счетчики 9.1.9.n переводятся в рабочее состояние снятием с указанных выше входов этих блоков строба анализа. При этом на пятый вход модульного преобразователя 7 от блока 18 задания модуля подается минимальное значение пробного периода Tj Tjmin (фиг.3з). Счетчик адреса в блоке 15 управляется уже не импульсами сигнала (их на первом входе блока 15 в режиме анализа нет), а импульсами с третьего выхода модульного преобразователя 7 (фиг.3е). Эти импульсы образуются в момент окончания очередного модульного преобразования вычисления очередного значения вычета Δ tij. Такая организация управления счетчиком адреса необходима вследствие того, что время, требуемое на вычисление каждого вычета Δ tij, не остается неизменным, поэтому только после завершения вычислительных операций в модульном преобразователе 7 дается команда на изменение адреса и извлечение из блока 6 памяти нового значения временного интервала t(i-1),i. На фиг.3е показаны импульсы, соответствующие моментам переключения счетчика адреса, а на фиг.3ж изменения состояния счетчика адреса. В момент То+Тц1 завершается преобразование массива временных интерваловt(i-1),i} по модулю Tj=Tjmin и начинается его преобразование по модулю Tj (Tjmin + Δ T), которое завершается в момент To + Tц1 + Тц2 (фиг. 3з), где Тц1 длительность первого цикла преобразования, Тц2- длительность второго цикла преорбразования и т.д. Каждый цикл завершается в момент, когда содержимое счетчика адреса достигает конечного значения. В конце каждого цикла преобразования импульсом с четвертого выхода блока 15 управления (фиг. 3и) наращивается на первом выходе блока 18 задания модуля значения пробного периода Tj на Δ Т. Признаком завершения второго этапа работы устройства является достжение пробным периодом своего максимального значения Tj Tjmax. Этот момент фиксируется коротким импульсом на втором выходе блока 18 задания модуля (фиг.3к), который, поступая на второй вход синхронизатора, задает ему момент начала формирования нового строба анализа, по которому описанный выше процесс повторяется. Одновременно с преобразованием в пределах каждого цикла осуществляются сортировка вычетов по численному значению и подсчет числа одинаковых вычеов каждого из возможных значений.

Каждому интервалу t(i-1),i соответствует "свой" вычет Δ tij, двоичный код которого появляется на первом выходе модульного преобразователя 7. В момент завершения формирования этого двоичного кода дешифратор 8 открывает вход записи "1" в соответствующий по номеру счетчик (9.1.9.n). Так, если вычет Δ tij 0, то на первом выходе дешифтора 8 появляется уровень логической "1", который, поступая на второй вход счетчика 9.1, подготавливает его к записи (добавлению) единицы к содержимому счетчика. Если вычет Δ tij 1, то единица добавляется к содержимому счетчика 9.2, при Δ tij 2 к содержимому счетчика 9.3 и т. д. Одновременно с этим код вычета Δ tij, поступая на (n+1)-й вход (вход управления) мультиплексора 10, подключает выход соответствующего счетчика к входу порогового блока 11, где происходит сравнение текущего значения содержимого счетчика с порогом обнаружения Nпор. В случае его превышения на выходе порогового блока 11 появляется уровень логической "1", свидетельствующий об обнаружении периодической последовательности, который открывает по вторым входам ключи вычета 13 и модуля 14, на выходах которых соответственно на шинах 21 и 22 вычета и модуля появляются двоичные коды оценок временного положения обнаруженной последовательности (вычет) и периода следования импульсов (модуль преобразования пробный период Тj). Момент записи единицы в счетчики определяется моментом стабилизации значения двоичного кода вычета на первом выходе модульного преобразователя. В этот момент на его втором выходе появляется короткий импульс, поступающий на соединенные между собой первые (тактовые) входы счетчиков 9.1.9.n. В результате этого возрастает на единицу содержимое того счетчика, на второй вход которого с одного из выходов дешифратора 8 подается уровень логической "1".

Блок 15 управления формирует сигналы, координирующие взаимодействие всех блоков устройства. Он (фиг.4) состоит из первого дизъюнктора 25, счетчика 26 временного интервала, первого элемента 27 задержки, второго дизъюнктора 28, счетчика 29 адреса, второго элемента 30 задержки, третьего дизъюнктора 31, первого конъюнктора 32, четвертого дизъюнктора 33, третьего элемента 34 задержки, блока 35 выделения фронтов, регистра 36 конечного адреса, первого компаратора 37, инвертора 38, четвертого элемента 39 задержки, второго конъюнктора 40 и пятого элемента 41 задержки.

Работает блок управления следующим образом. На первом этапе работы устройства на второй вход блока управления поступает строб анализа (фиг.5б). При этом инвертированный инвертором 38 строб анализа запирает первый конъюнктор 32, поступая на его второй вход, и второй конъюнктор 40, поступая на его второй вход через четвертый элемент 39 задержки. Вместе с этим на выходе блока 35 выделения фронтов формируются короткие импульсы, соответствующие по временному положению переднему и заднему фронтам строба анализа (фиг.5л), которые, объединяясь с импульсами с выхода второго конъюнктора 40 в четвертом дизъюнкторе 33, через третий элемент 34 задержки поступают на второй вход (вход сброса) счетчика 29 адреса (фиг.5л). Таким образом, в начале и в конце первого этапа работы устройства счетчик 29 обнуляется (фиг.5ж).

Эталонная последовательность импульсов с выходе генератора тактовых импульсов (фиг.5а) поступает на третий вход блока управления и далее на первый вход счетчика 26 временного интервала. Каждый импульс увеличивает содержимое этого счетчика на единицу (фиг.5г). Период следования Тэ в эталонной последовательности импульсов определяет дискретность измерения временных интервалов Δ Т Тэ. Счетчик 26 к моменту начала строба анализа установлен в нулевое состояние предшествующим этому моменту напряжением с выхода инвертора 38 через первый дизъюнктор 25 и элемент 41 задержки на второй вход счетчика, являющийся входом установки нуля. Таким образом, счетчик сразу начинает отсчитывать (фиг. 5г) интервал между началом строба анализа и первым импульсом анализируемой последовательности (фиг.5в), который, как и последующие, поступает на первый вход блока 15 управления и далее через третий дизъюнктор 31 на второй выход блока 15, с которого поступает на блок 6 памяти в качестве тактового для записи значения временного интервала. Этот же импульс через первый дизъюнктор 25 и пятый элемент 41 задержки поступает на второй вход счетчика 26 временного интервала (фиг.5д) для его сброса и подготовки к отсчету следующего временного интервала. Задержка в элементе 41 необходима для того, чтобы сброс счетчика 26 происходил после записи его содержимого в блок 6 памяти.

Таким образом, к моменту появления очередного импульса на первом входе блока 15 (фиг.5в) на его первом выходе (выход счетчика 26 временного интервала) формируется двоичный код временного интервала (фиг.5г), который записывается в блок 6 памяти по адресу, подготовленному к этому моменту в счетчике 29 (фиг. 5ж). Через некоторый интервал времени, определяемый временем записи информации в блок 6, этот импульс наращивает адрес в счетчике 26 на единицу, подготавливая адрес следующей ячейки памяти для записи туда следующего значения временного интервала. Этот процесс обеспечивается тем же сигнальным импульсом, проходящим с первого входа блока 15 через первый элемент 27 задержки и второй дизъюнктор 28 на первый вход счетчика 29 адреса. Так обеспечиваются автоматическое наращивание адреса и запись значений временных интервалов в последова- тельно расположенные ячейки блока памяти, начиная с нулевого.

К моменту окончания строба анализа в счетчике 29 адреса устанавливается максимальное значение адреса, численно равное числу временных интервалов между импульсами в анализируемой реализации. Этот адрес импульсом с выхода блока 35 выделения фронтов записывается в регистр 36 конечного результата (фиг. 5м) для дальнейшего использования на втором этапе работы устройства. К моменту окончания строба анализа счетчик 26 временного интервала устанавливается в нулевое состояние напряжением с выхода инвертора 38 и во время второго этапа работы не меняет этого состояния (фиг.5г).

На втором этапе происходит считывание и обработка информации, накопленной в блоке 6 памяти за время первого этапа. При этом открываются конъюнкторы 32, 40, причем второй конъюнктор открывается с небольшим запаздыванием, определяемым четвертым элементом 39 задержки, необходимым для компенсации времени задержки изменения состояния регистра конечного адреса относительно конца строба анализа, возникающей вследствие аппаратурной задержки в блоке 35, регистре 36, компараторе 37. Счетчик 29 адреса обнуляется импульсом с выхода блока 35 выделения фронтов через четвертый дизъюнктор 33 и третий элемент 34 задержки. Таким образом, к началу второго этапа работы устройства на шине адреса блока памяти (выход счетчика 29 адреса) действует код нулевого адреса. На этом этапе сигнальные импульсы на первый вход блока 15 управления не поступают. Теперь на первый вход счетчика 29 адреса поступают импульсы, формируемые в модульном преобразователе 7 на его третьем выходе. Эти импульсы поступают на четвертый вход блока 15 управления, затем через открытый первый конъюктор 32 и второй дизъюнктор 28 поступают на счетный (первый) вход счетчика 29 адреса (фиг.5н). Каждый из этих импульсов (фиг.5н) формируется в момент окончания вычисления вычета. Эти импульсы с выхода первого конъюнктора 32 через второй элемент 30 задержки и третий дизъюнктор 31 поступают на второй выход блока 15 управления, являясь тактовыми для блока 6 памяти при считывании. Поскольку в этом режиме работы блока 6 памяти считыванию информации предшествует установление адреса ячейки памяти, импульс на втором выходе блока 15 управления задержан во втором элементе 30 задержки относительно момента переключения адреса. Таким образом, осуществляются последовательное считывание из блока 6 памяти временных интервалов t(i-1),i и формирование значений соответствующих вычетов Δ tij в модульном преобразователе 7. Процесс наращивания адреса в счетчике 29 адреса происходит до тех пор, пока его значение не превысит величины конечного адреса, хранимого на протяжении всего второго этапа работы в регистре 36 конечного адреса (фиг. 5м). Момент наступления этого события фиксируется появлением на выходе компаратора 37 уровня логической "1", который через открытый второй конъюнктор 40, четвертый дизъюнктор 33 и третий элемент 34 задержки поступает на второй вход счетчика 29 адреса и обнуляет его (фиг.5ж). Адрес на третьем выходе блока управления становится равным нулю. На этом завершается первый цикл работы и начинается следующий. Сброс счетчика 29 адреса в нулевое состояние приводит к изменению соотношения кодов на входах компаратора 37, в результате чего на его выходе появляется уровень логического "0".

Таким образом, в конце каждого цикла работы на выходе компаратора 37 формируется импульс (фиг.5и) "Конец цикла", длительность которого равна времени задержки распространения сигнала в цепи конъюнктора 40, дизъюнктора 33, элемента 34, счетчика 29. Этот импульс поступает на четвертый выход блока 15 управления и далее через блок ИЛИ 19 сбрасывает содержимое счетчиков 9.1.9. n, подготавливая их к работе в новом цикле, а также поступает на первый вход блока 18 задания модуля, где наращивает текущее значение пробного периода Tj на Δ Т. Последующие циклы второго этапа работы устройства подобны описанному.

Завершается второй этап в момент, когда в блоке 18 задания модуля текущее значение пробного периода достигает максимума Tj Tjmax, что приводит к формированию синхронизатором 16 нового строба анализа, поступающего на второй вход блока 15 управления. В результате работа этого блока вновь повторяется с первого этапа так, как это описано выше.

Синхронизатор 16 (фиг.6) вырабатывает строб анализа, а также последовательности нечетных "Такт 1" и четных "Такт 2" тактовых импульсов, используемых в работе модульного преобразователя 18. Он содержит счетчик 42 тактов, дешифратор 43 нечетного такта, дешифратор 44 четного такта, третий конъюнктор 45, счетчик 46 строба, RS-триггер 47 и дешифратор 48 строба. Первый вход синхронизатора 16 является входом счетчика 42 тактов, а его выход соединен с входом дешифратора 44 четного такта, выход которого является третьим выходом синхронизатора 16 и входом дешифратора 43 нечетного такта. Выход последнего является вторым выходом синхронизатора 16, соединенным с первым входом третьего конъюнктора 45, выход которого соединен с первым входом счетчика 46 строба. Второй вход счетчика 46 является вторым входом синхронизатора 16, первый выход соединен с первым входом RS-триггера 47, а второй выход с входом дешифратора 48 строба, выход которого соединен с вторым входом RS-триггера 47, первый выход которого является первым выходом синхронизатора 16, а второй выход соединен с вторым входом третьего конъюнктора 45.

Работает синхронизатор 16 следующим образом. На первый вход синхронизатора поступает эталонная последовательность импульсов с выхода генератора 17 тактовых импульсов. Эти импульсы поступают на вход счетчика 42 тактов (фиг. 7а), который работает в режиме непрерывного счета и осуществляет деление частоты эталонной последовательности импульсов в Кэ раз, где коэффициент пересчета Кэ определяется требуемым периодом следования последовательностей "Такт 1" и "Такт 2", зависящим от длительности переходных процессов в модульном преобразователе 7. С помощью дешифраторов 44 и 43 четного и нечетного тактов формируются две последовательности импульсов на их выходах, сдвинутые одна относительно другой на некоторый интервал времени, не превышающий половины периода повторения этих импульсов (фиг.7о.п). Величина этого сдвига определяется переходными процессами в модульном преобразователе 7, для нормальной работы которого формируются эти последовательноти. Они формируются непрерывно как на первом, так и на втором этапах работы устройства. Нечетная тактовая последовательность "Такт 1" с выхода дешифратора 43 нечетного такта поступает на первый вход третьего конъюнктора 45.

На первом этапе работы устройства, когда синхронизатор 16 формирует строб анализа на первом выходе RS-триггера 47 (фиг.7у), взведенного в единичное состояние сигналом нулевого содержимого счетчика 46 строба (фиг.7т) на первом входе RS-триггера 47, счетчик работает в режиме счета, так как потенциал, подаваемый с второго выхода RS-триггера 47 на второй вход третьего конъюнктора 45, держит его в открытом состоянии, и импульсы "Такт 1" через конъюнктор 45 поступают на счетный (первый) вход счетчика 46. В момент, когда в счетчике устанавливается число, равное То/Тт, где Тт период следования импульсов "Такт 1" (Тт Тз ˙ Кэ), на выходе дешифратора 48 строба появляется потенциал (фиг.7с), который, поступая на второй вход RS-триггера 47, переводит его в нулевое состояние. Этот момент соответствует окончанию строба анализа и завершению первого этапа работы устройства. При этом потенциал с второго выхода RS-триггера 47 запирает третий конъюнктор 45 и поступление импульсов "Такт 1" на счетный вход счетчика 46 строба прекращается. Счетчик 46 останавливается.

Таким образом, заданный фронт строба анализа совпадает с моментом появления импульса "Такт 1". Начинается второй этап работы устройства, длительность которого случайна из-за случайности размера и состава массива обрабатываемых временных интерваловt(i-1),i} Поэтому начало формирования очередного строба анализа определяется моментом завершения второго этапа, когда Тj превосходит значение Тjmax, что фиксируется появлением импульса на втором выходе блока 18 задания модуля (фиг.7ф), который, поступая на второй вход синхронизатора 16, а затем и на второй вход счетчика 46 строба, обнуляет его, в результате чего RS-триггер 47 переводится в единичное состояние, запирающий потенциал с второго входа третьего конъюнктора 45 снимается, импульсы "Такт 1" поступают на первый вход счетчика 46 и он возобновляет новый цикл счета формирует новый строб анализа. Длительность строба анализа определяется числом, декодируемым дешифратором 48 строба и задаваемым способом подключения его к выходам разрядов счетчика 46 строба. Начальная установка счетчика строба в нулевое состояние при включении питания устройства обеспечивается специальной цепью начальной установки, входящей в состав счетчика строба, о возможном варианте повторения которой сказано ниже.

Блок 18 задания модуля (фиг. 8) обеспечивает формирование начального значения пробного периода Tj Tjmin, наращивание пробного периода в каждом цикле на величину Δ Т, определение момента, когда текущее значение Тj превышает максимальное его значение Tjmax, и выдачу соответствующего импульса в этот момент в синхронизатор 16 для формирования нового строба анализа. Блок 18 задания модуля содержит счетчик 49 модуля и дешифратор 50 максимума.

Работает блок задания модуля следующим образом. На первом этапе работы устройства на третий вход блока задания модуля поступает строб анализа, который, воздействуя на третий вход счетчика 49 модуля, вписывает в него значение Тj Тjmin, поступающее с шины 24 минимального модуля на второй вход блока задания модуля и далее на второй вход счетчика 49 модуля в виде параллельного двоичного кода. На выходе счетчика модуля и, следовательно, на первом выходе блока задания модуля устанавливается параллельный двоичный код, численно равный Tjmin(фиг.9з). Дешифратор 50 максимума настроен на выделение значения Tj Tjmax, т.е. потенциал на его выходе изменяется, если на вход поступает двоичный код, эквивалентный значению Tj Tjmax + Δ T. На первом этапе работы устройства на первый вход блока 18 задания модуля и, следовательно, на первый (счетный) вход счетчика 49 модуля импульсы не поступают, поэтому блок задания модуля находится в режиме ожидания.

На втором этапе работы устройства строб анализа с третьего входа счетчика 49 модуля снимается, на его счетный вход начинают поступать импульсы конца цикла (фиг. 3и, 5и, 9и), соответствующие моментам завершения циклов анализа информации, накопленной в блоке 6. Это вызывает увеличение содержимого счетчика 49 модуля на единицу по каждому импульсу конца цикла, что приводит к наращиванию двоичного кода Тj на первом выходе блока 18 задания модуля на единицу, эквивалентную приращению значения Tj на Δ Т (фиг.3з, 9з). Процесс наращивания происходит до тех пор, пока Tj не достигнет своего максимального значения Tj Tjmax + Δ T. После завершения последнего цикла анализа в счетчике 49 модуля устанавливается двоичный код, эквивалентный значению Tj Tjmax + Δ T. При этом на выходе дешифратора 50 максимума происходит изменение потенциала, свидетельствующее о завершении второго этапа работы устройства, сигнал "Конец анализа". Этот перепад, поступая в синхронизатор 16, приводит к генерации синхронизатором нового строба анализа, который, поступая на третий (установочный) вход счетчика 49 модуля, вписывает в негор двоичный код Tjmin, и процесс работы блока 18 задания модуля повторяется так, как это описано выше. При этом на выходе дешифратора максимума происходит обратное изменение потенциала, в результате чего к моменту окончания второго этапа работы устройства формируется импульс (фиг.9ф) "Конец анализа", длительность которого определяется временем переходных процессов в синхронизаторе 16 при формировании переднего фронта строба анализа.

Модульный преобразователь 7 выполняет операции над каждым элементом массива значений временных интервалов t(i+1),i, накопленных в блоке 6 памяти на первом этапе работы устройства. Эти операции состоят в следующем. Очередное значение t(i-1),i, считанное из блока 6 памяти, складывается с содержимым регистра 52 промежуточного результата, в который первона- чально заносится "0", а затем предыдущее значение вычета Δ tij. Из полученной суммы последовательно раз за разом вычитается значение пробного периода Tj до тех пор, пока остаток не станет меньше Tj. Этот остаток и есть новое вычисленное значение вычета Δ t(i+1)j. Значение Δ t(i+1)j записывается в регистр 52 промежуточного результата. Одновременно с записью в регистр 52 промежуточного результата на третьем выходе модульного преобразователя 7 вырабатывается импульс "Завершение операций", который, поступая в блок 15 управления, наращивает код адреса и осуществляет считывание из блока 6 памяти нового значения временного интервала Δ ti,(i+1). Наряду с импульсом "Завершение операции" на втором выходе модульного преобразователя 7 вырабатывается импульс "Накопление", который поступает на тактовые входы всех счетчиков 9.1.9.n, сопровождая выдаваемый на первом выходе модульного преобразователя двоичный код полученного вычета Δt(i+1),j. Далее все описанные процессы повторяются.

Модульный преобразователь 7 (фиг.10) содержит сумматор 51, регистр 52 промежуточного результата, вычитатель 53, мультиплексор 54 вычетов, четвертый конъюнктор 55, второй компаратор 56, буферный регистр 57, расширитель 58, шестой элемент 59 задержки. Первый вход модульного преобразователя является первым входом сумматора 51, второй вход которого соединен с выходом регистра 52 промежуточного результата, а выход с первым входом мультиплексора 54 вычетов. Второй вход последнего соединен с выходом вычитателя 53, третий вход с выходом второго компаратора 56 и первым входом четвертого конъюнктора 55, а выход с первым входом буферного регистра 57, третий вход которого является третьим входом модульного преобразователя 7, второй вход вторым входом модульного преобразователя и соединен с входом расширителя 58, а выход является первым выходом модульного преобразователя и соединен с вторым входом вычитателя 53, вторым входом второго компаратора 56 и первым входом регистра 52 промежуточного результата. Третий вход регистра 52 соединен с вторым входом четвертого конъюнктора 55 и выходом расширителя 58, а второй вход является третьим выходом модульного преобразователя 7 и соединен с выходом четвертого конъюнктора 55, входом шестого элемента 59 задержки, выход которого является вторым выходом модульного преобразователя, четвертый вход которого соединен с третьим входом четвертого конъюнктора 55, а пятый вход с первым входом вычитателя 53 и первым входом второго компаратора 56.

Работа модульного преобразователя 7 заключается в следующем. На первом этапе работы устройства, когда происходит накопление информации в блоке 6 (в пределах строба анализа), модульный преобразователь находится в режиме ожидания. При этом информация от блока 6 на его первый вход не поступает, на второй его вход действует строб анализа, который устанавливает в буферном регистре 57 нулевое содержимое и удерживает его в этом состоянии, а также через расширитель 58 устанавливает в регистре 52 промежуточного результата нулевое содержимое и удерживает его в этом состоянии. В закрытом состоянии стробом анализа удерживается также четвертый конъюнктор 55. На пятый вход модульного преобразователя (первый вход вычитателя 53, являющийся входом вычитаемого) подается от блока 18 задания модуля двоичный код минимального значения пробного периода Tj Tjmin. На третий вход модульного преобразователя 7 поступает нечетная последовательность тактовых импульсов "Такт 1", которая далее поступает на третий (тактовый) вход буферного регистра 57, но не влияет на его состояние, так как он удерживается в нулевом состоянии. На четвертый вход модульного преобразователя 7 поступает четная последовательность тактовых импульсов "Такт 2", которая далее поступает на третий вход четвертого конъюнктора 55, но через него не проходит, так как он удерживается в запертом состоянии стробом анализа. Поэтому на втором и третьем выходах модульного преобразователя импульсы отсутствуют, а на первом информационном выходе присутствует нулевой двоичный код.

На втором этапе работы устройства, когда с второго входа модульного преобразователя 7 снимается строб анализа, снимается удержание буферного регистра 57 в нулевом состоянии, а спустя небольшой интервал времени, определяемый расширителем 58, отпирается четвертый конъюнктор 55 и снимается удержание в нулевом состоянии регистра 52 промежуточного результата. По заднему фронту строба анализа на первом входе сумматора 51 появляется код первого временного интервала t0,1 из нулевой ячейки блока 6 памяти, на его втором входе в это время действует нулевой код из регистра 52 промежуточного результата, поэтому на выходе сумматора 51 формируемая им сумма равна коду первого временного интервала (t0,1+0). Эта сумма поступает на первый (сигнальный) вход мультиплексора 54 вычетов, на втором входе которого присутствует код разности Tj Tjmin и нулевого содержимого буферного регистра 57, т. е. 0 Tjmin. В это время на первом входе второго компаратора 56 действует код Tj Tjmin, а на его втором входе нулевой код из буферного регистра 57, т. е. код на первом его входе больше кода на втором входе. При этом на выходе второго компаратора 56 присутствует потенциал, отпирающий четвертый конъюнктор 55 и пропускающий на выход мультиплексора 54 вычетов сигнал с его первого входа, т.е. сумму t0,1+0, которая первым тактовым импульсом нечетной последовательности "Такт 1" после заднего фронта строба анализа записывается в буферный регистр 57. Код этой суммы поступает на второй вход второго компаратора 56, где сравнивается со значением Tj Tjmin и на второй вход вычитателя 53, где из него вычитается Tj Tjmin, и разность подается на второй вход мультиплексора 54 вычетов. Если (t0,1+0) ≥ Tjmin, то потенциал на выходе второго компаратора 56 меняет свое значение, в результате чего запирается четвертый конъюнктор 55 и на выход мультиплексора 54 вычетов с выхода вычитателя 53 проходит результат вычитания [(t0,1+0) Tjmin] который вторым импульсом "Такт 1" записывается в буферный регистр 57, в результате чего на выходе вычитателя образуется разность (t0,1+0) 2Tjmin и т.д. до тех пор, пока разность [(t0,1 + 0) kTjmin] не станет меньше Tjmin, где k число циркуляций информации между мультиплексором 54, регистром 57, и вычитателем 53. В этот момент времени потенциал на выходе второго компаратора изменяется, в результате чего четвертый конъюнктор 55 отпирается, а мультиплексор 54 вычетов подключает к своему выходу свой первый вход. Однако состояние буферного регистра 57 до следующего импульса "Такт 1" не изменяется. Поэтому ближайший импульс четной последовательности "Такт 2" проходит через открытый четвертый конъюнктор 55 на второй (тактовый) вход регистра 52 промежуточных результатов и записывает в него разность [(t0,1 + 0) kTjmin] являющуюся первым значением вычета Δ tij. Это значение присутствует в виде двоичного кода на первом выходе модульного преобразователя 7 и поступает на вход дешифратора 8 и (n+1)-й вход мультиплексора 10. Этот код сопровождается импульсом "Завершение операции" с выхода четвертого конъюнктора 55, используемого для перехода к первому адресу хранения информации в блоке 6 памяти, а также задержанным в шестом элементе 59 задержки импульсом, который, поступая на тактовые входы счетчиков 9.1.9.n, увеличивает на единицу содержимое того из них, номер которого соответствует значению полученного вычета Δ t1j. Задержка в элементе 59 необходима для согласования с задержкой распространения кода вычета в дешифраторе 8.

К моменту прихода очередного импульса "Такт 1" из первой ячейки блока 6 памяти на первый вход сумматора 51 поступает значение второго временного интервала t1,2, которое складывается со значением вычета Δt1j, хранимого к этому времени в регистре 52 промежуточного результата. Сумма t1,2 + + Δ t1j через мультиплексор 54 вычетов попадает на первый вход буферного регистра 57, куда по этому (очередному) импульсу ("Такт 1") записывается. Далее происходящие процессы аналогичны описанным выше для первого значения временного интервала. Результатом этих процессов являются формирование второго значения вычета Δ t2j, запись его в регистр 52 промежуточного результата, наращивание на единицу содержимого соответствующего счетчика из группы (9.1.9.n) и переход к следующему адресу блока 6 памяти. Этот процесс завершается за две циркуляции (k=2), так как оказывается, что

t1,2 + Δ t1,j 2Tjmin + Δ t2j.

Полный цикл формирования массива вычетов по модулю Tjminзавершается, когда значение адреса, формируемого в блоке 15, достигает максимального значения. После этого происходит наращивание значения пробного периода Tj в блоке 18 задания модуля на величину Δ Т, на пятый вход модульного преобразователя 7 поступает двоичный код, соответствующий значению TjTjmin + Δ T, а блок 15 управления производит новый перебор по адресам, начиная с нулевого, значений временных интервалов. Модульный преобразователь начинает выполнять описанные выше функции в новом цикле вычисления вычетов по модулю Tj Tjmin + Δ T.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обнаружения периодических импульсных последовательностей и оценки их периода | 1989 |

|

SU1651225A1 |

| Анализатор импульсных последовательностей | 1989 |

|

SU1711089A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Программируемый логический контроллер | 1984 |

|

SU1497616A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| МНОГОКАНАЛЬНЫЙ ПАНОРАМНЫЙ ПРИЕМНИК | 1996 |

|

RU2115997C1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Многоканальный цифро-аналоговый преобразователь | 1981 |

|

SU1029409A1 |

Изобретение относится к измерительной технике и предназначено для обнаружения периодических импульсных последовательностей с неизвестным периодом повторения импульсов в аддитивной смеси с шумом и хаотической импульсной помехой. Устройство состоит из входной шины 1, квантователя 2, блока 3 стробирования, формирователя 4 импульсов, ключа 5 интервала, блока 6 памяти, модульного преобразователя 7, дешифратора 8, счетчиков 9. 1 ... 9.n, мультиплексора 10, порогового блока 11, блока 12 задания порога, ключа 13 вычета, ключа 14 модуля, блока 15 управления, синхронизатора 16, генератора 17, блока 18 задания модуля, блока ИЛИ 19, шин 20, 21, 22, 23, 24 обнаружения , вычета, модуля, порога квантования, минимального модуля соответственно. 2 з. п. ф-лы, 10 ил.

| Устройство обнаружения периодических импульсных последовательностей и оценки их периода | 1989 |

|

SU1651225A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-04-20—Публикация

1990-04-04—Подача