1

Изобретение относится к тепетрафной тезшике и технике передачи данных. : Известнйе устройство управлении делителя, сбдержанюе управляемый делитель, характеризуется низкой надежностью работы и возножностьк ложного фазирования.

Цель изобретения ft повышение надежг ности работы при исклк) Возможности Сложного фазирования. : Зго достигается тем, что единичный установочный вход каждот-о разряда управляемого делителя, кроме старшего, соединен с помощью схемы сборки, как через первую схему совпадения каждого разрша и схему инвертора этого разряда, так и через вторую схему совпадения того же разряда с одним из входов для сигналов величины рассогласования фаЗ| второй вход первой схекл.1 совпадения канадого разряда и пулевой вход старшего разряда управляомого делителя соединены с выходом совпадения на три входа, а второй вход другой схемы совпадения каждого , разряда соединен с выходом первой схек-шт совпадения на двя входа, едишршый установочный вход первого разряда соединен с помощью схемы сборки этого разряда также и с выходом другой схемы совпадения на два входа, второй вход, которой

соединен с одним плечом триггера, а первый вход вместе с первыми входами другой схемы совпадения на два входа и схемы совпадения на три вхо;да через элемент задержки .подсоединен к единичному

входу триггера, а Через другой элемент задержки - к первому выходу управляемого делителя, второй выход которого соединен с нулевым входом триггера, другое плечо триггера соединено с третьим

входом схемы совпадения на три входа, второй вход первой схемы совпадения на два входа и схемы совпадения на три входа соединены со входами для сигналов знака рассогпасования фаз.

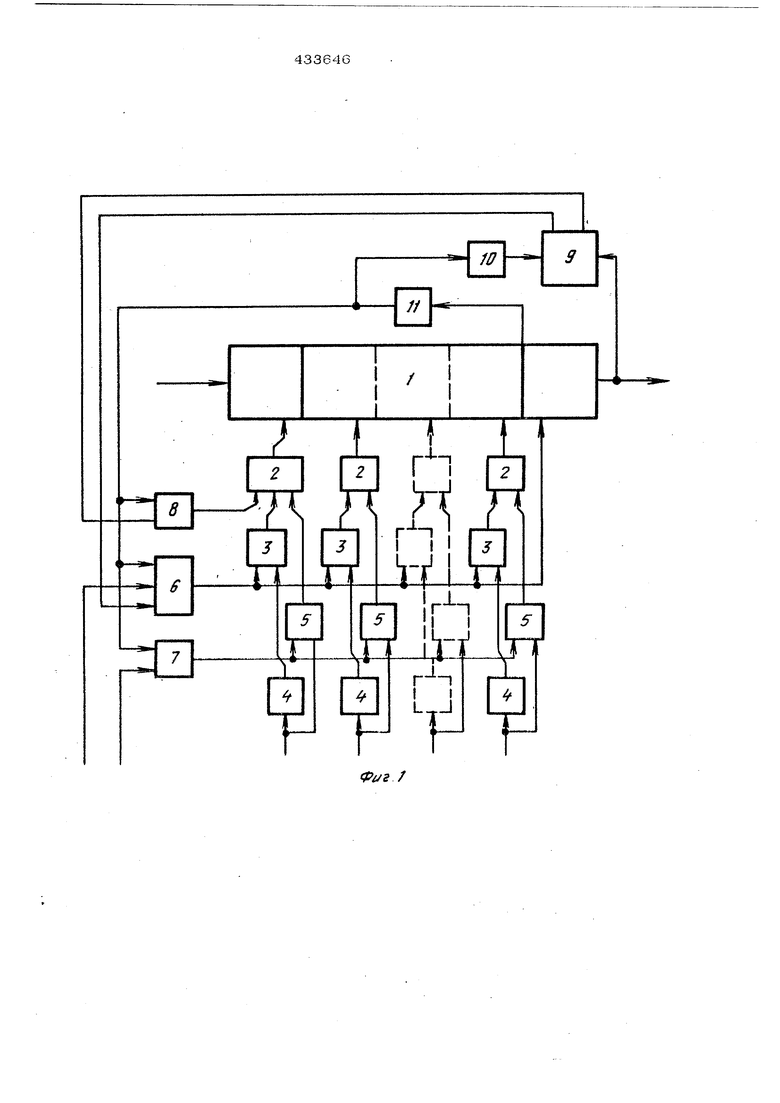

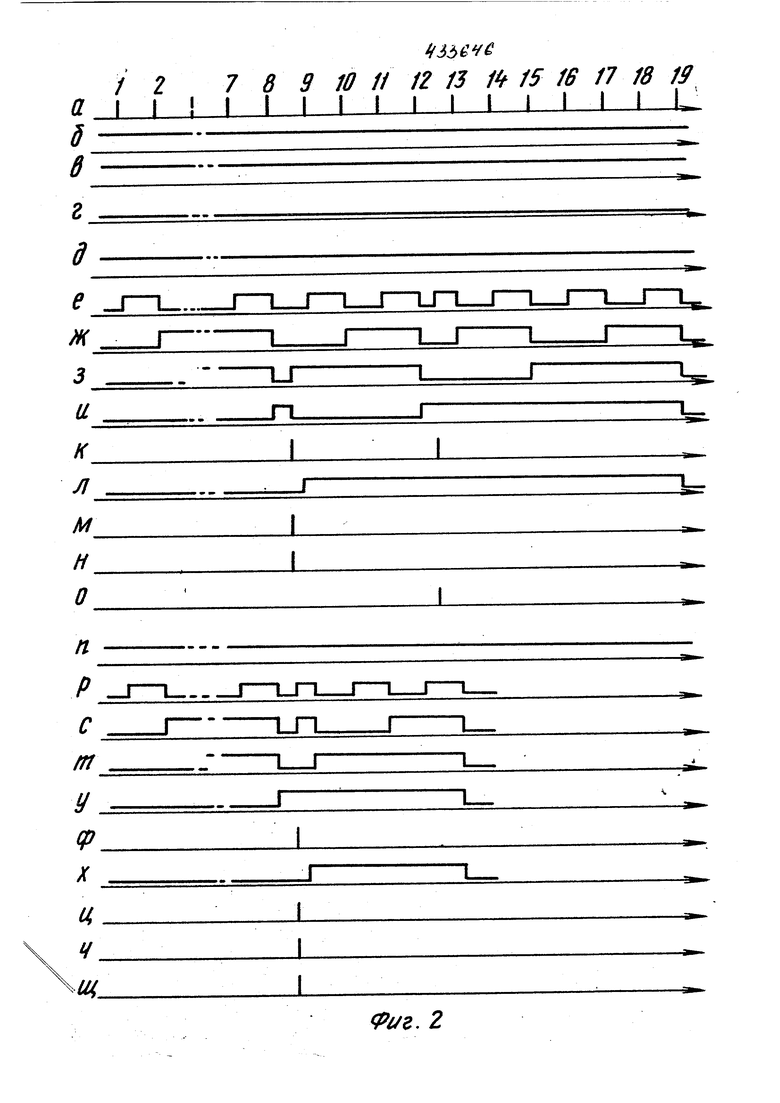

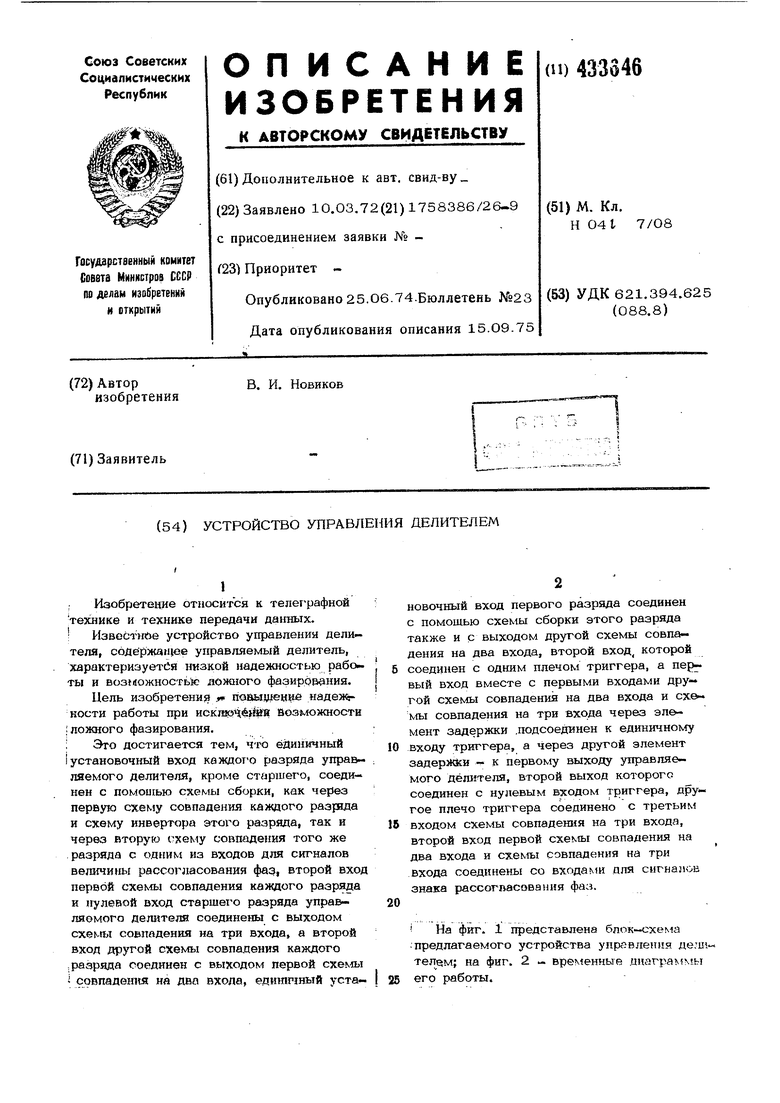

На фиг. 1 представлена блок- схема предлагаемого устройства управления деш на фиг. 2 - временные днaгpa ы его работы. 43 Устройство содержит: у1гравляемый делитель 1; схему 2 сборки; схему 3 совпа дения; схему инвертора -1; схекгу 5 совпадения на каждый разряд депитепя, кроме старшего; схему 6 совпадения на три вхо да; схемы 7,8 совпадения; триггер 9; элементы 10 к 11 задержки. Вход тактовой серии импульсов соеди-иен со входок- управляемого делителя 1, первый выход которого соединен со входом элемента 11 задержки, а второй выход с нулевым входом триггера 9. Выход элемента 11 задержки соединен со входом элемента 1О задержки и с первыми входами схем 6,7 и 8 совпадения, а выход элемента 10 задержки - с единичным вхо дом триггера 9, один выход которого сое нен с третьим входом схемы 6 совпадения на три входа, а другой - со вторым входом схемы 8 совпадения на два входа. Второй вход схемы 6 совпадения на три входа соединен со входом, на который подается сигнал Опережения, а второй вход схемы 7 совпадения на два входа - со входом, на который подается сигнал Отставания . Каждый вход из группы входов, на которые подается код величины рассогласования фаз, подсоединен ко входу инвертора 4 и ко входу схемы 5 совпадения. Вы ход инвертора 4 соединен со входом схемы 3 совпадения, второй вход схемы 5 совпадения с выходом схемы 7 совпади ния на два входа, а второй вход схемы 3 совпадения и нулевой установочный вход последнего разряда управ шемого делителя 1соеди(гены с выходом схемы 6 совпадения па 1рк входа. Выходы схем 3 и 5 совладо 1ия с:оеди 1е1 Ы со входами схемы 2сбо1)кн, п выход последней с единич- иым установочным входом соответствук июто f)Hзряда уиравляемотч; делителя 1. Третий вх;)Д схемы 2 сборки лервогл рагзряда соединен с вь(ходом с::хемы 8 совпадения на два входи. Первый выход управпяемсяо делите ля J является счетным входом сларшего , а второй выходвыходоь) :;троб импульсов. Элюры (см.) соответствуют работе устройства с коэффициентом деления де.чителя, равным 16. Эпюры д,е,ж,з,и, к,л,м,н,о поясняют работу устройства при наличии рассогласования фаз в сторону опережения, а эпюры п,р,с,т,у,ф,х,ц,ч,ш .поясняют работу устройства при наличии рассогласования фаз в сторону отставания Величина рассогласования фазы в обоих случаях взята одинаковой и равна трем пе} иидам частоты следования иг.цпяьсов иа вход управляемого деш1теля (3-1/F) НО- двои-чный код вел) рассоглас-; вания, равной 3-1/С. Тактовая серия импульсов поступает на вход делителя 1 с коэффициентом деления N (эпюра а). По мере поступления этих импульсов состояние управляемого делителя 1 изменяется (состояния 1,2, 3,4 разрядов управляемого делителя 1 показаны соответственно эпюрами е,ж,з, и,р,с,т,у). При поступлении импульсов в количестве, равном 1/2 N (8 импульсов), устанавливается состояние управляемого делителя ООО1, а на первом его выходе появляется сигнал (эпюры к,ф). При опережении строб-импульса по фазе на выходе управляемого делителя 1 за цикл работы его сигнал появится два раза (эпюра к). По первому сигналу срабатывает схема 6 совпадения на три входа (эпюра м), и на единичные установочные входы разрядов управляемого делителя ч&- . рез схемы инверторов 4, схемы 3 совпадения, схемы 2 сборок поступают сигналы обратного кода величины фазового рассогласования, ,т.е. установочный сигнал поступит только по третьему разряду (эшора и ). Так как старший разряд при этом устанавливается в нулевое состояние, то, по мере дальнейшего поступления импульсов на вход управляемого делителя 1, вновь установится состояние 0001 и на втором выходе управляемого делителя появится второй сигнал. По этому сигналу срабатывает схема 8 совпадения на два входа, и младший разряд управляемого делителя установится в единичное состояние. Этой установкой учитывается погрешность в коррекции фазы при первой установке унравляемого делителя 1. 9 разрешает срабатывание схем О и 8 совпадения один раз за цикл работь( управляемого делителя, а также устанавливает -очередность срабатывания этих схем совпадения. Тригг-ер 9 взв)дится сигналом, пос1унивишм с пергл; t, KXt-да управляемого делителя 1 через элементы П) и 11 задержки, а сбрасывается cmuanoi.-i со второго выхода управ- деличеля 1 (эпюры л, х). Вел№-. чина задержки элемента 11 должна соответспвовать окончанию перех,одных процессов в делителе 1, а элемента 10 - надежному срабатыванию схем 6 и 8 совпадения. При наличии отставания строб-импульса по фазе срабатывает схема 7 совпадения (эпюра ц), и на единичные установочные |входы управляемого делителя 1 через 5433 схемы 5 совпадений и схемы 2 сборок поступают сигналы величины фазового рассогласования в прямом коде. При этом сигналы появятся на установочных входах первого и второго разряда (эпюры з,щ). Из изложенного видно, что коррекция при отставании строй-импульса по фазе осуществляется установкой состояния управляемого делителя 1, которое являетс результатом, суммирования двоичной комби нации, соответствующей поступлению на вход делителя импульсов в количестве, равном 1/2, с двоичной комбинацией величины фазового рассогласования, а при оп& режении - результатом вычитания, причем результат вычитания получается двумя установками управляемого делителя. Предмет изобретения Устройство управления делителем, содержащее управляемый делитель, отличающееся тем, что, с целью повышения надежности работы при исключении возможности ложного фазирования, еди1шчный установочный вход каждого разряда управляемого делителя, кроме старшего, соединен с помощью схемы сборки, как через первую схему со впадения каждого разряда и схему инвертора этого разряда, так и через вторую схему совпаде}пш того же разряда с одним из входов для сигналов величины рассогласования фаз, второй вход первой схемы совпадения каждого разряда и нулевой вход старшего разряда управляемого делителя соединена с выходок cxeivoj совпадения на три входа, а второй вход другой cxejvibi совпадения каждого разряда соединен с выходом первой схемы совпадения на два входа, единичный уСтановочный вход первого разряда соединен с помощью схемы сборки этого разряда также и с выходом другой схемы совпадения на два входа, второй вход которой соединен с одним плечом триггера, а вход вместе с первыми входами другой схемы совпадения на два входа и сх&мы совпадения на три входа через эле юнт задержки подсоединен к единичному входу триггера, а через другой элемент задери ки - к первому выходу управляемого целителя, второй выход которого соединен с нулевым входом триггера, другое триггера соединено с третьим входом схемы совпадения на три входа, второй вход первой схемы совпадения на два входа и схемы совпадешш на три входа соединены со входами для сигналов знака рассогласования фаз.

I

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Устройство дискретного фазирования | 1980 |

|

SU1016847A1 |

| УСТРОЙСТВО АВТОПОДСТРОЙКИ ФАЗЫ СИГНАЛОВ | 1991 |

|

RU2027301C1 |

| Электронные часы с коррекцией | 1976 |

|

SU657396A1 |

| Преобразователь перемещения в код | 1988 |

|

SU1654973A1 |

| Преобразователь кода в суммарный интервал времени | 1983 |

|

SU1106012A1 |

| Цифровой генератор | 1986 |

|

SU1365071A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Преобразователь перемещения в код | 1982 |

|

SU1030824A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ КОЛИЧЕСТВА ПОСЛЕДОВАТЕЛЬНЫХ ИМПУЛЬСОВ | 1971 |

|

SU304706A1 |

L 1

ДТ

8

-«

л

T

I

ilLi

1Й

5

i

u

I I

( 7 1 2 783 Ю 11 I I I 1 12 13 1 15 16 17 18 19 I I I 1 I I I I

Авторы

Даты

1974-06-25—Публикация

1972-03-10—Подача