2. Преобразователь по п.1, отличающийся тем, что управляемый делитель частоты выполнен на п -разрядном двоичном счетчике импульсов, элементе ИЛИ и п элементах И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого подключён к выходу управляемого де.штеля частоты, установочные входы которого соедине:НЬ1 с первыми входами соответ твуклцих элементов И, вторые входы

которых объединены и подключены к счетному входу управляемого делителя частоты и входу п -разрядного дво ичного счетчика импульсов, инверсные выходы разрядов которого соединены с третьими входами соответствующих элементов И, причем остальные i-1 входов каждого г, -го элемента И, кроме первого соответственно соединены с прямыми выходами всех предшествующих разрядов двоичного счетчика импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Нониусный преобразователь кода во временной интервал | 1982 |

|

SU1034174A1 |

| Преобразователь код-временной интервал | 1983 |

|

SU1088115A1 |

| Измеритель временных интервалов | 1984 |

|

SU1190357A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1980 |

|

SU940295A2 |

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1986 |

|

SU1368993A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Преобразователь двоичного кода во временной интервал | 1990 |

|

SU1714811A1 |

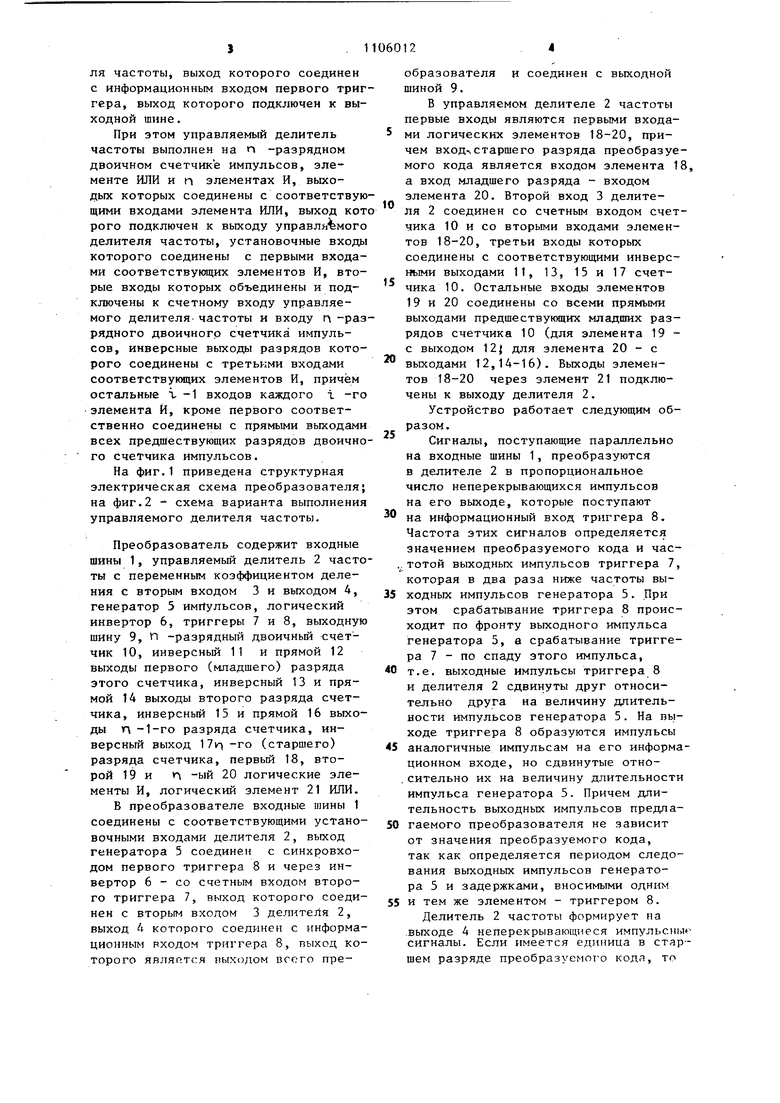

1. ПРЕОБРАЗОВАТЕЛЬ КОДА В СУММАРНЫЙ ИНТЕРВАЛ ВРЕМЕНИ, содержащий генератор импульсов и управляемый делитель частоты, установочные входы которого соответственно соединены с п входными шинами, отличающийся тем, что, с целью повышения точности преобразования, в него введены первый и второй триггеры и логический инвертор, вход которого соединен с выходом генератора импульсов и входом синхронизации первого триггера, а выход - со счетным входом второго триггера,выход которого подключен . к счетному входу управляемого делителя частоты, выход которого соединен с информационным входом первого триггера, выход которого подключен (Л к выходной шине.

Изобретение относится к импульсной технике, в частности к преобразователям кода в интервал времени, и может быть использовано для построения прецизионных преобразователей кода в напряжение с промежуточным преобразованием в число им пульсов стабильной длительности. Известен преобразователь кода в интервал времени, содержащий счетчик, генератор импульсов, триггер и логический элемент И, в котором пер вые входы счетчика соединены с кодо выми входими устройства, входы .логи ческого элемента И соединены с выхо дами генератора импульсов и триггер нулевой установочный вход которого соединен с выходом переполнения счетчика СП Недостаток этого устройства при использовании его в преобразователе кода в напряжение с промежуточны преобразованием в суммарный интерва времени заключается в том, что выходные импульсы неравномерно распре делены по периоду повторения. Это Приводит к увеличению пульсаций на выходе фильтра низких частот, который обычно применяется в преобразователях кода в напряжение с промежу точным преобразованием в число несоприкасающихся импульсов, длительности которых за период преобразования образуют суммарный интервал в мени. Наиболее близким к предлагаемому по технической сущности является преобразователь кода в суммарный ин терзал времени, содержащий генератор импульсов и управляемьй делитель частоты, установочные входы которого соединены с П входными шинами, счетный вход подключен к выходу генератора импульсов, а выход - к выходной шинеС2 . В этом преобразователе число выходньгх несоприкасающихся импульсов за период преобразования распределено более равномерно, что уменьшает пульсации в выходном сигнале преобразователя кода в напряжение, построенном на основе промежуточного преобразователя. Однако и этот преобразователь характеризуется недостатком, выражающимся в нарушении идентичности по длительности выходных импульсов, так как при различных кодах выходной импульс формируется различными логическими элементами с неидентичными задержками. Цель изобретения - повышение точности преобразования. Поставленная цель достигается тем, что в преобразователь кода в суммарный интервал времени, содержащий генератор импульсов и управляемый делитель частоты, установочные входы которого соответственно соединены с п входными шинами,введены первый и второй триггеры и логический инвертор, вход которого соединен с выходом генератора импульсов и входом синхронизации первого триггера, а выход - со счетным входом второго триггера, выход которого подключен к счетному входу управляемого делителя частоты, выход которого соединен с информационным входом первого триггера, выход которого подключен к выходной шнне.

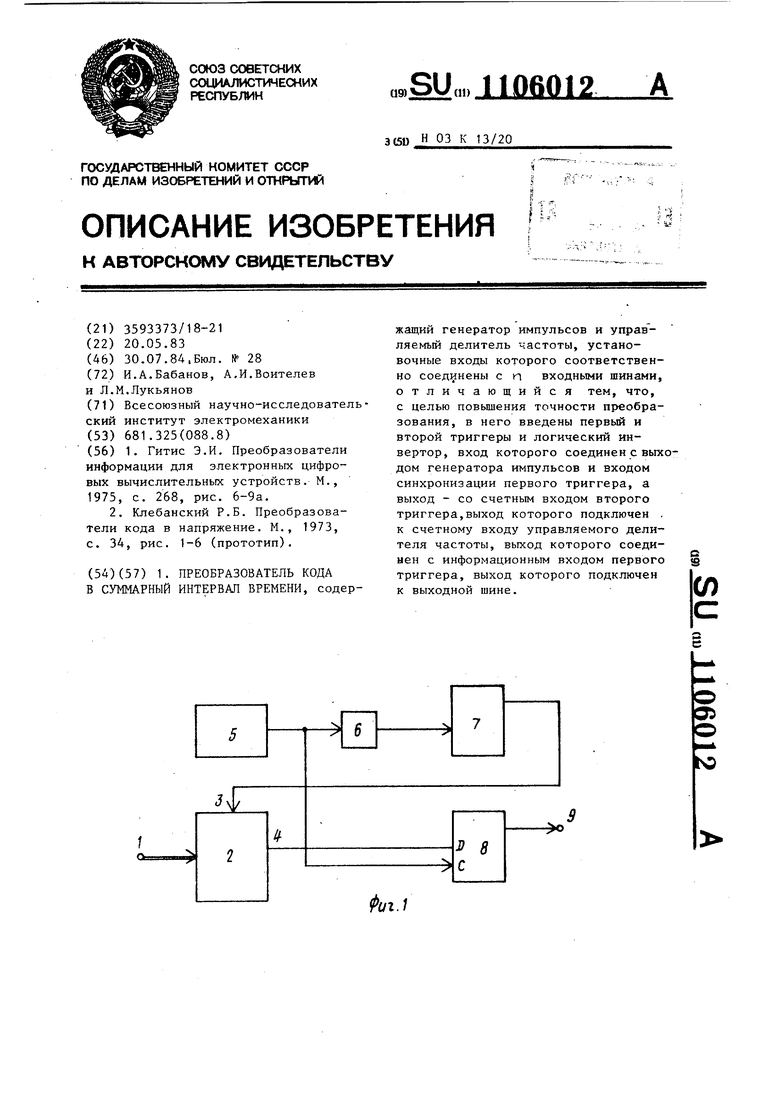

При этом управляемый делитель частоты выполнен на п -разрядном двоичном счетчике импульсов, элементе ИЛИ и г элементах И, выходых которых соединены с соответствующими входами элемента ИЛИ, выход кот рого подключен к выходу управляемого делителя частоты, установочные входы которого соединены с первыми входами соответствующих элементов И, вторые входы которых объединены и подключены к счетному входу управляемого делителя- частоты и входу 1Л -разрядного двоичного счетчика импульсов, инверсные выходы разрядов которого соединены с третьими входами соответствующих элементов И, причём остальные ч. -1 входов каждого г -го элемента И, кроме первого соответственно соединены с прямыми выходами всех предшествующих разрядов двоичного счетчика импульсов.

На фиг.1 приведена структурная электрическая схема преобразователя; на фиг.2 - схема варианта выполнения управляемого делителя частоты.

Преобразователь содержит входные щины 1, управляемьй делитель 2 частоты с переменным коэффициентом деления с вторым входом 3 и выходом 4, генератор 5 имПульсов, логический инвертор 6, триггеры 7 и 8, выходную шину 9, П -разрядный двоичный счетчик 10, инверсньй 11 и прямой 12 выходы первого (младшего) разряда этого счетчика, инверсный 13 и прямой 14 выходы второго разряда счетчика, инверсный 15 и прямой 16 выходы п -1-го разряда счетчика, инверсный выход 17и| -го (старшего) разряда счетчика, первый 18, второй 19 и п -ый 20 логические элементы И, логический элемент 21 ИЛИ.

В преобразователе входные шины 1 соединены с соответствующими установочными входами делителя 2, выход генератора 5 соединен с синхровходом первого триггера 8 и через инвертор 6 - со счетным входом второго триггера 7, выход которого соединен с вторым входом 3 делителя 2, выход 4 которого соединен с информацио} ным входом триггера 8, выход которого являр.тся пы. всего преобразователя и соединен с выходной шиной 9.

В управляемом делителе 2 частоты первые входы являются первыми входами логических элементов 18-20, причем вход старше го разряда преобразуемого кода является входом элемента 1 а вход младшего разряда - входом элемента 20. Второй вход 3 делителя 2 соединен со счетным входом счетчика 10 и со вторыми входами элементов 18-20, третьи входы которых соединены с соответствующими инверсными выходами 11, 13, 15 и 17 счетчика 10. Остальные входы элементов 19 и 20 соединены со всеми прямьгми выходами предшествующих младших разрядов счетчика 10 (для элемента 19 с выходом 12 для элемента 20 - с выходами 12,14-16). Выходы элементов 18-20 через элемент 21 подключены к выходу делителя 2.

Устройство работает следующим образом.

Сигналы, поступающие параллельно на входные шины 1, преобразуются в делителе 2 в пропорциональное число неперекрывающихся импульсов на его выходе, которые поступают на информационный вход триггера 8. Частота этих сигналов определяется значением преобразуемого кода и частотой выходных импульсов триггера 7, которая в два раза ниже частоты выходных импульсов генератора 5. При этом срабатывание триггера 8 происходит по фронту выходного импульса генератора 5, а срабатывание триггера 7 - по спаду этого импульса, т.е. выходные импульсы триггера 8 и делителя 2 сдвинуты друг относительно друга на величину длительности импульсов генератора 5. На выходе триггера 8 образуются импульсы аналогичные импульсам на его информационном входе, но сдвинутые относительно их на величину длительности импульса генератора 5. Причем длительность выходных импульсов предлагаемого преобразователя не зависит от значения преобразуемого кода, так как определяется периодом следования выходных импульсов генератора 5 и задержками, вносимыми одним и тем же элементом - триггером 8. Делитель 2 частоты формирует на

.выходе 4 неперекрывающиеся импульснысигналы. Если имеется единица в старшем разряде преобразусмо1-о кода, то 51 открыт по первому входу элемент 18, и через него проходят сигналы, посту пающие на вход 3 делителя частоты, в те моменты, когда младший разряд счетчика находится в состоянии нуля, т.е. на выходе элемента 18 формируются импульсы наибольшей частоты. На выходе элемента 19 аналогично фор мируются импульсы, но при наличии единицы в следующем за старшим разряде преобразуемого кода, но в моме ты, когда нпадший разряд счетчика 10 находится в единич ном состоянии, а второй младший его разряд - в нулевом состоянии, т.е. на выходе элемента 19 формируются импульсы с частотой в два раза меньшей, чем на выходе элемента 18 и т.д. На выходе элемента 20, управляемо го инверсным вь13{одом старшего разряда счетчика 10, при наличии единицы в младшем разряде преобразуемого кода за период работы этого счетчика формируется только один импульс в момен совпадения единичных состояний во всех более младших разрядах счетчика 10. Таким образом, преобразователь позволяет получить прецизионные, строго идентичные по длительности выходные импульсные сигналы, количество которых равно значению преобразуемого кода. ТехЙико-экономический эффект от использования изобретения заключается 35 в том, что импульсы выходной после2довательности в предлагаемом устройстве обладают значительно большей идентичностью и стабильностью по длительности, что существенно повышает точность преобразования кода в суммарньй интервал времени. Улучшение идентичности и стабильности подтверждается следующим. Длительность импульса на выходе логического элемента в общем случае определяется выражением U tu4-t-j$ -fcic. , где - длительность входного импульсарвремя задержки фронта время задержки спада. Обычно 1зсрт tjj, поэтому можно написать , ty iaxt A-t , где t r-tsq,--t) Для предлагаемой схемы имеем tn fcgy t-д-Ь-3 (знак можно взять любой, но какой-нибудь один для конкретного типа триггера 8). Для прототипа выходной импульс равен ty « . -т.ду ± д-tj , причем для различных значений . г задержки л Lai могут быть различными как по знаку, так и по величине из-за неидентичности параметров различных логических элементов. Таким образом, длительность йыходных импульсов преобразователя строго постоянна не зависимо от значения преобразуемого кода.

/

12 13

//

I

W

о

6

s/

Щ

5ПV

Sy

2ff

tl.

21 f.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гитис Э.И | |||

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М., 1975, с | |||

| Способ изготовления гибких труб для проведения жидкостей (пожарных рукавов и т.п.) | 1921 |

|

SU268A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Клебанский Р.Б | |||

| Преобразователи кода в напряжение | |||

| М., 1973, с | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-07-30—Публикация

1983-05-20—Подача