1

Изобретение относится к имнульсной технике и может быть иснользовано в телемеханике и дискретной автоматике.

Известные формирователи, выполненные на потенциальных элементах, содержащие статические триггеры с раздельными входами, схемы совпадения, управляющие триггерами, инверторы, имеют низкую помехозащищенность.

Цель изобретения - повысить помехозащищенность устройства.

Для этого в него введен парафазный генератор импульсов, выходы которого соединены с дополнительными выходами схем совпадения.

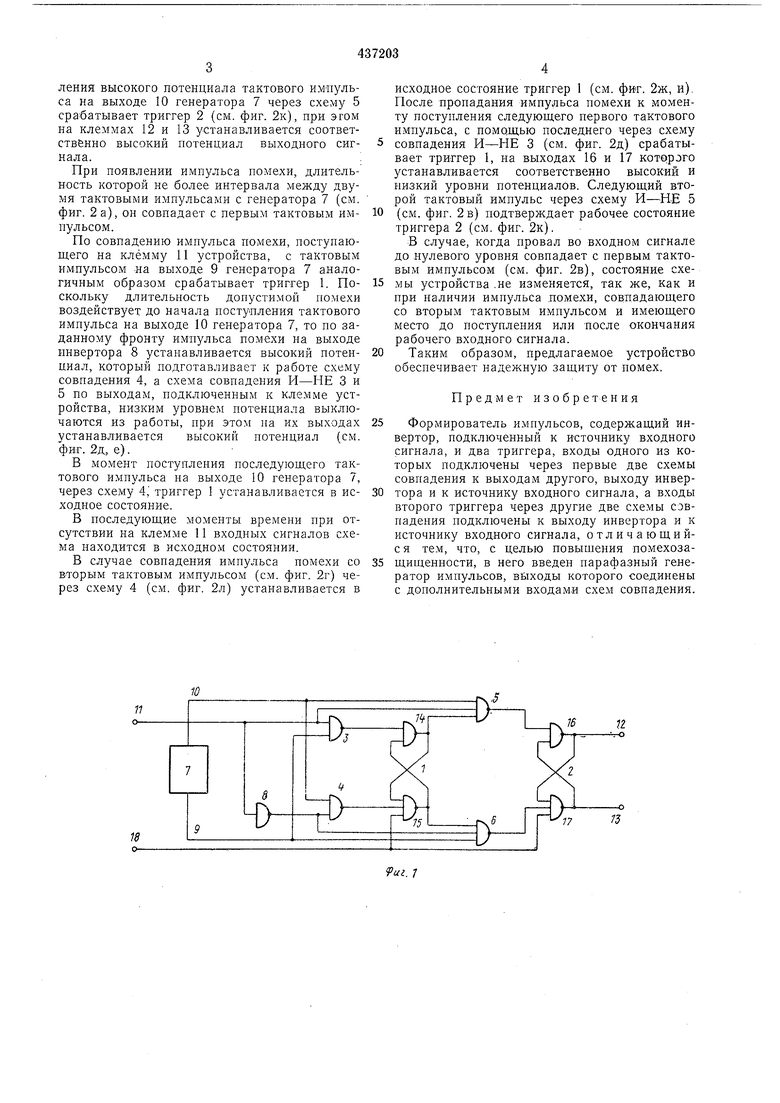

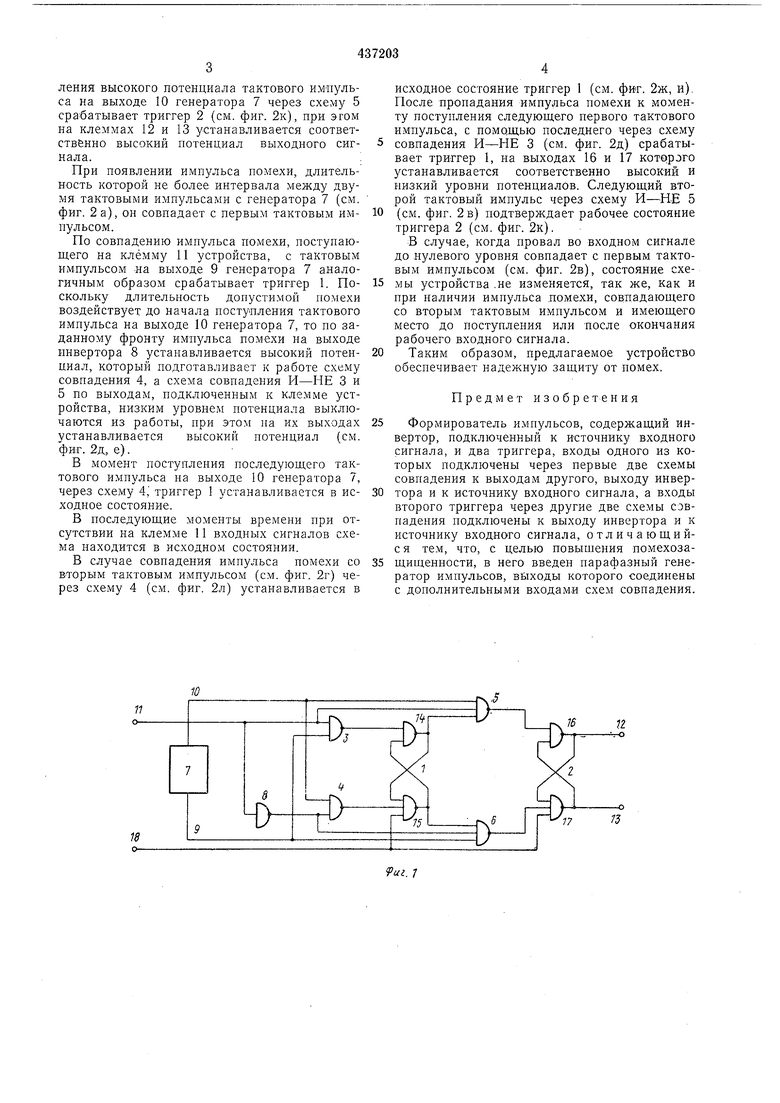

На фиг. 1 показана функциональная схема формирователя; на фиг. 2 - временные диаграммы работы устройства.

Формирователь содержит статические триггеры 1, 2 с раздельными входами, логические схемы И-НЕ 3 и 4 на два входа, логические схемы И-НЕ 5 и 6 на три входа соответственно, управляющие единичным и нулевым входами триггеров 1, 2, двухтактный генератор 7 импульсов, инвертор 8. Одни из входов логических схем И-НЕ 3, 6 и 4, 5 попарно объединены и подключены к выходам 9 и 10 двухтактного генератора импульсов. Формирователь содержит также входную клемму 11; выходные клеммы 12 и 13 соответственно для прямого и инверсного выходных сигналов, единичный и нулевой выходы 14, 15, 16, 17 - триггеров 1 и 2, шину сброса 18. Устройство работает следующим образом. В исходное состояние схему устанавливают импульсом низкого потенциала, поступающего по шине сброса. При этом на клемме 11 низкий потенциал входного импульса, на выходе инвертора 8-высокий потенциал, а с выходов 9 и 10 генератора 7 поступают тактовые

импульсы (см. фиг. 2а, б, в, г). На выходах схем совпадения И-НЕ 3 и 5, на выходах 15 и 17 триггеров 1 и 2 устанавливается высокий потенциал (см. фиг. 2д, е, ж, з), а на выходах 14 и 16 триггеров 1 и 2 низкий потенциал (см.

фиг. 2 и, к).

При этом на выходах схем совпадеипя И- НЕ 4 и 6 (см. фиг. 2 л, м) будут вырабатываться импульсы, инвертированные по отношению к импульсам, поступающим с выходов

10 и 9 генератора 7.

В случае высокого потенциала на клемме 11 и по совпадению с высоким гготенциалом тактового импульса на выходе 9 генератора 7 через схему совпадения И-НЕ 3 срабатывает

триггер 1 (см. фиг. 2м), на выходе 14 которого высокий потенциал подготавливает для работы схему совпадения.

При этом па выходах логических схем И- НЕ 4 и 6 устанавливается высокий потенциал

(см. фиг. 2л, м). В следуюп;ий момепт появ

ления высокого потенциала тактового импульса на выходе 10 генератора 7 через схему 5 срабатывает триггер 2 (см. фиг. 2к), при эгом на клеммах 12 и 13 устанавливается соответственно высокий потенциал выходного сигнала..

При появлении импульса помехи, длительность которой не более интервала между двумя тактовыми импульсами с генератора 7 (см. фиг. 2 а), он совпадает с первым тактовым импульсом.

По совпадению импульса помехи, поступающего на клемму 11 устройства, с тактовым импульсом на выходе 9 генератора 7 аналогичным образом срабатывает триггер 1. Поскольку длительность допустимой помехи воздействует до начала поступления тактового импульса на выходе 10 генератора 7, то по заданному фронту импульса помехи на выходе инвертора 8 устанавливается высокий потенциал, который подготавливает к работе схему совпадения 4, а схема совпадения П-НЕ 3 и 5 по выходам, подключенным к клемме устройства, низким уровнем потенциала выключаются из работы, при этом па их выходах устанавливается высокий потенциал (см. фиг. 2д, е).

В момент поступления последующего тактового импульса па выходе 10 генератора 7, через схему 4, триггер 1 устанавливается в исходное состояние.

В последующие моменты времени при отсутствии на клемме 11 входных сигналов схема находится в исходном состоянии.

В случае совпадения импульса помехи со в-торым тактовым импульсом (см. фиг. 2г) через схему 4 (см. фиг. 2л) устанавливается в

исходное состояние триггер 1 (см. фит. 2ж, и). После пропадания импульса помехи к моменту поступления следующего первого тактового импульса, с помощью последнего через схему

совпадения И-НЕ 3 (см. фиг. 2д) срабатывает триггер 1, на выходах 16 и 17 которого устанавливается соответственно высокий и низкий уровни потенциалов. Следующий второй тактовый импульс через схему И-НЕ 5

(см. фиг. 2 в) подтверждает рабочее состояние триггера 2 (см. фиг. 2к).

В случае, когда провал во входном сигнале до нулевого уровня совпадает с первым тактовым импульсом (см. фиг. 2в), состояние схемы устройства .не изменяется, так же, как и при наличии импульса помехи, совпадающего со вторым тактовым импульсом и имеющего место до поступления или после окончания рабочего входного сигнала.

Таким образом, предлагаемое устройство обеспечивает надежную защиту от помех.

Предмет изобретения

Формирователь импульсов, содержащий инвертор, подключенный к и-сточнику входного сигнала, и два триггера, входы одного из которых подключены через первые две схемы совпадения к выходам другого, выходу инвертора и к источнику входного сигнала, а входы второго триггера через другие две схемы совпадения подключены к выходу инвертора и к источнику входного сигнала, отличающийс я тем, что, с целью повышения помехозащищенности, в него введен парафазный генератор импульсов, выходы которого соединены с дополнительными входами схем совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по длительности | 1979 |

|

SU817998A1 |

| Стабилизированный преобразователь постоянного напряжения | 1981 |

|

SU1012224A1 |

| Преобразователь однофазного напряжения в трехфазное | 1986 |

|

SU1376185A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Устройство для выделения одиночного импульса | 1989 |

|

SU1621147A1 |

| ИМПУЛЬСНОЕ УСТРОЙСТВО | 1971 |

|

SU433629A1 |

| Селектор импульсов по периоду следования | 1980 |

|

SU892696A1 |

| Устройство подавления помех | 1978 |

|

SU741436A1 |

| Устройство для задержки импульсов | 1978 |

|

SU790217A1 |

| Цифровой частотомер | 1984 |

|

SU1236384A1 |

75 72

м

Авторы

Даты

1974-07-25—Публикация

1972-01-20—Подача