-ч со со ел

00

ю

Изобретение относится к технике передачи сигналов и может использоваться в устройствах телеуправления, телеконтроля и цифровой связи, работающих в асинхронном режиме/для регенерации дискретных сигналов, передаваемых по физическим линиям или радиолиниям с высоким уровнем помех. ..... :

Известен цифровой асинхронный регенератор импульсных сигналов, содержащий генератор импульсов, первый и второй элементы И, реверсивный счетчик, элемент НЕ, делитель частоты с переменным коэффициентом деления, дешифратор и выходной триггер...

Недостатком этого цифрового асинхронного регенератора является искажение длительностей элементарных посылок принимаемых дискретных сигналов, которое выражается в уменьшении длительностей импульсов и увеличении длительностей пауз в выходном регенерированном сигнале и имеет место как при поступлении на вход регенератора посылок без искажений, так при поступлении посылок уже имеющих искажения. -.-.

Цифровой асинхронный регенератор декретных сигналов обеспечивает исключение искажений длительностей принимаемых посылок сигнала.

По технической сущности это устройство наиболее близко к заявляемому и принято за прототип. Этот цифровой асинхронный регенератор дискретных сигналов .содержит выходной триггер, генератор импульсов, делитель частоты, четыре элемента И, реверсивный счетчик, дешифратор, инвертор, детектор уровня, RS-триг- гер управления, одновибратор, дополнительный инвертор, два элемента ИЛИ и датчик тактовых импульсов. Детектор уровня состоит из RS-триггера, элемента И и интегратора.

Недостатком прототипа является низкая помехоустойчивость, обусловленная .тем, что, при равновероятности появления врезок в принимаемых импульсных сигналах и импульсов помех в паузах, отсутствие принудительного сброса реверсивного счетчика обеспечивает возможность накопления в нем числа, определяемого импульсами помех, достаточного для формирования сигнала на первом выходе дешифратора, что определяет возможность ложной установки выходного триггера в единичное состояние при отсутствии передаваемого сигнйла. Кроме того, низкая помехоустойчивость .этого устройства обусловлена также тем, что выходной сигнал RS-триггера в дегектопе уровня, разрешающий работу устройства, формируется при поступлении на S-вход этого триггера любого из импульсов помех независимо от длительности, что при отсутствии передачи

дискретной информации и наличии импульсных помех в канале связи обеспечивает практически постоянное присутствие на выходе детектора уровня сигнала, разрешающего работу регенератора.

0 Целью изобретения является повышение помехоустойчивости.

Реализация поставленной цели достигается тем, что в цифровой асинхронный регенератор дискретных сигналов, содер5 жащий детектор уровня, генератор тактовых импульсов, счетчик, Д-триггер, выход .которого является выходом регенератора, . входом которого является вход детектора уровня, и последовательно соединенные

0 RS-триггер, одновибратор и элемент ИЛИ .введены два блока задержки, мажоритарный блок, генератор серии импульсов и регистр сдвига, информационный и тактовый входы и выходы которого соединены соот5 ветственно с выходом первого блока задержка, вход которого подключен ко входу детектора уровня, с выходом генератора серии импульсов; ко входу которого подклю- . чён выход элемента ИЛИ, и со входом

0 мажоритарного блока, выход которого подключен к информационному входу Д-тригге- ра, динамический вход которого соединен с выходом второго блока задержки, ко входу которого подключен выход элемента ИЛИ, и

5 с тактовым входом счетчика, управляющий и установочный входы и выход которого соединены соответственно с инверсным выходом RS-триггера, с выходом Д-триггера и с R-входом RS-триггера, S-вход и прямой вы0 ход которого соединены соответственно с выходом Д-триггера и со входом генератора тактовых импульсов, выход которого подключен ко второму входу элемента ИЛИ. при этом выход детектора соединен с пуско5 вым входом одновибратора.

Реализация поставленной цели достигается также тем, что детектор уровня содержит последовательно соединенные фильтр нижних частот и пороговый блок,

0 выход которого является выходом детектора уровня, входом которого является вход фильтра нижних частот.

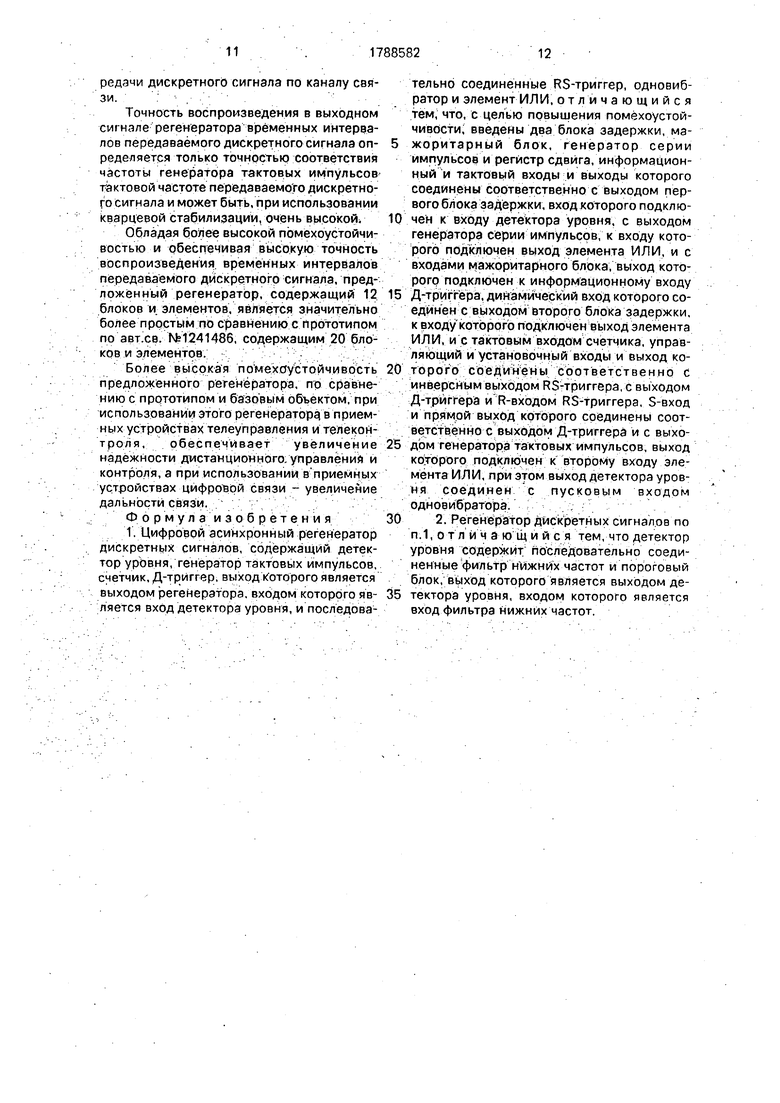

На фиг. 1 изображена структурная электрическая схема предложенного генерато5 ра; на фиг. 2 - временные диаграммы. поясняющие работу предложенного регенератора,

Цифровой асинхронный регенератор дискретных сигналов содержит дотек т о;- уровня 1. одновибратор 2, элемент ИЛИ °,

генератор серии импульсов 4, регистр сдвига 5, мажоритарный блок 6, Д-триггер 7, первый блок задержки 8. второй блок задержки 9, счетчик 10, RS-триггер 11, и генератор тактовых импульсов 12, при этом детектор уровня 1 содержит последовательно соединенные фильтр нижних частот 13 и пороговый блок 1.4.

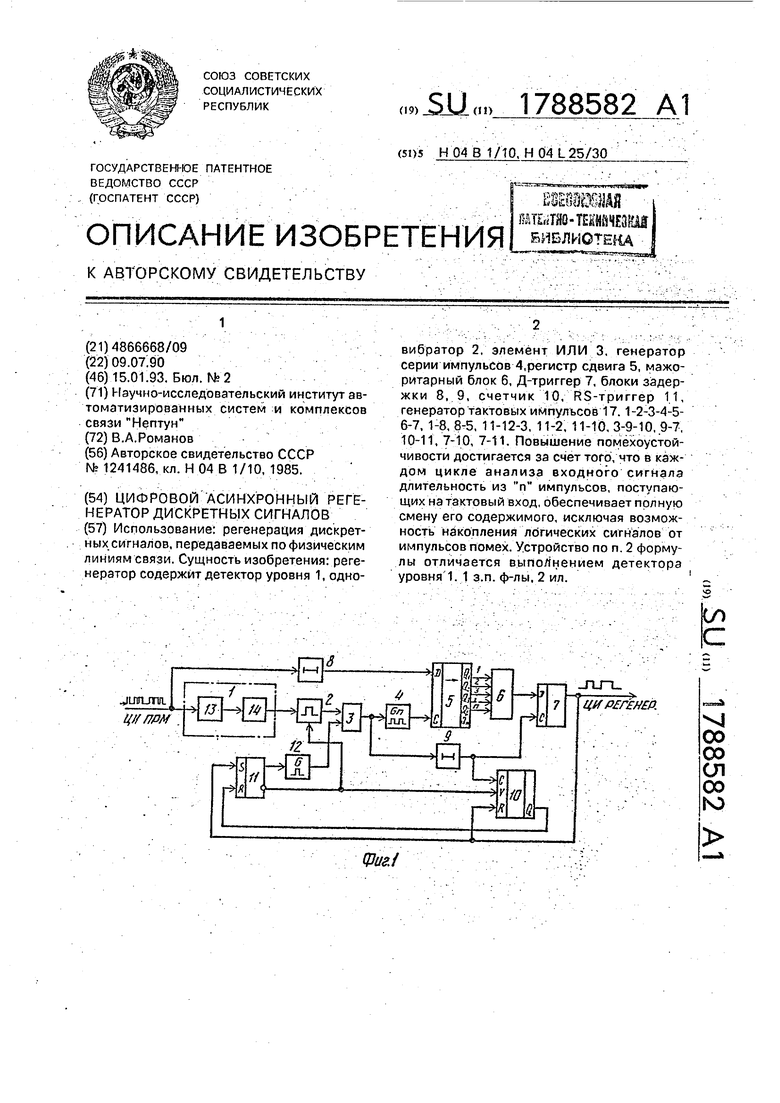

На фиг. 2 изображены следующие временные диаграммы, поясняющие принцип работы предложенного регенератора:

а - передаваемый сигнал, где Тт - длительность тактового интервала одной элементарной посылки;

б - сигнал на входе регенератора при наличии в нем ложных импульсов, дроблений и краевых искажений, обусловленных помехами в канале связи;

в - сигнал на выходе детектора уровня 1, где tfl y - время анализа уровня сигнала де- тектором уровня;

г - сигнал на выходе одновибратора 2, где 1одн - длительность импульса;

д - сигнал на выходе первого блока задержки 8, где 13эд1 - время задержки;

е -сигнал на выходе генератора серии импульсов 4, где Тп - период следования импульсов.

Теп - длительность серии из п импуль- сов;

ж - сигнал на прямом выходе RS-тригге- ра 11;

з - сигнал на выходе генератора тактовых импульсов 12;

и - сигнал на выходе первого (младшего) разряда n-разрядного регистра сдвига 5;

к - сигнал на выходе второго разряда n-разрядного регистра сдвига 5;

л - сигнал на выходе третьего разряда п-разрядного регистра сдвига 5;

м - сигнал на выходе четвертого (1-го) разряда n-разрядного регистра сдвига 5;

н - сигнал на выходе последнего (старшего) разряда n-разрядного регистра сдви- га 5;

п - сигнал на выходе n-входового мажоритарного блока 6;

р - сигнал на выходе второго блока задержки 9, где т3ад2 - время задержки;

с - сигнал на выходе счетчика 10;

т - регенерированный сигнал на выходе Д-триггера 7.

Цифровой асинхронный регенератор дискретных сигналов работает следующим образом.. .

В исходном состоянии, при отсутствии на входе регенератора сигнала и наличии импульсов помех, длительности которых не

превышают времени зналйза детектором уровня 1 входного сигнала, на выходе этого детектора сохраняется потенциал низкого логического уровня. Время т.ду анализа уровня входного сигнала регенератора детектором уровня 1 определяется частотой среза ftp фильтра нижних частот 13, его порядком и порогом срабатывания порогового устройства 14.. ,

Если длительность tn импульса помехи на входе регенератора превышает время 1ду анализа уровня, например, равное одной третьей длительности Тт тактового интервала элементарной посылки передаваемого сигнала, то амплитуда выходного сигнала фильтра нижних частот 13 превышает порог срабатывания порогового блока 14, на выходе которого формируется положительный импульс. Фронт выходного импульса детектора уровня 1 обеспечивает запуск одновибратора 2, выходной импульс которого длительностью Ьдн, например. мкс, поступая через элемейт ИЛИ 3, осуществляет запуск регенератора серии импульсов 4, формирующего на своем выходе серию, из нечетного числа п импульсов, например, из пяти импульсов

Период следования Тп выходных импульсов генератора серии импульсов 4 оп ределяется из соотношения

Тп

Тт

п Ч- 1

где п - любое целое нечетное число 3.

Первый блок задержки 8 обеспечивает задержку входного сигнала регенератора (фиг. 2 б,д) на время т.зад1. например, на

время т. -д-Тт.

Импульсы, поступающие на тактовый С- вход n-разрядного регистра сдвига 5 обеспечивают последовательную запись в этот регистр сигнала, поступающего на его информационный Д-вход .с выхода блока задержки 8. При этом, если длительность tn импульса помехи не превышает половины тактового интервала Тт элементарной посылки передаваемого сигнала, то за время Теп. соответствующее длительности сигнала серии из п импульсов , импульсы, поступающие на тактовый С-вход регистра сдвига 5, обеспечивают запись в регистр

значений сигнала логической единицы и значений сигнала логического нуля. -.

Например, при скорости передачи информации КБОД. ,25 мкс, частоте

ледования импульсов генератора серии из импульсов 4 кГц, ,2 мкс и длиельности импульса помехи мкс серия из п-5 импульсов обеспечивает запись в регистр сдвига 5п значений сигнала логической единицы и значений сигнала огического нуля. При этом, по окончании серии из импульсов с разрядных выхоов 1 ...п регистра сдвига 5 на соответствующие входы мажоритарного блока 6 поступает параллельный код, код Q0011, обеспечивающий установку на выходе мажоритарного блока 6 сигнала логического нуля.:

Выходной импульс второго блока задержки 9, задержанный по отношению к выходному/импульсу одновибратора 2 на время т.3ад2 Т«(п+1), например, на время t3afl2 5,2(5+1)31,2 мкс, поступая на динамический С-вход Д-триггера 7на информационный вход которого поступает сигнал логическогонул;я, подтверждает нулевое сотояние выходного Д-триггера 7. г При поступлении на вход регенератора принимаемого дискретного сигнала (фиг. 26), содержащего импульсы помех в паузах, g также имеющего дробления и краевые искажения обусловленные помехами в канале связи, по окончаний времени tfly анализа уровня первого импульса этого дискретного сигнала на выходе детектора уровня 1 фор- ми руется по ложйтел ьн ы и им пул ьс (фи г. 2 в), фронт которого обеспечивает запуск одно- вибратора 2. Выходной импульс (фиг. 2) одновибратора 2, поступая через элемент I/I Л И 3, обеспечивает запуск генератора серии импульсов 4, который формирует на своем вьгходе серию из нечётного числа п импульсов. Первый блок задержки 8 обеспечивает задержку входного сигнала регенератора на время, равное времени анализа уровня входного сигнала детектором 1 уровня, например, г3ад1 Ю мкс.:. - Серия из п импульсов, поступающих на тактовый С-вход п-разрядного регистра сдвига 5 обеспечивает последовательную запись в ячейки памя тй Этого регистра сигнала (фиг, 2д), поступающего на его информационный Д-вход. Каждый импульс Серии из п импульсов обеспечивает запись в первый (младший) разряд п-разрядного регйст-. ра сдвига 5 соответствующего текущего значения входного информационного сигнала, а также осуществляет сдвиг на один разряд всего содержимого этого регистра (фиг. 2 и, к, л, м, н).

Так как nptf передаче по каналу связи единичного сиг нзла в принимаемом искаженном сигнале (фиг-. 2 б) сумма длительностей импульсных сигналов высокого

логического уровня на интервале времени превышает сумму длительностей сигналов низкого логического уровня, то серия из нечетного числа п импульсов обеспечивает запись в n-разрядный регистр сдвига 5 числа щ единиц большего, чём число п0 нулейНапример, по окончании серии импульсов (фиг. 2 е), обеспечивающих запись в ре0 гистр сдвига 5 первого единичного бита принимаемого сигнала (фиг. 2д) на выходе первого разряда регистра 5 устанавливается потенциал низкого логического уровня (фиг. 2и), на выходе второго разряда - потен5 циал высокого логического уровня (фиг. 2к), на выходе третьего разряда - потенциал низкого логического уровня (фиг. 2л), а на . выходах четвертого и пятого разрядов - потенциал высокого логического уровня (фиг.

0 2н, п). .При этом, с выходов 1..,п регистра сдвига 5 на соответствующие входы п-вхо- дового мажоритарного блока 6 поступает параллельный код, например, код 01011 (фиг.2и,х, л,м, н), обеспечивающий установ5 ку на выходе мажоритарного блока 6 потен. ци.ал а высокого1 логического уровня,

соответствующего логической единице (фиг.

2П). :.,.- ,.

Выходной импульс (фиг. 2) второго бло0 ка задержки 9, поступая на динамический С-вход Д-триггера 7, на Д-вход которого поступает сигнал логической единицы (фиг. 2п), обеспечивает установку на выходе этого Д-триггера потенциала высокого логическо5 го уровня (фиг. 2т).

Сигнал логической единицы, формируемый на выходе Д-триггера 7, осуществляет устано вку в еди нич н оё состоя н ие у п ра в л я ю- щего RS-триггерэ, 11, выходной сигнал (фиг.

0 2ж) которого обеспечивает запуск генератора тактовых импульсов 12. Генератор тактовых импульсов 12 вырабатывает импульсы длительностью , например, мкс, с частотой fT, например, с частотой

5 кГц, равной частоте следования элементарных посылок передаваемого дискретного сигнала. Выходные импульсы (фиг. 2з) генератора тактовых импульсов 12, поступая через элемент ИЛИ 3 на вход генератора

0 серий импульсов 4, обеспечивает его периодический запуск через интервалы времени Тт, например, Тт 31,25 мкс. При поступлении каждого тактового импульса генератор серии импульсов 4 вырабатывает серию им5 пульсов (фиг. 2е), обеспечивающую последовательную запись в n-разрядный регистр сдвига 5 сигнала (фиг. 2д), поступающего ил его информационный Д-вход.

При передаче по каналу связи сигнала логического нуля суммарная длительность

сигналов низкого логического уровня во входном сигнале регенератора, содержащем импульсные помехи, превышает суммарную длительность сигналов высокого логического уровня, обусловленных помехами в канале связи, вследствие чего, по окончании соответствующей серии из п импульсов, число нулей в выходном параллельном коде регистра сдвига 5 превышает число единиц.

При этом, с выходов 1 ...п регистра сдвига 5 на соответствующие входы п-входового мажоритарного блока 6 поступает параллельный код, например, код 10100 (фиг. 2 и, к, л, м, н),обеспечивающий установку на выходе мажоритарного блока 6 потенциала низкого логического уровня (фиг. 2п), а соответствующий выходной импульс (фиг. 2р) второго блока задержки 9 обеспечивает установку потенциала логического нуля (фиг , 2т) на выходе Д-триггера 7.

Таким образом, по .окончании каждой серии из п-импульсов в п-разрядном регистре сдвига 5 фиксируется код, число единиц в котором определяется суммарной дли-; тельностью сигналов высокого логического уровня, а число нулей - суммарной длительностью сигналов низкого логического уровня в искаженном входном сигнале регенератора. Если число единиц в соответствующем параллельном коде,характеризующем входной сигнал регенератора, превышает число нулей щ п0, на выходе п-входового мажоритарного блока 6 устанавливается сигнал, логической единицы, а если число нулей в этом коде превышает число единиц ni n0. то на выходе мажоритарного блока 6 устанавливается сигнал логического нуля.

Выходные импульсы (фиг. 2р) второго блока задержки 9 обеспечивают фиксацию значений выходного сигнала мажоритарного блока б в Д-триггере 7, на выходе которого формируется цифровой регенерированный сигнал (фи. 2т), не имеющий краевых искажений, дроблений и ложных импульсов.

По окончании передачи дискретного сигнала на вход регенератора, поступают только импульсы, обусловленные помехами в канале связи. При этом, выходные импульсы генератора тактовых импульсов 12, поступая через элемент ИЛИ 3, продолжают осуществлять периодический запуск генератора серии импульсов 4. При отсутствии входного сигнала по окончании каждой серии из п импульсов на выходе мажоритарного блока б устанавливается потенциал низкого логического уровня, обеспечивающий наличие потенциала низкого логического уровня на выходе Д-триггера 7.

Выходной сигнал Д-триггера 7 низкого логического уровня разрешает работу счет- 5 чика 7, осуществляющего подсчет числа тактовых импульсов, соответствующих тактовым интервалам, в течение которых на выходе Д-триггера 7 непрерывно сохраняется сигнал логического нуля. При поступле10 нии на счетный С-вход счетчика 10 числа М тактовых импульсов, например, , соответствующих, следующим подряд/сигналам логического нуля, на единицупрёвышающе- го максимально возможное число N. напри15 мер, , следующих подряд, тактовых интервалов логического нуля-в передаваемом сигнале, на выходе счетчика 10 формируется положительный импульс (фиг. 2с), обеспечивающий сброс в исходное состоя0 ние-управляющего RS-триггера 11. При

этом, на инверсном выходе управляющего

RS-тригера 11 устанавливается потенциал

высокого логического уровня, запречцаю щий подсчет счетчиком 10 тактовых импуль5 сов и разрешающий работу одновибратора 2, подготавливая тем самым ре-генератор к регенерации нового принимаемого дискретного сигнала.

Эффективность предлагаемого изобре0 тения состоит в том, что путем введения в цифровой асинхронный регенератор дискретных сигналов, содержащий детектор уровня, генератор тактовых импульсов, счетчик, Д-триггер, RS-триггер, одновибра5 тор и элемент ИЛИ, двух блоков задержки, мажоритарного блока, генератора серии импульсов и регистра сдвига достигается увеличение помехоустойчивости регенератора. Увеличение помехоустойчивости

0- регенератора при наличии на его входе потока импульсов помех обеспечивается тем, что в каждом ци:кле анализа входного сигнала серия из п-импульсов, поступающая на тактовый С-вход п-разрядного регистра

5 сдвига обеспечивает полную смену его содержимого, исключая возможность накопления в регистре логических сигналов от импульсов помех, а, следовательно и воз можность формирования ложных сигналов

0 на выходе регенератора.

Кроме того, увеличение помехоустойчивости регенератора обусловлено также выполн ением детектора уровня в виде последовательно соединенных фильтра

5 нижних частот и порогового блока, обеспечивающих уменьшение вероятности ложных запусков регенератора импульсами помех и его переключения в режим анализа входного сигнала при отсутствии факта передачи дискретного сигнала по каналу связи. :-,;. . ч

Точность воспроизведения в выходном сигнале регенератора временных интервалов передаваемого дискретного сигнала определяется только точностью соответствия частоты генератора тактовых импульсов тактовой частоте передаваемого дискретного сигнала и может быть, при использовании кварцевой стабилизации, очень высокой.

Обладая более высокой помехоустойчивостью и обеспечивая высокую точность воспроизведения временных интервалов передаваемого дискретного сигнала, предложенный регенератор, содержащий 12 блоков и элементов, является значительно более простым по сравнению с прототипом по автхв.№1241486, содержащим 20 блоков и элементов.;

Более высокая помехоустойчивость предложенного регенератора, по сравнению с прототипом и базовым объектом, при использовании этого регенератора в приемных устройствах телеуправления и телекон- троля, обеспечивает увеличение надёжности дистанционного;управлений и контроля, а при использовании в приемных устройствах цифровой связи - увеличение дальности связи.

Ф о р м ул а и з о б р ете н и я

1. Цифровой асинхронный регенератор дискретных сигналов, содержащий детектор уровня, генератор тактовых импульсов, счетчик, Д-трИггер, выход которого является выходом регенератора, входом которого является вход детектора уровня, и последовательно соединенные RS-триггер, одновиб- ратор и элемент ИЛИ, отличающийся тем, что, с целью повышения помехоустойчивости, введены два блока задержки, мажоритарный блок, генератор серии импульсов и регистр сдвига, информационный и тактовый входы и выходы которого соединены соответственно с выходом первого блока задержки, вход которого подключей к входу детектора уровня, с выходом генератора серии импульсов, к входу которого подключен выход элемента ИЛИ, и с входами мажоритарного блока, выход кото- рогр подключен к информационному входу

Д-три гера, динамический вход которого соединен с выходом второго блока задержки, к входу которого подключен выход элемента ИЛИ, и с тактовым входом счётчика, управляющий и установочный входы и выход которого соединены соответственно с инверсным выходом RS-триггера, с выходом Д-трйггёра и R-входом RS-триггера, 5-вход и прямой выход которого срединены соответственно с выходом Д-триггера и с выходом генератора тактовых импульсов, выход которого подключен к второму входу элемента ИЛИ, при этом выход детектора уровня соединен с пусковым входом одновибратора. I. ..-..-: : .

2. Регенератор дискретных сигналов по п.1, от л и ч а ю щ и и с я тем, что детектор уровня содержит1 последовательно соединенные фильтр нижних частот и пороговый блок, выход которого является выходом детектора уровня, входом которого является вход фильтра нижних частот.

I

a I

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных последовательностей | 1985 |

|

SU1298868A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Формирователь импульсов | 1987 |

|

SU1492458A1 |

| Устройство синхронизации с м-последовательностью | 1984 |

|

SU1218484A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2270527C1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1985 |

|

SU1241486A1 |

| Устройство для корреляционного приема фазоманипулированных псевдослучайных сигналов | 1984 |

|

SU1252964A1 |

| Дуплексная система передачи данных с временным разделением сигналов | 1990 |

|

SU1782336A3 |

Использование: регенерация дискретных сигналов, передаваемых по физическим линиям связи. Сущность изобретения: регенератор содержит детектор уровня 1, одновибратор 2, элемент ИЛИ 3. генератор серии импульсов 4,регистр сдвига 5, мажоритарный блок 6, Д-триггер 7, блоки задержки 8, 9, счетчик 10, RS-триггер 1.1, генератор тактовых импульсов 17.1 -2-3-4-5- 6-7, 1-8, 8-5, 11-12-3, 11-2, 11-10, 3-9-10, 9-7, 10-11, 7-10, 7-11, Повышение помехоустойчивости достигается за счет того, что в каждом цикле анализа входного сигнала длительность из п импульсов, поступающих на тактовый вход, обеспечивает полную смену его содержимого, исключая возможность накопления логических сигналов от импульсов помех. Устройство по п. 2 формулы отличается выполнением детектора уровня 1.1 з.п. ф-лы, 2 ил.

«I

Тт

ЦП ПППП ПППППЛП ППП P ,П ППП QJL

-H Tr N

in ппппп пгппя п ппп п п ппп

I I .. ПП П ПППП

г.

л I

I. . -..

п п

Редактор

Составитель В.Романов Техред М.Моргентал

J

i ч

i

i

П ПП П| П ПП1П П П

I --, ., ;--f ,

I - I I I I ИПОЛ ГОРЛЙП

I

п л п

I t

an

п п

I I

П П-П-ПП

I I OR flJ1L

Фиг.2.

Корректор О.Кравцова

| Цифровой асинхронный регенератор дискретных сигналов | 1985 |

|

SU1241486A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-01-15—Публикация

1990-07-09—Подача