JL

&0

о:

00

01

Изобретение относится к преобразовательной технике и может быть использовано в системах электропитания аппаратуры связи и вычислительной техники.

Цель изобретения - повьшение надежности точности работы преобразователя за счет исключения сбоев, а также за счет получения на его вы- ходах взаимоинверсных парных импульсов.

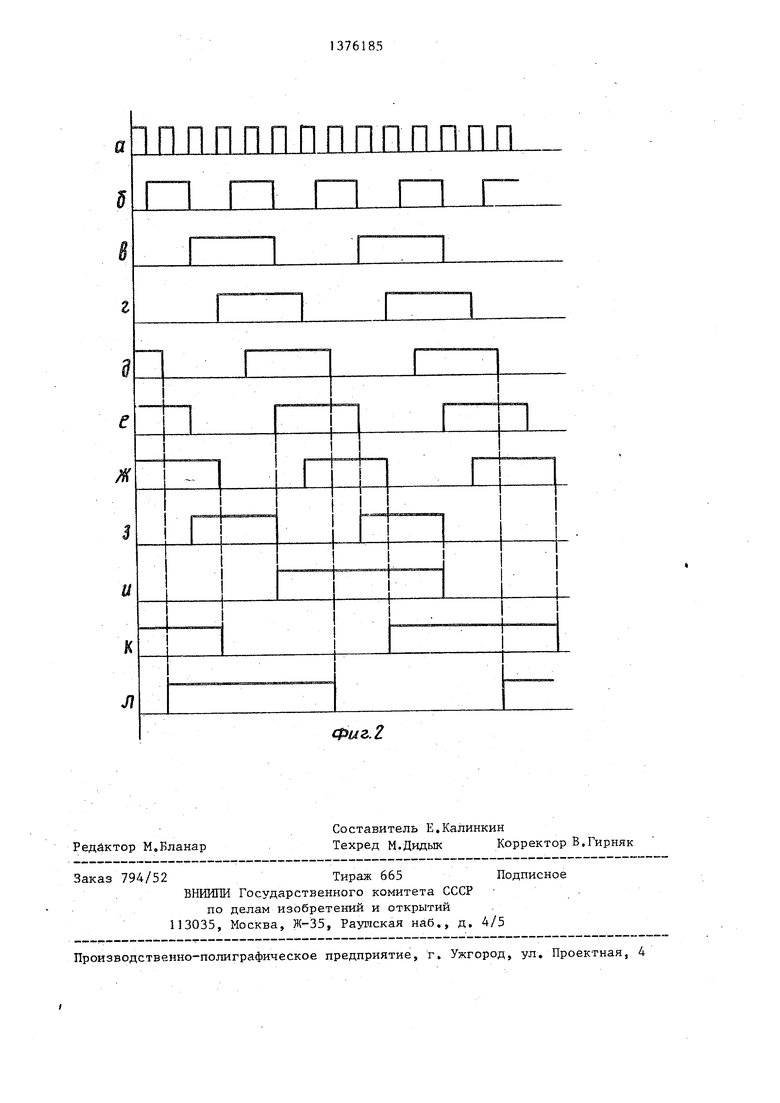

На фиг.1 приведена принципиальная схема преобразователя; на фиг.2- эпюры напряжений в различных точках его.

Преобразователь однофазного напряжения в трехфазное содержит последовательно соединенные однофазный источник (задающий генератор) 1 и делитель 2 частоты на три, делитель 3 частоты на два, включен между делителем 2 частоты на три и фазосдви- гающим блоком 4, последний состоит из универсального четырехразрядного сдвигающего регистра 5, собранного на микросхеме, инвертора 6 и трех lK-триггерах 7-9, собранных на микросхемах. Тактовый вход регистра 6 соединен с выходом генератора 1 импуль сов, информационный вход г с выходом делителя 3 частоты на два, выход третьего разряда регистра 5 через инвертор 6 соединен со счетным входо первого 1К-триггера 7, выход четвер- того разряда - со счетным входом второго 1К-триггера 8, выход второго разряда - со счетным входом третьего 1К-триггера 9, на 1К-входы которых подан уровень логической 1, а выхо ды 1К-триггеров 7-9 являются выходами фаз преобразователя.

Преобразователь однофазного напряжения в трехфазное также содержит блок 10 контроля правильности чередования фаз,.который содержит IK- триггер 11 и трехвходовую схему И-НЕ входы которой соединены соответственно с прямыми выходами первых двух 1К-триггеров 7 и 8 и с инверсным выходом третьего 1К-триггера 9 фазо- сдвигающего блока 4, а выход соединен с R-входом 1К-триггера 11, счетный вход которого соединен с выходом делителя 3 частоты на два, на 1-вход подан уровень логической 1, на К- вход - уровень логического 0 прямой выход триггера И соединен с R

с

10

15

20 25 30 35 40

с

50

5

выходами триггеров 7-9 фазосдвигаю- щего блока 4, а инверсный выход с V-входом регистра 5.

Преобразователь однофазного напряжения в трехфазное работает следующим образом.

Однофазный источник 1 генерирует импульсы с частотой, которая должна быть в 12 раз выше необходимой выходной частоты преобразователя (фиг.2а). После делителя частоты 2 частота следования импульсов уменьшается в три раза (фиг.2б), а после делителя 3 частоты - еще в два раза (фиг.2в).

Делители частоты строятся по стандартной схеме на 1К-триггерах.

Импульсы с делителя 3 частоты подаются на информационный вход сдвигающего регистра 5, на тактовый вход которого поданы импульсы с источника однофазного напряжения. С выхода каждого разряда сдвигающего регистра 5 можно получать импульсы той же частоты, которая подается на информационный вход, но сдвинутые после каждого следующего разряда на период импульсов, поступающих на тактовый вход. Эпюры напряжений со всех разрядов регистра 5 приведены соответственно на фиг.2 г-ж.

Импульсы с третьего разряда регистра 5 (фиг.2е) поступают на инвертор 6, с выхода которого инвертированные импульсы (фиг,2з) поступают на счетный вход триггера 7, который включен по схеме обычного счетного триггера. С выходов триггера 7 снимается пара взаимоинверсных импульсов , являющаяся выходом первой фазы преобразователя.

На фиг.2и показаны импульсы, снимаемые с прямого выхода триггера 7,

Импульсы с четвертого разряда регистра 5 (фиг.2ж) поступают на счетный вход триггера 8, с выходов которого снимается пара взаимоинверсных импульсов, являющихся выходом второй фазы преобразователя.

На фиг.2к показаны импульсы, снимаемые с прямого выхода триггера 8.

Импульсы с второго разряда регистра 5 (фиг.2д) поступают на счетный вход триггера 9, с выходов которого снимается пара взаимоинверсных импульсов, являющихся выходом третьей фазы преобразователя, причем импульсы по аналогии с первыми двумя фазами снимаются с противоположных выходов. На фиг, 2л показаны импульсы с инверсного выхода триггера 9.

При сдвиге фаз, равном 120°{фиг.2и л) , на всех входах схемы И-НЕ 12 никогда не присутствует одновременно уровень логической 1 и с выхода схемы И-НЕ 12 на R-вход триггера поступает уровень логической 1, При поступлении на счетный вход триггера 11 импульсов с выхода делителя 3 (фиг.2в) он постоянно выдает с прямого выхода уровень логической 1, а с инверсного вьтода - уровень логи ческого О. Это появоляет регистру 5 и триггерам 7-9 работать в нормальном режиме.

При сбое хотя бы одной из фаз импульс с выхода соответствующего триг гера фаэосдвигающего блока 4 сдвигается на 180°, Это может произойти из-за отсутствия начальной установки триггеров 7-9 или при прохождении помехи по цепям питания.

Иной сдвиг невозможен, так как регистр сдвигают только на период тактируемого импульса, следовательно, соотношение по времени между импульсами на выходах его разрядов все время сохраняется и сбой может произойти за счет ложного переключения какого-либо из триггеров 7-9.

При таком сбое на входах схемы И-НЕ 12 появляется период времени, при котором на всех ее входах присутствует уровень логической 1, при этом с ее выхода и на R-вход триггера 1I постлтает импульс с уровнем логического О, которьА ус- танавливает его в состояние, при котором на прямом выходе устанавливается уровень логического О, а на инверсном - логической 1, Это приводит к установке триггеров 7-9 в состояние нуля по прямым выходам (начальная установка) и записи нулевого состояния в триггеры разрядов регистра.

Такое состояние сохраняется до прихода спадающего фронта импульса с выхода делителя 3 на счетный вход триггера 11, который переключается в первоначальное состояние, разрешая работу преобразователя,

Использование изобретения по сравнению с известным преобразователем позволяет существенно повысить точность и надежность работы преобразователя за счет исключения сбоев в фа зосдвигающем блоке, а также расширить область применения за счет возможности использования двухтактного усилителя мощности.

Формулаизобретения Преобразователь однофазного напряжения в трехфазное, содержащий последовательно соединенные генератор импульсов -и трехкратный делитель частоты, фазосдвигающий блок и инвертор отличающийся тем, что, с целью повьтения надежности и точности, в него введены блок контроля правильности чередования фаз, содержащий 1К-триггер и трехвходовой элемент И-НЕ и двухкратный делитель частоты, включенный между трехкратным делителем частоты и фазосдвигающим блоком, который выполнен на универсальном сдвигающем четырехразрядном регистре и трех 1К-триггерах, при этом тактовый вход регистра соединен с выходом генератора импульсов, информационный вход с выходом двухкратного делителя частоты, выход третьег разряда регистра через инвертор соединен со счетным входом первого IK- триггера, выход четвертого разряда регистра со счетным входом второго 1К-триггера, выход второго разряда регистра со счетным входом третьего НС-триггера, 1К-входы всех триггеров подключены к клемме для подачи сигнала с уровнем логической единицы, выходы 1К-триггеров являются выходами преобразователя, а входы трехвхо- дового элемента И-НЕ соединены соответственно с прямыми выходами первых двух 1К-триггеров и инверсным выходо третьего 1К-триггера фазосдвигающего блока, выход элемента И-НЕ соединён с В-входом 1К-триггера блока контроля правильности чередования фаз, вход которого соединен с выходом двухкратного делителя частоты, 1-вход подключен к клемме для подачи сигнала с уровнем логической единицы К-вход - к клемме для подключения сигнала с уровнем логического нуля, прямой выход триггера соединен с R входами всех триггеров фазосдвигающего блока, а инверсный выход - с входом сброса регистра в нулевое состояние.

1ППППППППППППП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Многоканальное устройство для управления вентильным преобразователем | 1990 |

|

SU1777216A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для управления @ -фазным автономным инвертором напряжения | 1983 |

|

SU1089753A1 |

| Устройство для управления преобразователем постоянного напряжения в квазисинусоидальное с промежуточным высокочастотным преобразованием | 1981 |

|

SU1297198A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1983 |

|

SU1144174A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

Изобретение относится к электротехнике и мохет быть использовано в статических преобразователях. Цель изобретения - повьшение точности и надежности. При нарушении сдвига фаз появляется интервал времени,когда на прямых выходах триггеров 7,8 и инверсном выходе триггера 9 присутствуют уровни логической единицы, что является запрещенным состоянием. Три единицы вызывают появление логического нуля на выходе схемы 12, после чего триггер 11 устанавливается в состояние О. На R-входах триггеров 7, 8, 9 сигнал О, а на V-входе регистра 6 - сигнал 1, пока на С-вход триггера 11 не приходит задний фронт импульса, после чего состояние триггера изменяется и не реагирует на импульсы на счётном входе. За время присутствия сигнала О на Е-входах триггеров 7, 8, 9 и сигнала 1 на V-входе регистра 6 происходит их начальная установка и счет начинается заново, устраняя тем самым ошибку в чередовании фаз. 2 ил. i (Л

ж I

Фиг.2

n

| Преобразователь однофазного напряжения в трехфазное | 1983 |

|

SU1112503A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-02-23—Публикация

1986-09-30—Подача