1

Изобретбн-ие относится к вычислительной техднке и автоматике.

Известен триггер с неразрушаемой памятью, содержащий статический триггер, ячейку памяти, устройство перезаписи и ф-ормирователь Наиряжения иитания.

Предлагаемый триггер отличается от известного тем, что с целью повышения быстродействия в него дополнительно введены формирователь импульса считывания, формирователь импульса установки исходного состояния, три схемы совпадения. Ячейка памяти выполнена на феррит-транзисторной ячейке, а устройство перезаписи содержит оитрон, резистор, два усилителя, RC-цепочку и два ключа, Причем к каждому выходу статического триггера подсоединен вход одной из двух схем совпадения, вторые входы которых соединены с выходом ключа устройства перезаписи, его вход соединен со средней точкой делителя, .образованного резистором и фотодиодом оптрона, светодиод оптрона подсоединен КО входу формирователя напряжения питания; к выходу каждой схемы совпадения подсоединена через RC-цепочку и усилитель обмотка феррит-транзисторной ячейки, причем одна началом, другая - концом, а третья обмотка включена в нагрузочную деиь другого ключа устройства перезаписи, вход которого соединен с выходом формирователя им2

пульса считывания и с одним из входов третьей схемы совпадения, второй вход которой соединен с выходом усилителя ф PPIT транзисторной ячейки, а выход-с единичным выходом статического триггера.

Вход формирователя импульса считывания соединен с выходом формирователя импульса установки исходного состояния и входом статического триггера.

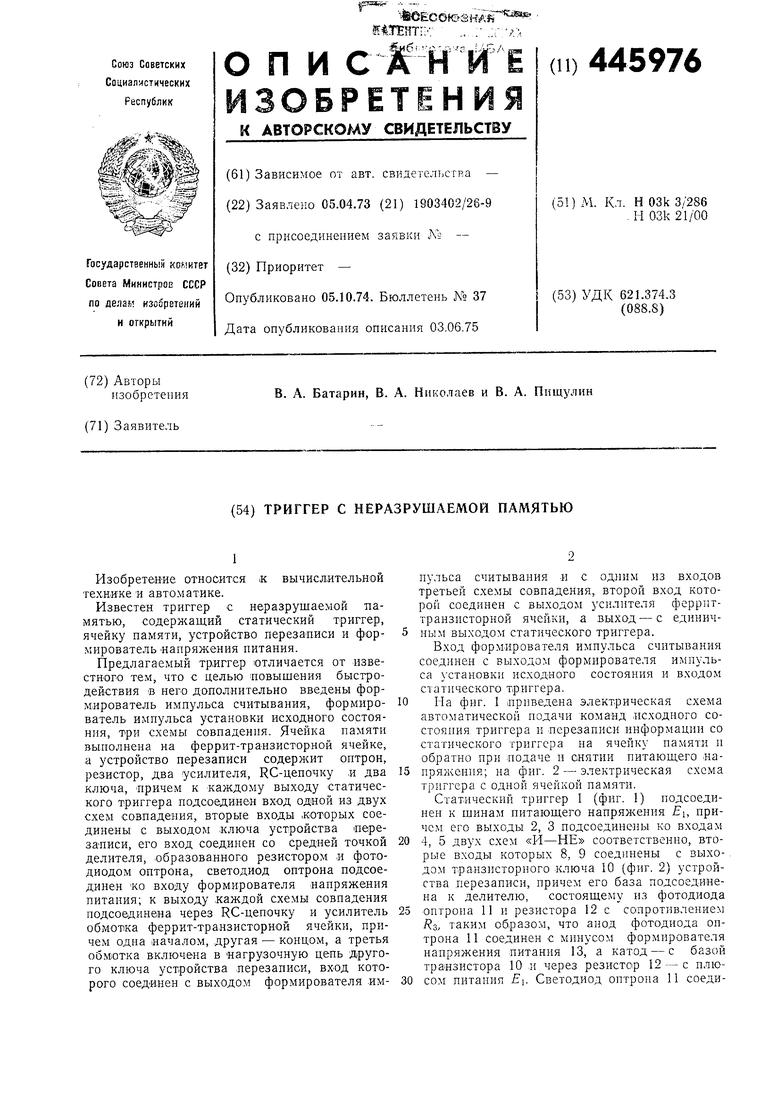

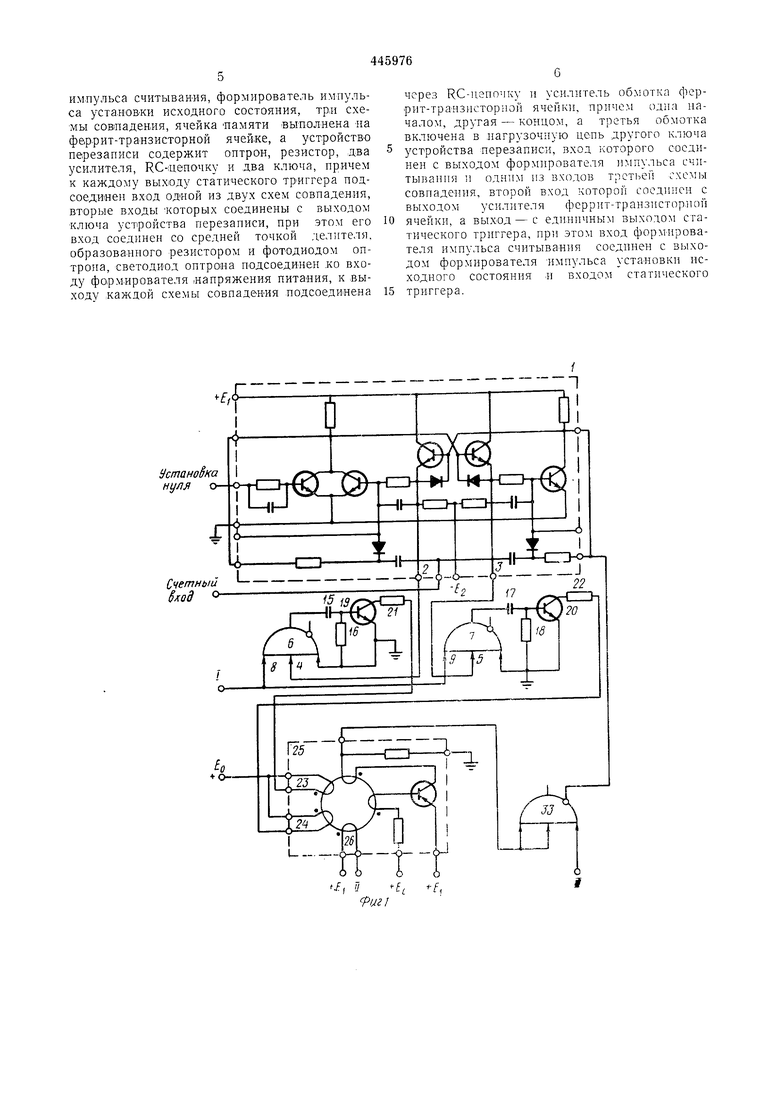

Па фиг. 1 приведена электрическая схема автоматической подачи команд исходного состояния триггера и перезаписи информации со статического триггера на ячейку памяти и обратно при подаче и снятии питающего напряжения; на фиг. 2 - электрическая схема триггера с одной ячейкой памяти.

Статический триггер 1 (фиг. I) подсоединен к шинам питающего напряжения EI, причем его выходы 2, 3 подсоединены ко входам

4, 5 двух схем «И-ПЕ соответственно, вторые входы которых 8, 9 соединены с выходом транзисторного ключа 10 (фиг. 2) устройства перезаписи, причем его база подсоединена к делителю, состоящему из фотодиода

оптроиа 1 и резистора 12 с сопротивлением RS, таким образом, что анод фотодиода оитрона И соединен с минусом формирователя напряжения питания 13, а катод - с базой транзистора 10 и через резистор 12-с илюсом питания EI. Светодиод онтрона 11 соединен анодом с плюсом первичпоп) питания L,, а катод через резистор 14 - с минусом с.. Вы ходы схем «И-НЕ 6 и 7 через цепочку, состоящую из коиденсатора 15 и резистора 16, и Цепочку, состоящую из копденсатора 17 н резистора 18, подсоединепы к базам Т|ра-нз1ь стороз 19 и 20, причем их коллекторы через реЗИсторы 21, 22 подсоединены к обмоткам 23 и 24 ячейки па.мяти 25 ооответстзеппо, так что конец обмотки 24 подсоедииеп к коллектору траизистора 20 через резистор 22, а пачало :обмотки 23 подключеио через резне гор 21 1К транзистору 19, другие котщы обмоток соедннены с плюсом fp формирователя напряжедия -питания 13. Начало обмотки 26 ячейки памяти 25 иодключепо через резиетор 27 ключа устройства нерезаинси (фиг. 2) к коллектору транзистора 28 этого ключа, база транзистора 28 через дифференцирующую цепочку, состоящую из конденсатора 29 и резистора 30, подсоединена к выходу формирователя импульса считывания 3 и через диод 32 - к одному из входов схемы «И-НЕ 33 (фиг. I), второй вход которой соединен е выходом 2 транзистора ячейки памяти. Выход схемы «И-НЕ 33 связан с праЕилм ввьходом статического триггера 1. Формирователь импульса считывания 3 соединен с катодом диода 34, анод которого через дифференцируюн1ую ценочку, состоящую из конденеатора 35 и резнстора 36, соединен с выходом формирователя установки исходного состояния 37, вход которого подключен к плюсу конденсатора 38 интегрирующей цепочки, состоящей из копденсатора 38 и резистора 39, причем эта цепочка, формирователь установки исходного состояния, формирователь импульса считывания 31, ключ 10, обмотка 26 н выходной транзистор ячейки 1пам.яти 25 включены на питание EI.

Схема триггера с неразрушаемой -памятью работает следующим образом.

Так как применение статических триггеров в нриборах обычно связано с нспользованием формирователя напрял ения питания, состоян;его из стабилизатора, преобразователя, выпрямителя и выходных RC-фнльтров, который создает разные номиналы напряжений питания триггеров, то при подаче ннтанпя на входные клеммы формирователя напряжение на нагрузке достигает номинального значения с задержкой в несколько миллисекунд, а при снятии питаиия напряжение на 1пагрузке оннжается до величины, при которой схема перестает функционировать нормально, за десятки миллисекунд. Таким образом, ири запитке формирователя напряжения литания 13 оптрон 11 обеспечивает закрытое состояние транзистора 10 устройства нерезацшси, и с его коллектора на входы схем «И-НЕ 6 и 7 поступает запреп1аюп;нй потенциал. Через 0,1-0,2 еек носле подачи питания ina формирователь напряжения питания 13 интегриру1С|щая -цепочка 38, 39 заряжается, н ерабатываст формирователь установки исходного состояния 37. На его выходе носле цепочки 35, 36 появляется положл-гтельный импульс, который через диод 40 поступает в пень установки нуля статического триггера 1. Одновремепно с этим через диод 34 запускается формирователь импульса считывания 31, по истечеиии 0,1-0,2 сек на базу транзистора 28 ключа устройства перезаписи приходит открывающи) импульс, и коллекторный ток этого TpaiisncTopa протекает через обмотку 26 феррит-транзисторной ячейки 25. Одновременно этот импульс поступает на один из двух входов схемы «Н-EIE 33. В зависимости от того, в каком состоянии находилась

ячейка 25, на выходе ее появляется или отсутствует импульс. Если нмнульс есть, он постунает затем на другой вход схемы «И-НЕ 33. В этолг случае, если ца обоих входах схемы «И-НЕ 33 одновременно нрисутствуют

импульсы, малое сонротивление открытых нереходов входящих в нее транзисторов щунтирует на время действия имиульсов выход правого плеча статического триггера I, благодаря чему -он устанавливается в положение, обратное исхолному. Нри отсутствии выходного сигнала с ячейки ламяти 25 схема совпадепня «И-НЕ 33 закрыта и не щунтирует правого нлеча триггера 1, который при этом остается в .состоянии, установленном нмну.льсом установки нуля. Таким образом, в точности воспроизводится логическая информация, за-цисанная до выключения напряжения питания. Все устройство нерезаниси и ячейка памяти не переключаются во время работы

статического триггера 1, а работают только 1 момент перезаписи информации.

При снятии питания со входных клем.м формирователя на нряже ия питания 13 светодиод оптрона 11 «гаснет в течение 0,2-0,3 мксек, а ном-инальное напряжение питания на выходе формирователя поддерживается за счет разряда емкос-гей сглаживающего фильтра еп,е в течение нескольких десятков миллисекунд. В течение этого времени транзистор

10 закрывается, н на его выходе образуется разрешающий потенциал. Он попадает на соответствующие входы 8, 9 схем «И-НЕ 6 н 7, на вторые входы которых 4, 5 постунает напряжение с правого и левого нлеч триггера

1, В этой схеме «Н-НЕ, на входе совпадают paзpeнJaюи иe потенциалы, из-меняе-1--с-я выходной -потенциал, который, дифференци.руяеь на цепочках 15, 16 или 17, 18, проходит через транзнетор 19 или 20 и лереводит ячейку па.мяти 25 в еоетояние +5ч или -В„.

П р е д 1 е -J- и 3 о б р е т е -п и я

Триггер с неразрушаемой памятью, содержащий статический триггер, ячейку памяти, устройство перезаписи и формирователь напряжения питания, о т л-и ч а ю щ и и с я тем, что, с целью новышепия быстродействия, в

него дополнительно В1зедены сЬормпрователь.

импульса считываНИЯ, формирователь импульса устааовки исходного состояния, три схемы совпадеЕия, ячейка памяти выполнена на фер.рит-траизисторной ячейке, а устройство перезаписи содержит оптрон, резистор, два усилителя, КС-щепочку и два ключа, причем к каждому выходу статического триггера подсоедине} вход одной из двух схем совпадения, вторые входы которых соединены с выходом ключа устройства перезаписи, при этом его вход соединен со средней точкой делителя, образованного резистором и фотодиодом оптрона, светодиОД оптрона подсоединен .ко входу формирователя |Напряжени.я питания, к выходу каждой схемы совпаде ния подсоединена

через RC-пепомку п усилитель обмотка феррпт-тра-нзнсторпой ячейки, причем одна пачалом, другая - концом, а третья обмотка включена в пагрузочную цепь другого ключа устройства перезаписи, вход которого соединен с выходом формирователя импульса считывания и одним из входов третьей схемы совпадения, второй вход которой соединен с В1з1ходом усилителя феррит-транзисторпой ячейки, а выход - с едипичным выходом статического триггера, при этом вход форМИрователя импульса считывания соедппен с выходом формирователя импульса установкп исходного состояния .и входом статического триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического адресования объектов | 1979 |

|

SU867819A1 |

| Устройство для индикации | 1972 |

|

SU448467A1 |

| Транзисторный преобразователь постоянного напряжения | 1986 |

|

SU1396227A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ЧАСТОТЫ И ОТНОШЕНИЯ ДВУХ ЧАСТОТ | 1971 |

|

SU294112A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Двоичный сумматор | 1972 |

|

SU439809A1 |

| ФЕРРИТ-ТРАНЗИСТОРНЫЙ ТРИГГЕР СО СЧЕТНЫМ ВХОДОМ | 1973 |

|

SU409355A1 |

| Генератор инфранизкочастотных импульсов | 1981 |

|

SU961104A1 |

| Устройство для определения междуфазных замыканий и замыканий на землю в сетях с изолированной нейтралью напряжением 6-10 кВ | 2022 |

|

RU2788035C1 |

| Устройство для управления тиристорами трехфазного импульсного источника напряжения | 1976 |

|

SU741385A1 |

9 иг

1

.- .-...J 11

i Г,

Т {.- i2 -

: M -t:j ::r li-ik

-Я i f -Ii

li U :-ii :И Г9

I

t-ial

..„.1

Устснобка нуля

Авторы

Даты

1974-10-05—Публикация

1973-04-05—Подача