Изобретение относится к радиоэлектронике, может быть использовано в приемных устройствах систем связи, радиолокации и радионавигации.

Известно устройство для синхронизации двоичной линейной рекуррентной последовательности, содержащее на входе коррелятор, состоящий из перемножителя, интегратора и порогового блока, выход которого соединен с запрещающим входом схемы «Запрет. Сигнальный вход этой схемы подключен к выходу генератора временных интервалов. Выход схемы «Запрет связан со входом переключателя, переключающего генератор опорной последовательности или в режим записи символов принимаемой последовательности, или в режим выработки опорной последовательности с фазой, определяемой символами принимаемой последовательности, записанными в регистр этого генератора. После переключения генератора в режим выработки опорной последовательности происходит анализ на наличие или отсутствие синхронизации. Продолжительность анализа обычно много больше времени загрузки регистра. Общее время на достижение синхронизации определяется числом попыток, каждая из которых включает время загрузки регистра и время анализа.

Для ускорения синхронизации предлагаемое устройство содержит дополнительный инвертор, соединенный последовательно с дополнительной схемой запрета, которые включены между информационным входом накопителя и его входом сброса. Запрещающий вход схемы запрета соединен с одним из выходов триггера переключателя. К выходу накопителя коррелятора подключен дополнительный пороговый блок (с порогом т k), выход которого соединен с другим входом триггера переключателя.

Для замыкания петли обратной связи генератора опорной последовательности, необходимо принять п т безошибочных символов подряд (п - число разрядов регистра сдвига генератора опорной последовательности, т - пороговое число, достижение которого фиксирует дополнительно введенный пороговый блок). При несовпадении символа принимаемой последовательности и символа с выхода схемы обратной связи в режиме поиска синхронизации накопитель сбрасывается, и счет начинается снова. Так повторяется до тех пор, пока не будет достигнут порог т. После этого петля обратной связи генератора опорной последовательности замыкается, и устройство переходит в режим подтверждения ее правильности по порогу k.

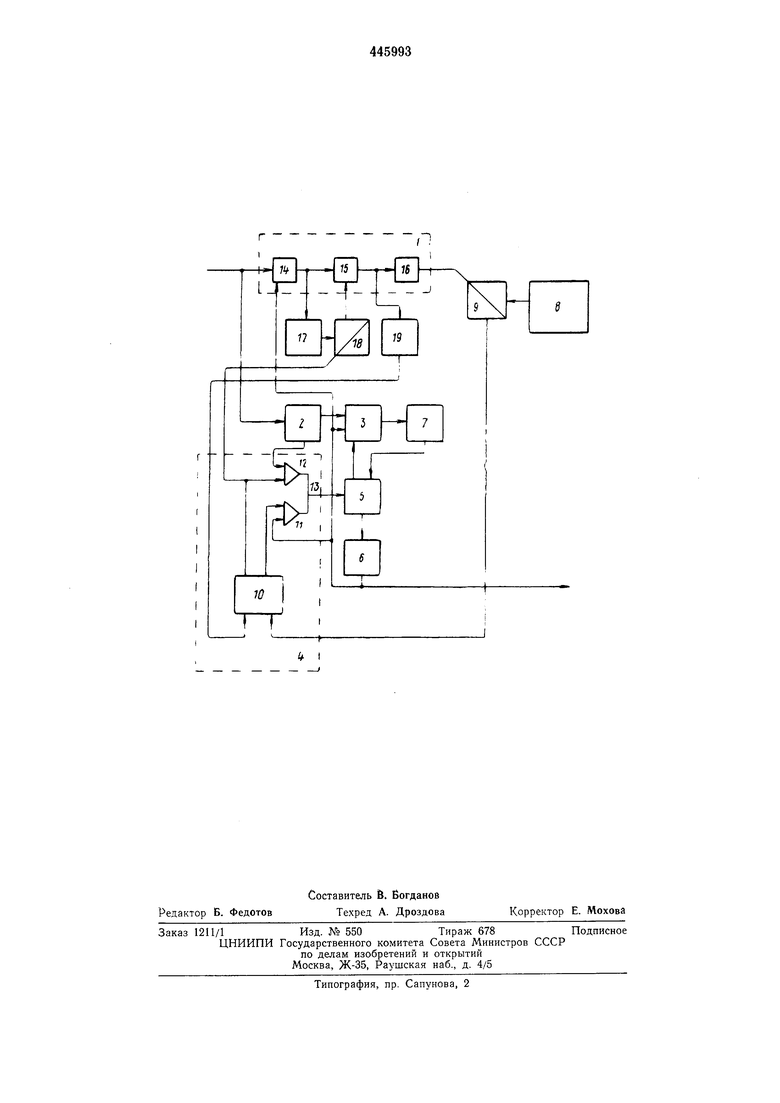

На чертеже приведена схема предлагаемого устройства. Вход устройства соединен со входом коррелятора 1 и через схему задержки 2 - со входом дифференциального коррелятора 3 и сигнальным входом нереключателя 4. Выход нереключателя соединен со входом регистра сдвига 5 на п разрядов, который подключен ко входу схемы обратной связи 6 и дифференциальному коррелятору 3 (элементы 5 и 6 образуют генератор опорной носледовательности). Выход схемы обратной связи 6 подключен ко второму входу дифференциального коррелятора 3, ко второму входу коррелятора 1 и ко второму сигнальному входу переключателя 4. Выход коррелятора 3 соединен со входом генератора тактовых импульсов 7, выход которого соединен с тактовым входом регистра 5. Выход регистра временных интервалов 8 соединен со схемой запрета 9, запрещающий вход которой соединен с выходом коррелятора 1. Выход схемы запрета подключен к унравляющему входу переключателя 4, состоящего из триггера с раздельными входами 10, схем совпадения 11 и 12 и схемы «ИЛИ 13. Коррелятор 1 состоит из последовательно соединенных перемножителя 14, накопителя 15 и порогового блока 16. Выход перемножителя 14, кроме того, соединен через инвертор 17 со входом дополнительной схемы запрета 18, выход которой подключен к шине сброса накопителя 15. Запрещающий вход схемы запрета соединен со входом триггера 10. Выход накопителя 15 через дополнительный пороговый блок 19 подключен ко второму управляющему входу переключателя 4. Выходная онорная последовательность снимается со схемы обратной связи 6. Работает устройство следующим образом. В момент включения устройства пороги k и m в пороговых блоках 16 и 19 не превыщены, и импульс с генератора временных интервалов 8 через открытую схему запрета 9 при помощи триггера 10 и схемы совпадения 12 открывает вход регистра сдвига 5 для символов принимаемой последовательности. Схема запрета 18, управляемая триггером 10, также открывается для прохождения через нее инвертированного сигнала с перемножителя 14 на щину сброса накопителя 15. Одновременно начинает работу дифференциальный коррелятор 3, который совместно с генератором тактовых импульсов 7 выполняет тактовую синхронизацию с принимаемой последовательностью. На выходе схемы обратной связи 6, подключенной к регистру 5, на каждом очередном такте приема формируется сигнал, определяемый рекурретной зависимостью символов данной последовательности. Для нроверки вьпюлняемости рекуррентного уравнения перемножитель 14 умножает символ выходного сигнала схемы обратной связи 6 на входной символ принимаемой последовательности. Для выявления неискаженного отрезка принимаемой последовательности длиной п т необходимо, чтобы рекурретное уравнение выполнилось т раз подряд после сброса накопителя 15. В этом случае сигнал с порогового блока 19 замыкает обратную связь генератора опорной М-последовательности (регистр 5 и схема обратной связи 6) с помощью переключателя 4. При этом в переключателе 4 триггер 10, опрокинувшись, снимает запрет со схемы совпадения И, через которую сигнал обратной связи поступает па схему «ИЛИ 13 и с нее на регистр 5. С этого момента регистр 5 и схема обратной связи 6 переходят в автономный режим работы. Начальная фаза вырабатываемой последовательности определяется л символами, записанными в регистр 5 в момент замыкания цепи обратной связи. Схема обратной связи 6 совместно с коррелятором 1 и дополнительными схемами 17-19 обнаруживают большинство комбинаций ошибок. Выигрыш во времени синхронизации получается благодаря тому, что генератор опорной последовательности включается только при отсутствии в его регистре искаженных символов принимаемой М-последовательности, что обнаруживается дополнительно введенными элементами. Нредмет изобретения Устройство для синхронизации двоичной линейной рекуррентной последовательности, содержащее генератор опорной последовательности, а на входе - коррелятор, состоящий из последовательно соединенных перемножителя, накопителя и порогового блока, выход которого подключен к схеме «Запрет, управляе.мой генератором временных интервалов, соединенной с одним из входов триггера переключателя, отличающееся тем, что, с целью ускорения вхождения в синхронизм, выход схемы «Запрет подключен непосредственно к одному из входов триггера переключателя, ко второму входу которого через дополнительный пороговый блок подключен выход наконителя, причем между информационным входом и вхоом сброса накопителя включены последоваельно соединенные инвертор и дополнительая схема «Запрет, к соответствующему вхоу которой подключен один из выходов тригера переключателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации м-последовательности с инверсной модуляцией | 1974 |

|

SU702534A1 |

| ВСЕСОЮЗНАЯ 1"ЛШТНО.Ш(кгт-ЯАя/ | 1973 |

|

SU374594A1 |

| Устройство синхронизации м-последовательности | 1974 |

|

SU554628A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| Устройство для синхронизации рекуррентных сигналов | 1975 |

|

SU542357A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 2002 |

|

RU2244384C2 |

| Устройство для синхронизации м-последовательностей с инверсной модуляцией | 1977 |

|

SU651493A2 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ ФАЗОМАНИПУЛИРОВАННЫХ КОДОВЫХ СИГНАЛОВ | 2002 |

|

RU2236086C2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ С ПОВЫШЕННОЙ СЛОЖНОСТЬЮ | 1999 |

|

RU2153230C1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

Авторы

Даты

1974-10-05—Публикация

1972-07-11—Подача