(54) УСТРОЙСТВО ДЛЯ ВЫБОРА СРЕДНЕГО ПО ВЕЛИЧИНЕ

ДВОИЧНОГО ; ЧИСЛА

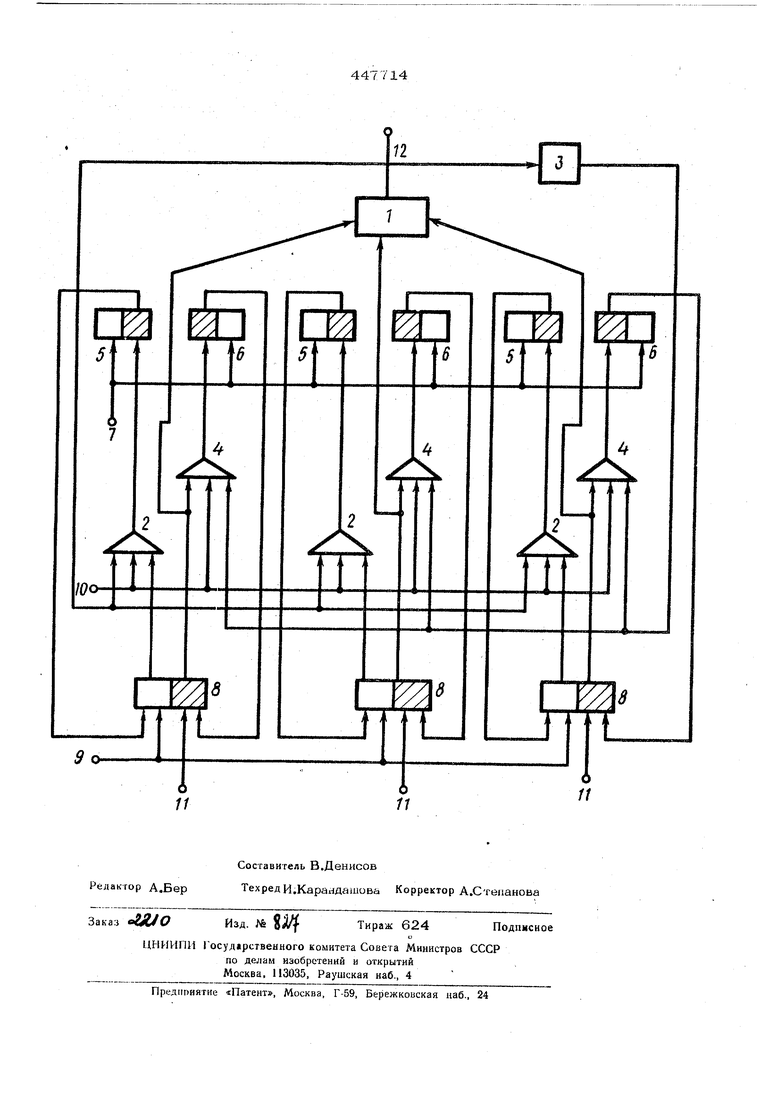

соответствует высокий потенциал, а нулю низкий. В- исходном состоянии после подачи сигнала по шинам 7 и 9 нулевые выходы триггеров 5, 6 и 8 имеют высокий ;потенциал, а единичные - шзкий. Асинхро но принятая информация запоминается на триггерах 8, с которых поступает на ма1жоритный элемент 1 и схемы И 2 и И. Герез время, определяемое максималь;ной рассинхронизадией каналов и включением триггеров 8, по шине сийхронизации 1О подается тактирующий сигнал, по которому происходит изменение состояний триггеров 5 выдачи иудей и триггеров 6 выдачи единиц. Съем информации с мажо- If.r. - .

т-арного элемента 1 производится в Момент появления сигнала на шине 10. ; Дальнейшую работу устройства рассмот рим на примере подачи на его входы произвольных чисел. Предположим, что на левый (по схеме) вход 11 устройства по-, дается число 1О11, на средний - число 1ООО, а на правый - число 0111. При подаче на входы 11 старших разрядов приведенных чисел едлнищз запоминаютсяна левом и среднем (по схеме) триггерах 8, с которых поступают на соответствующие входы мажоритарного элемента 1 и на соответствующие схемы И 4, в результате чего на выходе мажоритарного элемента 1 формируется единица, которая поступает на схемы И 2 и инВ9ртор 3. На выходе инвертора 3 формиру ется низкий потенциал, который запрещает срабатывание схем И 4. Левая и .средняя схемы И 2 закрыты низким сигналом с нулевых выходов триггеров 8, а правая схема И 2 под1отовле1ш к срабатыванию. При поступлении сигнала но шине 10 срабатывает правая схема И 2, которая устанавливает правый триппер выдачи нулей 5 в единичное состояние. Так как сигнал по шине 7 поступает один раз при установке устройства в исходное состояние перед приемом данного числа, то ттравый триггер 5 будет находиться в единичном состоянии на все время приема числа. Единичное состояние правого триг1 ера 5 выдачи нулей,безус,ловно удерживает правый входной триггер 8 в нулевом состоянии. В дальнейшем, независимо от то1ю, как инфррмация будет поступать по правому входу 11 правый триггер 8 будет нахошпъся в нулевом сослс ян11и и с единичного выхода его будет выдаваться низкий потенциал, который поступает на правый вход мажоритар;ног6 элемента 1 и запрещает срабатывание правой схемы И 4.

Единичное состояние правого триггера 5 выдачи нулей соответствует поступле- 5 нию минимального числа по правому входу 11. После поступления сигнала по шине 10 поступает сигнал по шине 9 и подготапаливает входные триггеры 8 к приему очередной цифры числа. Вслед за старшим

10 разрядом числа на входы 11 устройства

поступает следующий разряд числа (в данном случае соответствующий нулю во .всех разрядах). При этом состояние триггеров 5 выдачи нулей и триггеров 6

15 вьщачи единиц не изменится. Далее в .предварительно подготовленные сигналом по шине 9 .триггеры 8 поступает третья цифра. После срабатывания левого триггера на левом входе мажоритарного элемента 1 присутствует единичный , а на среднем и правом - нулевые сигналы. На выходе мажоритарного элемента 1 формируется нулевой сигнал, который запрещает срабатывание схем И 2, а черев инвертор

15 3 подготавливает к срабатыванию схемы И 4. Но разрешение на срабатывание схемы И 4 по другому входу поступает только на левую схему И 4 от единичного плеча левого триггера 8. С приходом сигнала по шине Ю срабатывает тол1зко левая схема И 4 и устанавливает левый трипер выдачи единиц б в единичное состояние, который в дальнейшем будет

безусловно, удерживать левый входной триг5 гер 8 в ешшичном состоянии независимо от вида информации, которая по ту1ШТ но левому входу 11. Единичное состояние левого триггера 6 выдачи единиц соотв:егствует поступлению максимального) числя по 0. левому входу 11. В дашэнейи1ем на выходе мажоритарного элемента 1 будут формироваться сигналы, соответствующие поступающим по среднему входу 11 числу 1 ООО, которое является средним по величине, т. е. 5 011К .

. Таким образом, устройство позволяет восстанавливать истинную ии|}юрмацию в каналах резервированного устройства.

Предмет изобретения

Устройство для выбора среднегх) по ве; -личине двоичного числа, содержащее вход,; ные триггеры, единичные выход-1 которых соединены с соответствуюишми входами мажоритарного элемента, выход которого iсвязан непосредственно с первыми входами схем И анализа нулей и через инвертор - с первыми входами схем И анализа единиц, и триггеры выдачи единиц и нулей, единичные входы которых соединены с выходами соответствующих схем И анализа единиц и нулей, о т л и ч а ющ е е с я тем, что, с целью упрощения устройства и расширения функщюнальных возможностей, в нем единичные и нулевые

6

выходы входных триггеров соединены со вторыми входами соответствующих схем И анализа единиц и нулей, нулевые входы - с единичными выходами триггеров выдачи нулей, а единичные входы - с едини 4Hbii.iii выходами триггеров выдачи единиц, причем третьи входы схем И ана ли за Нулей и единиц подключены к шине .синхронизации.

5

( I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выбора среднего по величине числа | 1981 |

|

SU1005336A1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ДОСТОВЕРНОЙ ИНФОРМАЦИИ | 1973 |

|

SU394790A1 |

| Устройство для выбора среднего по величине двоичного числа | 1975 |

|

SU603994A1 |

| Устройство для выбора достоверной информации | 1983 |

|

SU1141413A1 |

| Трехканальное устройство для выбора достоверной информации | 1975 |

|

SU595733A1 |

| Устройство для выбора среднего по величине двоичного числа | 1979 |

|

SU879591A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для синхронизации резервированного делителя частоты | 1981 |

|

SU1001104A1 |

| Многоканальное устройство для синхронизации | 1977 |

|

SU657430A1 |

| Мажоритарно-резервированное устройство | 1980 |

|

SU1032600A1 |

Z:

Авторы

Даты

1974-10-25—Публикация

1972-10-12—Подача