kepTOp ,входаых(, сигнало.в обратного кряэ инвертор числа, шина прямого кода, шина обратного кода, элемент ИЛИ числа, выход которого соединен со вторым ВХОДОМэлемента И выдачи числа, первый вход- с выходом элемента И обратного кода, второй-с выходом элемента И прямого кода, единичный вход Триггера анализа нулей соединен с выходом элемента ИЛИ выдачи нулей., первый вход которого соединен а выходом элемента И анализа нулей обратного кода, второй- с выходом элемента И анализа нулей, а единичный вход триггера анализа единиц соединен с выходом элемента ИЛИ выдачи единиц, первый вход которого соединен с элементом И анализа единиц обратного кода, второйс элементом И анализа единиц. Шина прямого кода подключена ко второму BXO ЮУ элемента И прямого кода, к третьему входу элемента И анализа нулей и к четвертому входу элемента И анализа единиц, а шина обратного кода подключена ко второму входу элемента И обратного кода, к третьему входу элемента И анализа нулей обратного кода и к четвертому входу элемента И анализа единиц обратного кода. Выход мажоритарного элемента соединен с первым входом элемента И анализа нулей обратного кода и через инвертор выходных сигналов обратного кода - с первым входом элемента И анализа единиц обратного кода, а каждый информационный вхо устройства соединен через инвертор чис ла с первым входом элемента И обратно™ го кода, с первым входом элемента И прямого кода, со вторым входом элемента И анализа нулей обратного кода и через инвертор входных сигналов обратного кода - с третьим входом элемента И анализа единиц обратного кода, причем, нулевой выход триггера анализа нулей соединен со вторым входом элемента И анализа единиц обратного кода.

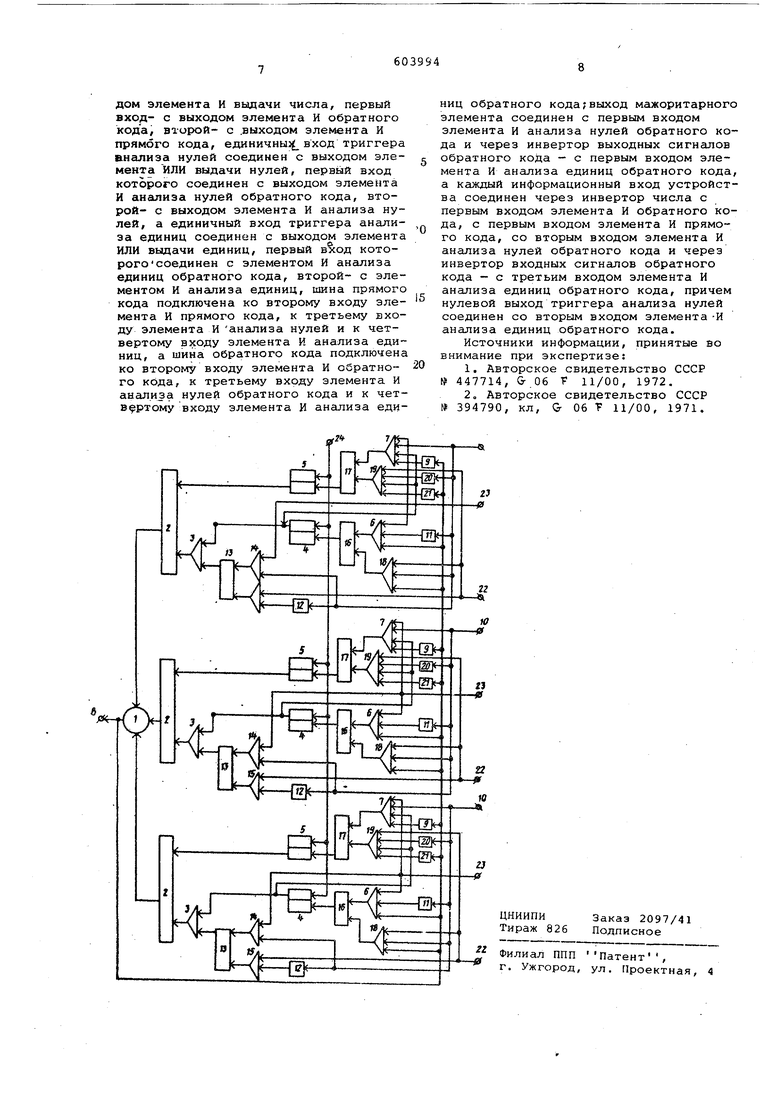

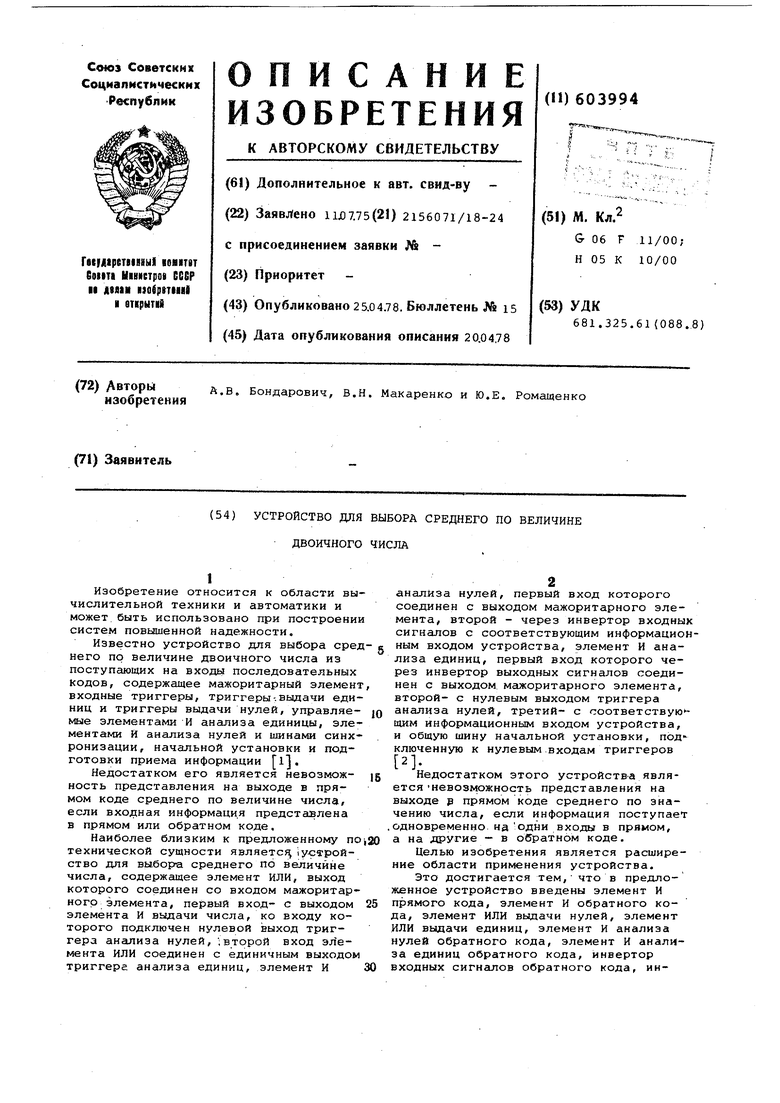

На чертеже представлена структурная схема устройства, например, на три входа (нижний, средний и верхний),

Предложенное устройство содержит MamopH TapHbaa элемент 1, элемент ИЛИ 2, элементы К 3 выдачи числа, триггеры 4 анализа нулей,, триггеры 5анапи за единиц, .элегченты И 6 анешиза нулей, элементы и 7анализа единиц, выход 8

устройства, инверторы 9 выходных сиг-:

налов, информационные входы 10, инвер торы 11 входных сигналов, инверторы 12 числа, элементы ИЛИ 13 числа, эле менгк и 14 прямого кода, элемейты,.И 15 Обратного кода, элементы или 16 выдачи нулей, элементы ИЯЙ 17 выдачи единиц, элементы И 18 анализа нулей обратного кода, элемент И 13 анал зза единиц обратного кода, инвертора 20 входных сигналов обратного кода, инаерторы 21 .выходных сигналов обрат

ного кода, шины 22 обратного кода, шины 23 прямого кода, общую для всех триггеров шину 24 начальной установки. Устройство для выбора среднего по

величине-числа работает следующим об

разом.

На информационные входьз 10 от соотвествующих каналов, информация которых обрабатывается предложенным устройством, подаются сигналы в последователь ном двоичном прямом или обратном коде, начиная со старших разрядов. Будем считать, что единице в разряде кода соответствует высокий потенциал, нулюнизкий.

В исходном достоянии после подачи сигнала по идане 24 начальной установки на нулевом выходе триггеров 4 анализа нулей присутствует высокий потенциал, а на единичном выходе триггеров 5 анализа единиц- низкий. При этом разрешено прохождение старших разрядов входных сигналов на входы мажоритарного элемента 1 при подаче сигнала по шине 23 прямого кода- апя единичных сигналов прямого ,кода, при подаче сигнала по шине 22 обратного кода- для нулевых сигналов обратного кода.

Дальнейшую работу устройства Рассмотрим на примере подачи на его входа произвольных сигналов.. Предполо жим, . что на нижний информационный вход 10 устройства подается прямой код 110111,на средний- обратный код 010100, а на верхний- обратный кол 100010, что со-, ответствует значениям двоичных чисел в прямом коде 11011, 10101.1 и 011101 соответственно.

При подаче на информационные входы 10 устройства старших разрядов приведенных кодов единичный сигнал левого канала и ..сигнал по левой шине 23 прямого кода приводят к срабатыванию левого элемента И 14 прямого кода. Выходной сигнал левого элемента И 14 прямого кода через -левый элемент ИЛИ 13 н единичный сигнал нулевого выхода левого триггера 4 анализа кулей приводит к срабатЕлванию левого элемента И 3 вьадачи -шсла, выход которого через нижний элемент ИЛИ 2 1;оступает на нижний вход мажоритарного элемента Д.

Нуль среднего кана.па через средний инвертор 12 числа и с-Ш-нел по средней 1иине 22 обратного кода при.водит к срабатыванию среднего з.лемевга И 15, обратного кода. ВЫ.ХОДНОЙ сигнал среднего элемента И 15 сбратыого кода через сре.дний элемент ИЛИ 13 чи:;ла и единичный сигн-ал нулевого вкхода среднего триггера 4 приводит к срабатыванию среднего элемента И 3 и .выдачи числа,выход которого через средний элемент ИЛИ 2 поступает на сре.дний вход мажоритарного элемента 1.

В результате появления сигналов на нижнем и среднем вхо..цах ма; оритарijozo элемента на выходе 8 усаройства появляется; единица, формируется стар-ший разряд выходного сигнала. Единица в старшем разряде выходного сигнала, единица в старшем разряде кода, поступившая на верхний информационный вход 10 устройства, и сигнал на первой шина 22 обратного -кода приводят к срабатыванию верхнего элемента И 18 анализа Егулей обратного кода, сигнал на Еыходе которого устанавлива ет в единичное состояние верхний триг гер 4 анализа нулей. На нулевом выходе упомянутого триггера появляется низкий потенциал, закрываются верхний элемеит Я 3 выдачи числа, верхний эле мент И 7 анализа единиц и вархний элемент И 19 анализа единиц обратного кода„С этого момента на верхнем входе мажоритарного элемэн.ха постоянно удерживается низки.н потенциал, 11езаЕИс;иг.5О от значений последующих разрядов кода поступающего на одноименный вход устройства. Срабатыва ше верхнего элемента И 18 анализа нулей обратного кода элемента И 6 анализа нулей при поступлении н,а верхний вход устг ойства пряi-Moro кода свидетельствует о том, что , поступаюгцее ка верхний вход 10 стройстБа, имеет каименьшее зна.чение 13 устройстве оно заманяется кодом с нулями во всех последующих. разрядах. - Вслэд за старшим разрядом на информационные входы 10 устройства подается следующий рязряд сигналов. Единица/ поступаютая на нижний информационный вход 10, проходит на нижний вход мажоритарного элемента. Однако на двух других его входах присутствуют нулевы сигналы, так что сигнал на выходе , 8 принимает нулевое значение. Выходной нулевой сигнал, поступа;ощий через нижний инвертор 9 выходных сигналов ,единичный сигнал обратного кода по нижнему- информационном, входу 10 и сигнал, поступаюсаий по нижней шине 23 прямот-о кода, приво.дят к срабатыванию нижнего 3J 8MeETa И 7 анализа единиц, сигна: на выходе которого устанавливает в е-ди:- ичное состояние -:ижний триггер 5 анализа единиц. На едннич-ном выходе этого триггера появляется высокий потенциал, который через нижний элемент ИЛИ 2 поступает на нижний вход мажоритарного элемента 1, С этого момент.а на нижнем выходе мажо ритарного эла1/,ента 1 будет постоянно Удерживаться высокий потенцйа. незави симости от значений последующих разря дов кодов, поступающих на одноименный вход устройства. Срабатывание нижнего элемента И 7 анализа едини; (нижнего элемента И 19 анализа единиц обратного кода при поступлении на нижний вход устройства информации в обратном коде) свидетельсвуст о том, что число, поступающее на верхний информационный вход 10 имеет наибольшее значение среди входных чисел. В устройс.тве оно заменяется прямым кодом с единицами но всех последующих разрядах. После прохождения первых двух разрядов входных сигналов на верхнем входе мажоритарного элемента 1 постоянно удерживается низкий потенциал, а на нижнем входе высокий потенциал. При таком распределении потенциалов на входах мажоритарного элемента значения последующих разрядов кода на выходе 8 соответствуют значениям одноименных разрядов прлмого кода и.ии обратным зиаченийм одысимекных разрядов обратного 5со,|да, пос1упаю:- его на средний информа1.и;окиь.й в.СОд 10, На выходе устройства формируется в прямом коде число 10101.1 у яьлл.ощееся сред-и-ш по вяличине сре.чи .)дных сигналов. Таким образом, предложенное устройство позволяет реализовать представление на выходе в прямом последовательном коде среднего по значению числа при при€;ме икформацки в прямом и обра(гном ьсоде, что расширяет область его применения. Формула изобретения Устройство для выбора среднего по еличинедвоичного числа, содержащее лемент ИЛИ, выход которого соединен о входом мажоритарного элемента, перЫЙ вход- с выходом элемента И выдаи числ.а, ко входу которого подключен улевой выход триггера анализа нулей, торой вход элемента ИЛИ соединен с единичнш выходом триггера анализа единиц,.элемент И анализа нулей, первый вход которого соединен с выходом мажорих-аркого элемента, второй - через инвертор вход( сигналов с соответст- вующим информационным входом устройст ва, элёмект И анализа единиц, первый вход которого через инвертор выходных сигналов соединен с выходом мажоритарного элемента, второй - с нулевым выходсхм триггера анализа нулей, третийс соответстЕующи --: информационным входом устройства, и общую шину начально установки, подключенную к нулевым вхо- дам триггеров, о т л и ч а ю щ е е с 5 тем, ЧТО; с целью расширения области применения, в негс введены элемент И прямого ргода, элемент И обратного код, элемент выдачи нулей, элемент ИЛИ выдачи единиц, элеглгэнт И анализа нулей обратного кода, элемент И анализа еди Е1ИЦ обратного кода, инвертор входных сигналов обратного кода, инвертор выходных сигналов обратного кода, инвертор числа, шина прямого кода, iLMna обратного кода, элемент ИЛИ числа, выход которого соединен со вторым вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выбора среднего по величине числа | 1981 |

|

SU1005336A1 |

| Устройство для выбора достоверной информации | 1983 |

|

SU1141413A1 |

| Устройство для выбора среднего по величине двоичного числа | 1979 |

|

SU879591A1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ДОСТОВЕРНОЙ ИНФОРМАЦИИ | 1973 |

|

SU394790A1 |

| Трехканальное устройство для выбора достоверной информации | 1975 |

|

SU595733A1 |

| Устройство для выбора среднего по величине двоичного числа | 1972 |

|

SU447714A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

Авторы

Даты

1978-04-25—Публикация

1975-07-11—Подача