1

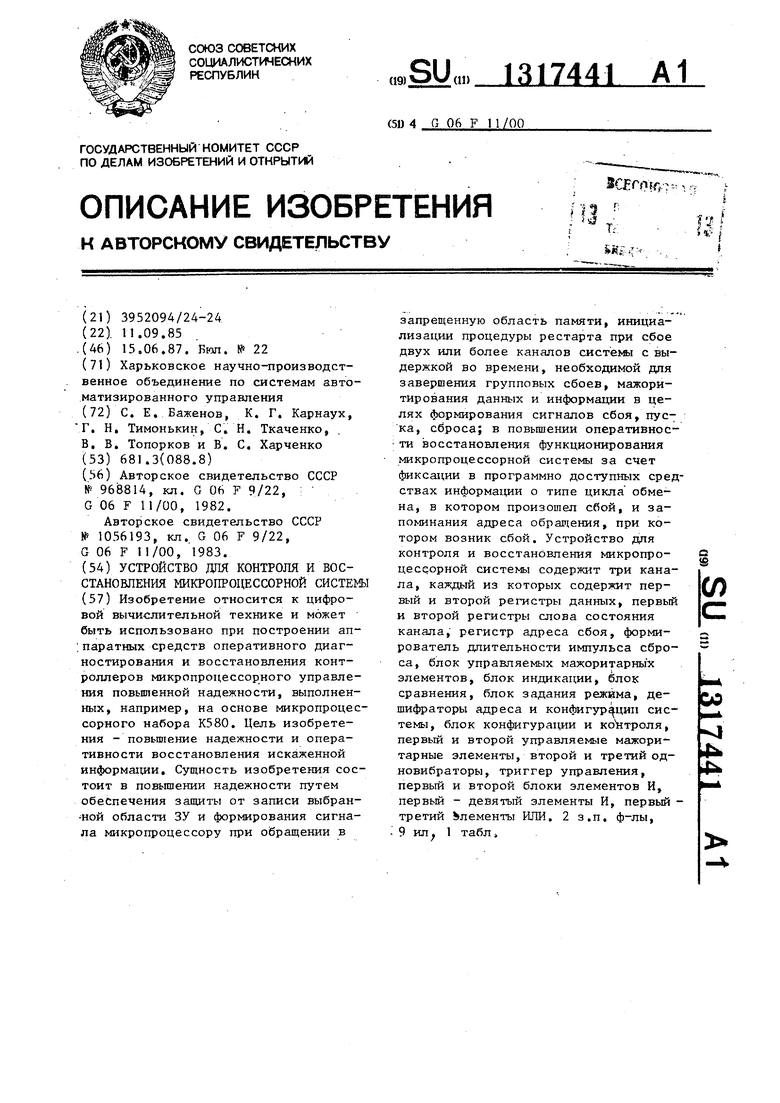

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении аппаратных средств оперативного диагностирования и восстановления контроллеров микропроцессорного управления повышенной надежности, выполненных, например, на основе микропроцессорного набора К580.

Целью изобретения является повышение надежности и оперативности восстановления искаженной информации,

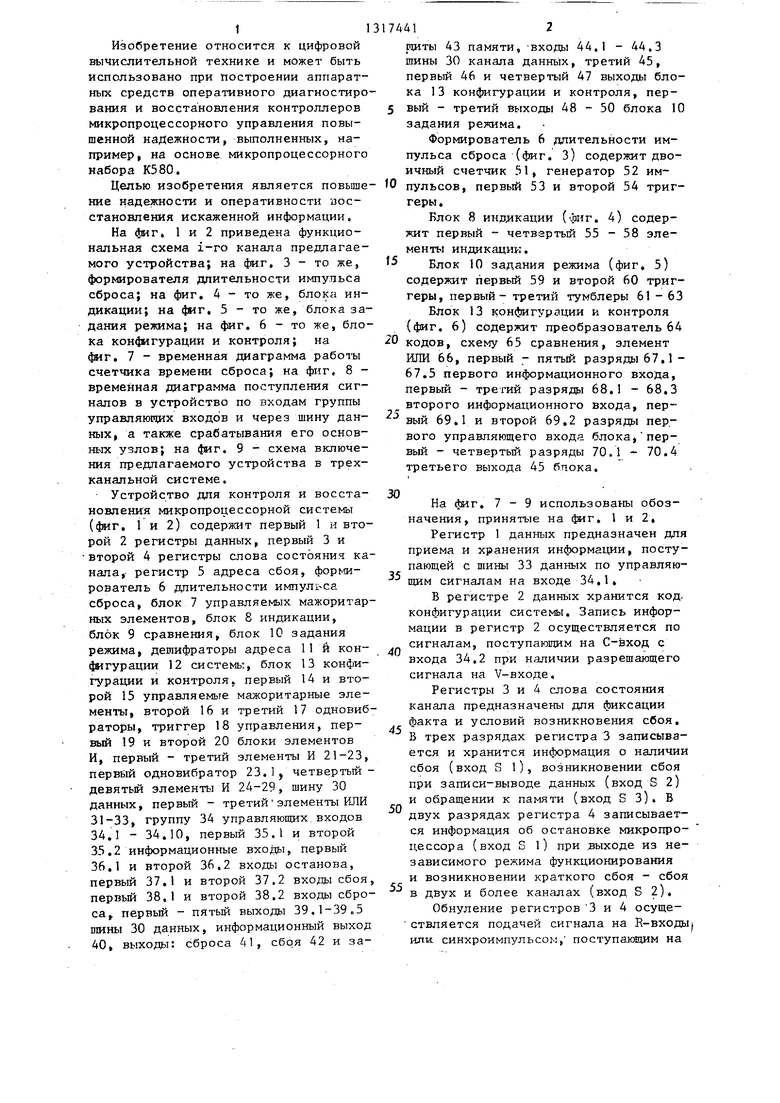

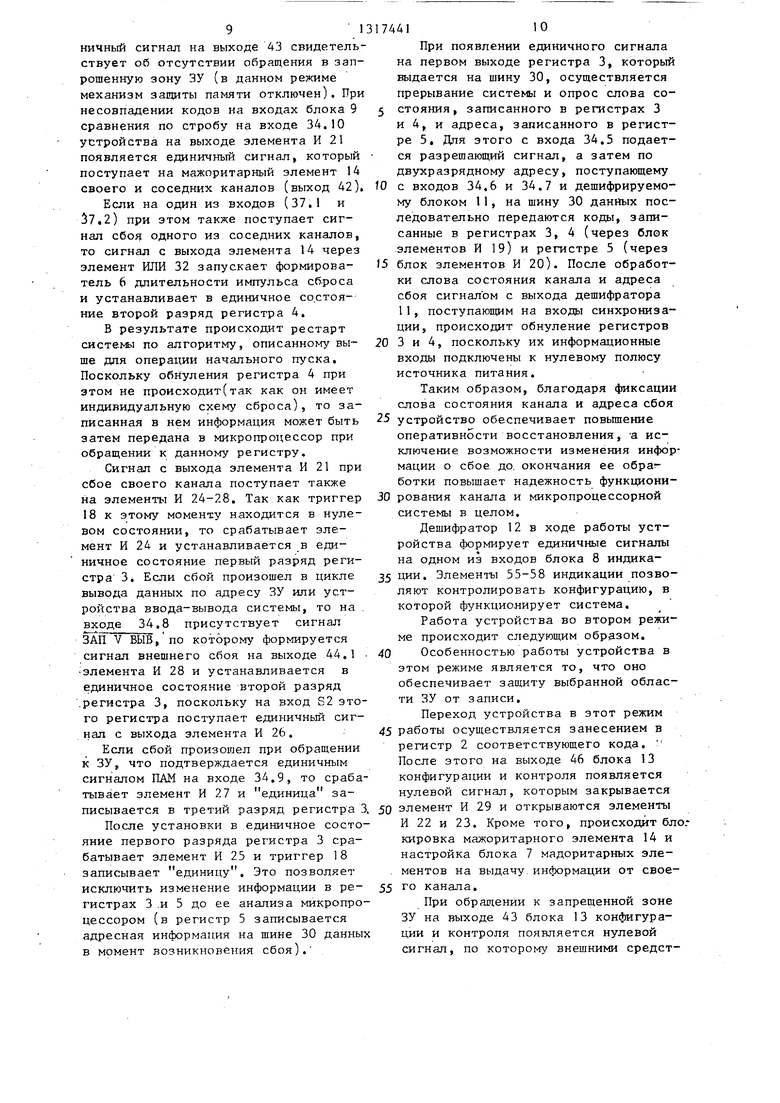

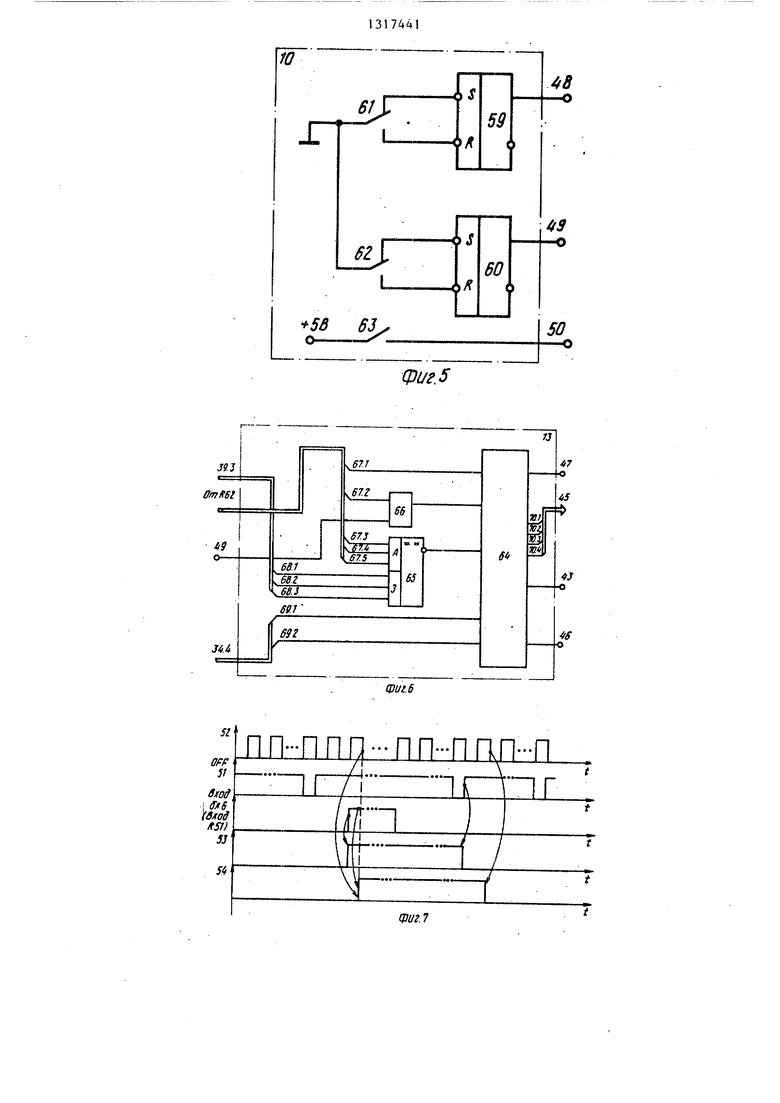

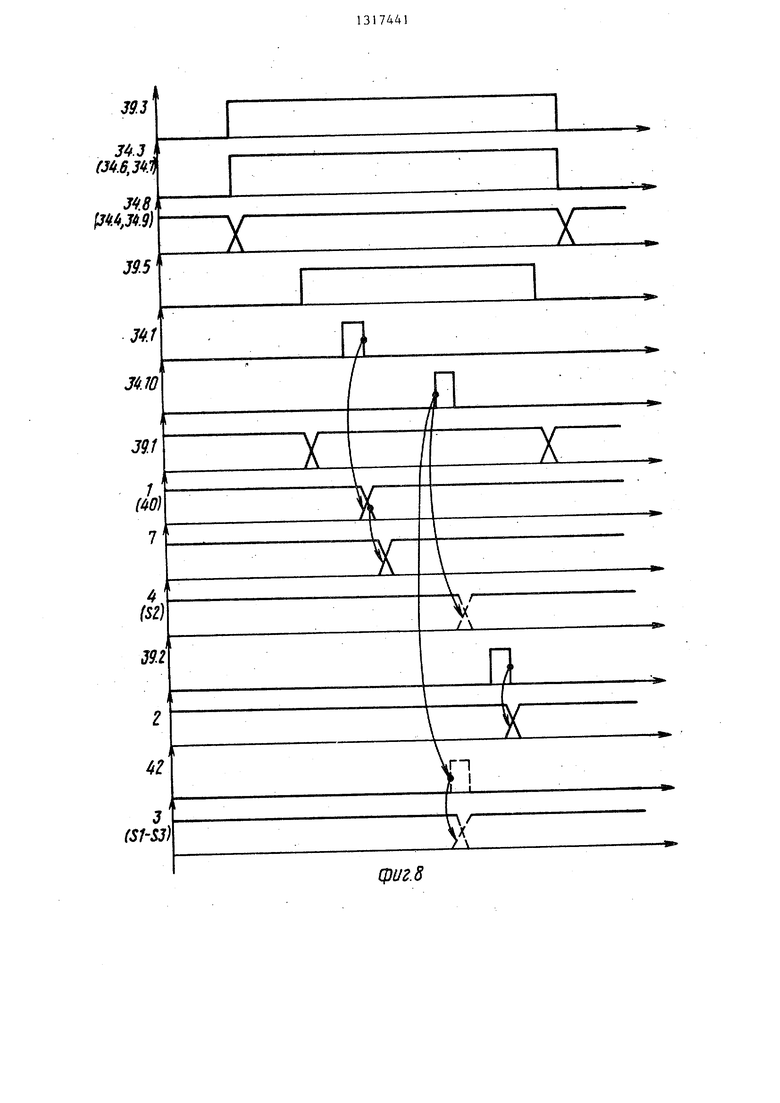

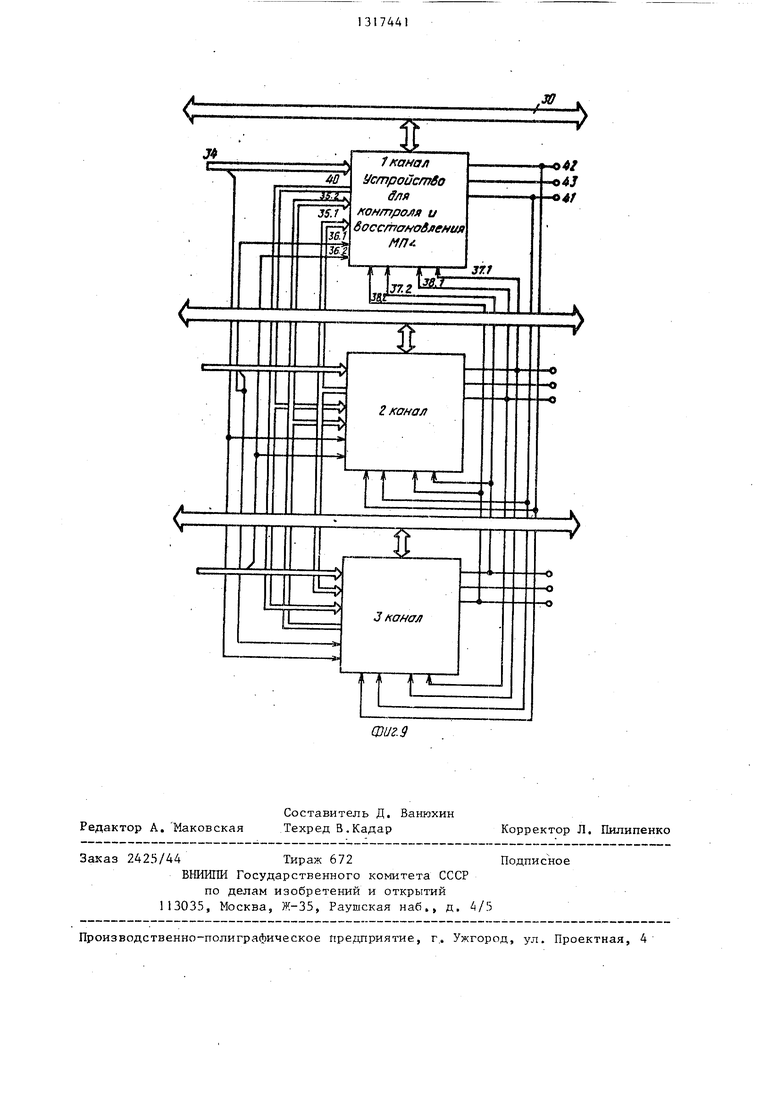

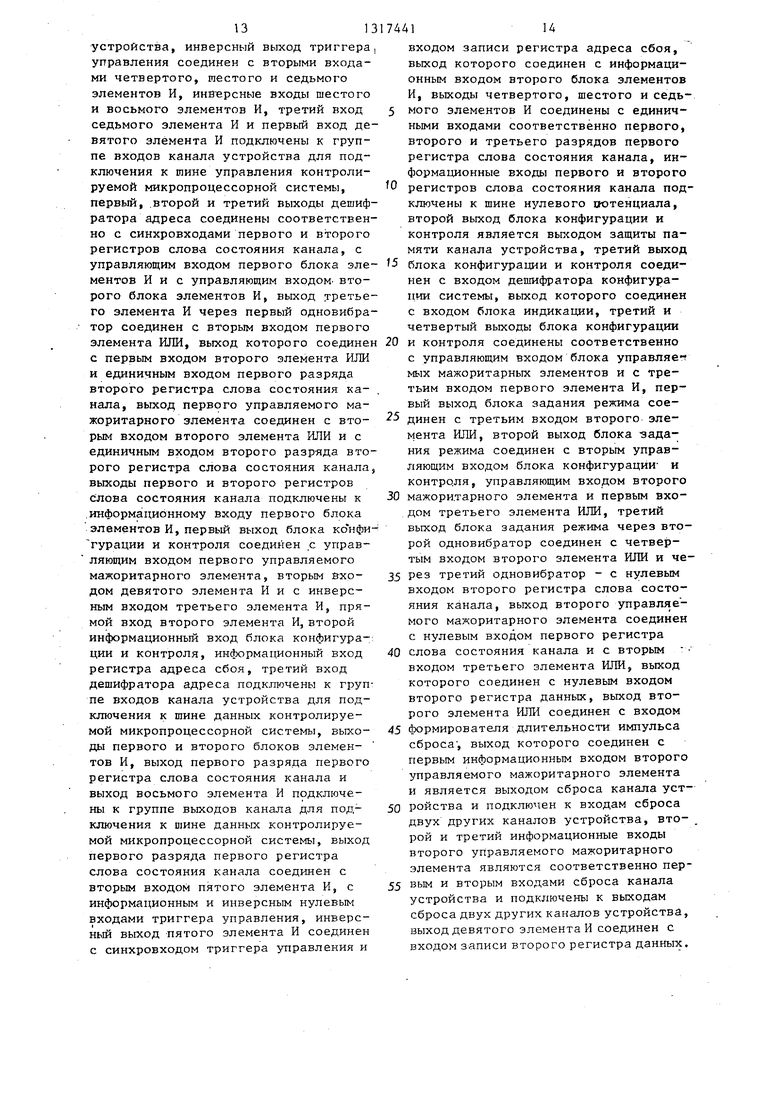

На (Jwr, 1 и 2 приведена функциональная схема i-ro канала предлагаемого устройства; на фи.г, 3 - то же, формирователя длительности импульса сброса; на фиг. 4 - то же, блока индикации; на фиг, 5 - то же, блока задания режима; на фиг. 6 - то же, блока конфигурации и контроля; на фиг. 7 - временная диаграмма работы счетчика времени сброса; на фиг, 8 - временная диаграмма поступления сигналов в устройство по входам группы управляющих входов и через шину данных, а также срабатывания его основных узлов; на фиг. 9 - схема включения предлагаемого устройства в трех- канапьной системе.

Устройство для контроля и восстановления микропроцессорной системы (4мг, 1 и 2) содержит первый 1 и второй 2 регистры данных, первый 3 и второй 4 регистры слова состояния канала, регистр 5 адреса сбоя, формирователь 6 длительности импульса сброса, блок 7 управляемых мажоритарных элементов, блок 8 индикации, блок 9 сравнения, блок 10 задания режима, дешифраторы адреса 11 и конфигурации 12 системы, блок 13 конфигурации и контроля, первый 14 и второй 15 управляемые мажоритарные элементы, второй 16 и третий 17 одновиб раторы, триггер 18 управления, первый 19 и второй 20 блоки элементов И, первый - третий элементы И 21-23, первый одновибратор 23. 1 j четвертый - девятый элементы И 24-29, шину 30 данных, первый - третий элементы ИЛИ 31-33, группу 34 управляюшлх входов

34.1- 34.10, первый 35.1 и второй

35.2информационные входа, первый 36.1 и второй 36.2 входы останова, первый 37,1 и второй 37.2 входы сбоя первьм 38.1 и второй 38,2 входы сброса,, первый - пятый выходы 39,1-39.5 тины 30 данных, информационный выход 40, выходы: сброса 41, сбоя 42 и за25

174412

щиты 43 памяти, -входы 44.1 - 44.3 шины 30 канала данных, третий 45, первый 46 и четвертый 47 выходы блока 13 конфигурации и контроля, пер- 5 вый - третий выходы 48-50 блока 10 задания режима.

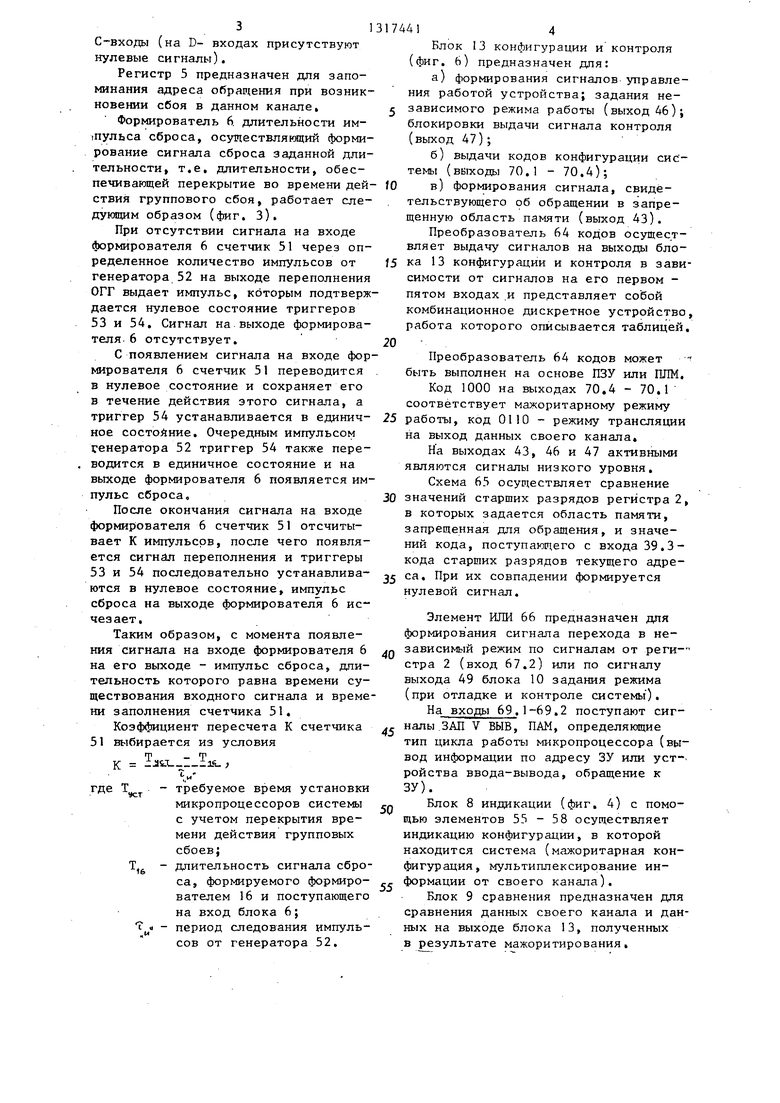

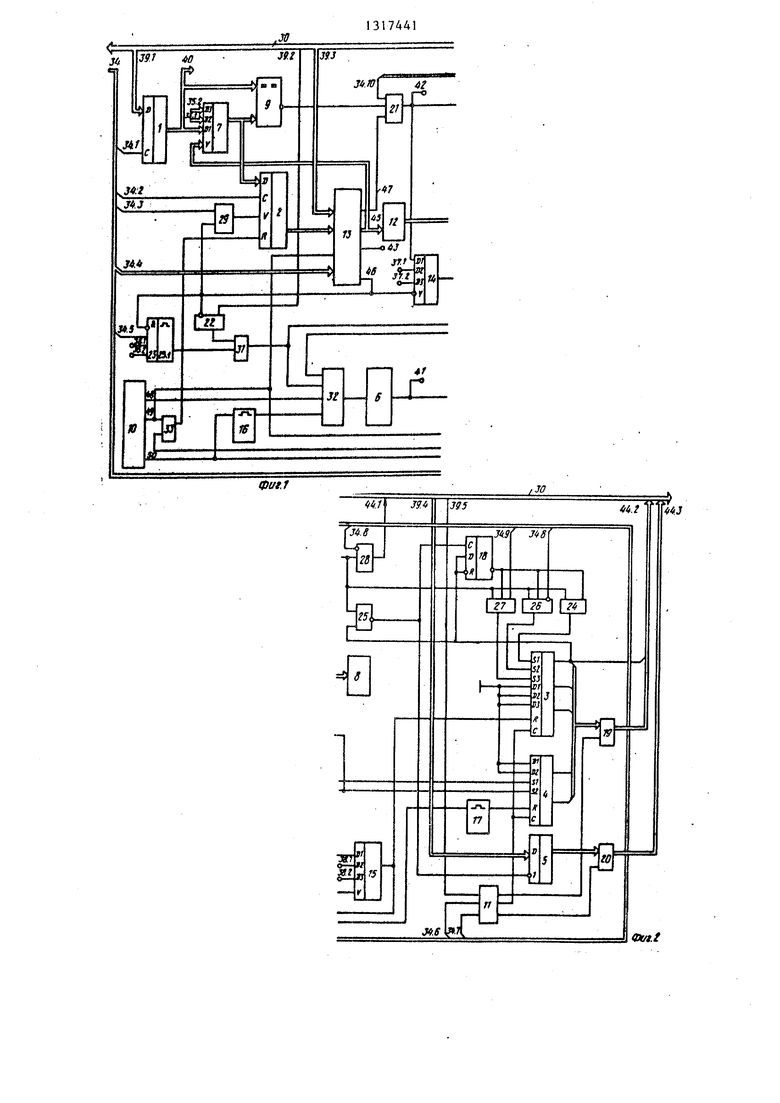

Формирователь 6 длительности импульса сброса (фиг. 3) содержит двоичный счетчик 51, генератор 52 им- 10 пульсов, первый 53 и второй 54 триггеры .

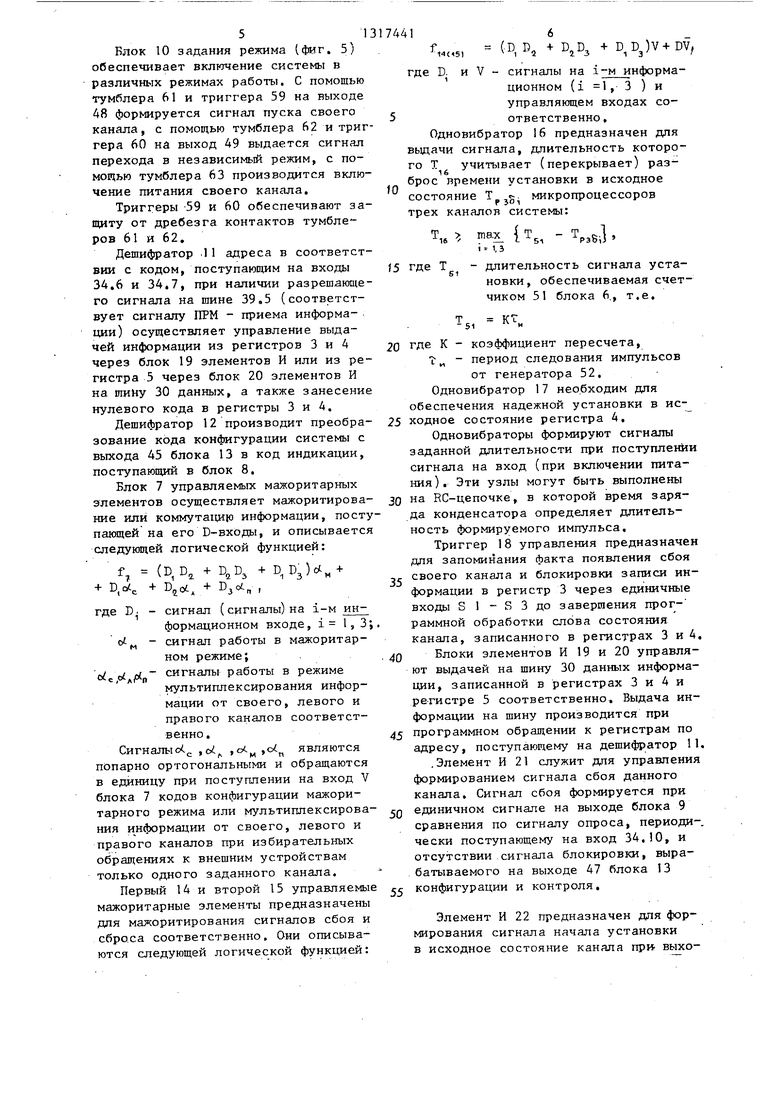

Блок 8 индакации (.риг. 4) содержит первый - четвзртый 55-58 элементы индикации,

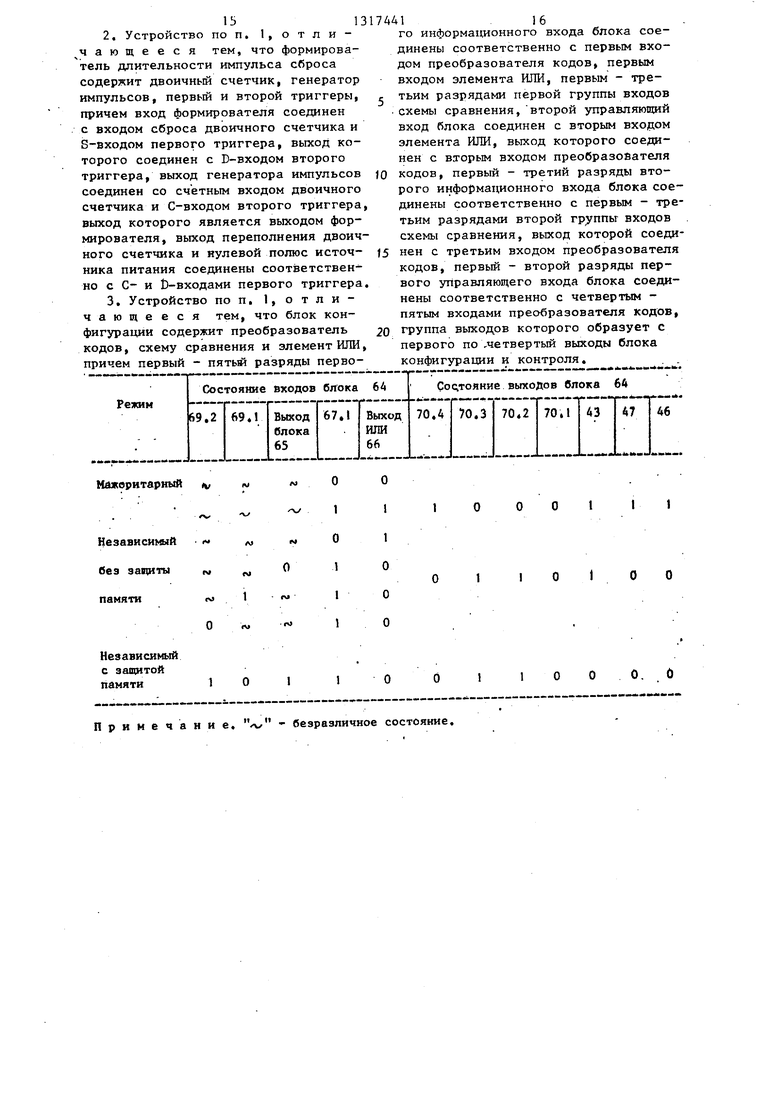

Блок 10 задания режима (фиг. 5) содержит первый 59 и второй 60 триггеры, первый- третий тумблеры 61-63

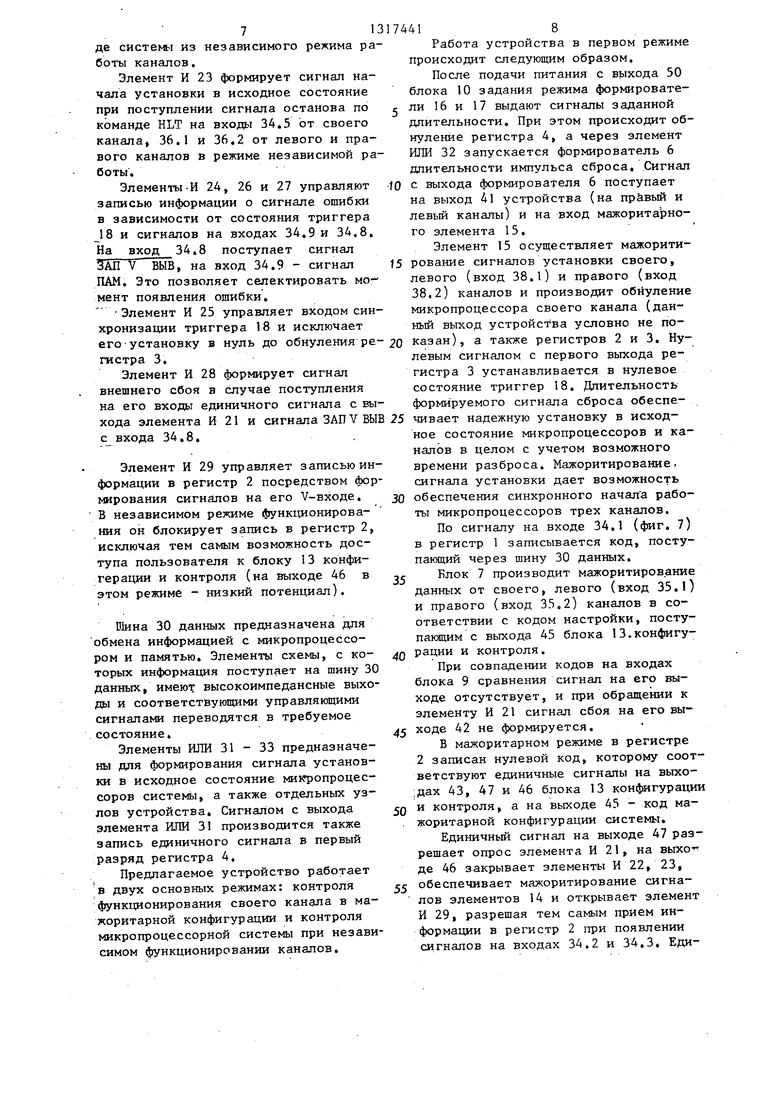

Блок 13 конфигурации и контроля (фиг. 6) содержит преобразователь 64 0 кодов, схему 65 сравнения, элемент ИЛИ 66, первый - пятый разряды 67,1 - 67.5 первого информационного входа, первый - третий разряд 1 68.1 - 68,3 второго информационного входа, первый 69.1 и второй 69.2 разряды первого управляющего входа блока, первый - четвертьш разряды 70.1 - 70,4 третьего выхода 45 блока,

30

На 5иг. 7-9 использованы обозначения, принятые на г, 1 и 2,

Регистр 1 данных предназначен для приема и хранения информации, поступающей с шины 33 данных по управляю- пщм сигналам на входе 34,1.

В регистре 2 данных хранится код. конфигурации системы. Запись информации в регистр 2 осуществляется по сигналам, поступающим на С-вход с входа 34.2 при наличии разрешающего сигнала на V-входе.

Регистры 3 и 4 слова состояния канала предназначены для фиксации факта и условий возникновения сбоя, В трех разрядах регистра 3 записывается и хранится информация о наличии сбоя (вход S 1), возникновении сбоя при записи-выводе данных (вход S 2) и обращении к памяти (вход S З). В двух разрядах регистра 4 записывается информация об остановке микропроцессора (вход S 1) при выходе из независимого режима функционирования и возникновении краткого сбоя - сбоя в двух и более каналах (вход S 2),

Обнуление регистров 3 и 4 осуще- ствляется подачей сигнала на R-входьь или синхроимпульсом, поступакацим на

40

45

50

3

С-входы (на D- входах присутствуют нулевые сигналы).

Регистр 5 предназначен для запоминания адреса обрап(ения при возникновении сбоя в данном канале,

Формирователь 6. длительности им- гпульса сброса, осушествлякяций формирование сигнала сброса заданной длительности, т.е. длительности, обеспечивающей перекрытие во времени действия группового сбоя, работает следующим образом (фиг. З).

При отсутствии сигнала на входе формирователя 6 счетчик 51 через определенное количество импульсов от генератора 52 на выходе переполнения ОГГ выдает импульс, которым подтверждается нулевое состояние триггеров 53 и 54. Сигнал на выходе формирователя- 6 отсутствует.

С появлением сигнала на входе формирователя 6 счетчик 31 переводится в нулевое состояние и сохраняет его в течение действия этого сигнала, а триггер 54 устанавливается в единичное состояние. Очередным импульсом генератора 52 триггер 54 также переводится в единичное состояние и на выходе формирователя 6 появляется импульс сброса.

После окончания сигнала на входе формирователя 6 счетчик 51 отсчитывает К импульсов, после чего появляется сигнал переполнения и триггеры 53 и 54 последовательно устанавливаются в нулевое состояние, импульс сброса на выходе фор мирователя 6 исчезает.

Таким образом, с момента появления сигнала на входе формирователя 6 на его выходе - импульс сброса, дпи- тельность которого равна времени существования входного сигнала и времени заполнения счетчика 51.

Коэффициент пересчета К счетчика 51 выбирается из условия

Т - Т К .,

ЕИ- где Т - требуемое время установки

микропроцессоров системы с учетом перекрытия времени действия групповых сбоев; Т., - длительность сигнала

са, формируемого формирователем 16 и поступающего на вход блока 6; - период следования импульсов от генератора 52.

174414

Блок 13 конфигурации и контроля (фиг. 6) предназначен для:

а)формирования сигналов управления работой устройства; задания не5 зависимого режима работы (выход 46); блокировки выдачи сигнала контроля (выход 47);

б)выдачи кодов конфигурации системы (выходы 70.1 - 70.4);

fO в) формирования сигнала, свидетельствующего об обращении в запрещенную область памяти (выход 43).

Преобразователь 64 кодов осуществляет выдачу сигналов на выходы бло}5 ка 13 конфигурации и контроля в зависимости от сигналов на его первом - пятом входах .и представляет собой комбинационное дискретное устройство, работа которого описывается таблицей.

20

Преобразователь 64 кодов может быть выполнен на основе ПЗУ или Ш1М.

Код 1000 на выходах 70,4 - 70.1 соответствует мажоритарному режиму 25 работы, код 0110 - режиму трансляции на выход данных своего канала.

На выходах 43, 46 и 47 активными являются сигналы низкого уровня.

Схема 63 осуществляет сравнение 30 значений старших разрядов регистра 2, в которых задается область памяти, запрещенная для обращения, и значений кода, поступающего с входа 39.3- кода старших разрядов текущего адре- 35 са. При их совпадении формируется нулевой сигнал.

Элемент ИЛИ 66 предназначен для формиров ания сигнала перехода в не

зависимый режим по сигналам от реги- стра 2 (вход 67.2) или по сигналу выхода 49 блока 10 задания режима (при отладке и контроле системы).

На входы 69.1-69.2 поступают сиг- налы ЗАП V ВЫВ, ПАМ, определяющие тип цикла работы микропроцессора (вывод информации по адресу ЗУ или уст-, ройства ввода-вывода, обращение к ЗУ).

Блок 8 индикации (фиг. 4) с помощью элементов 53 - 38 осуществляет индикацию конфигурации, в которой находится система (мажоритарная конфигурация, мультиплексирование информации от своего канала).

Блок 9 сравнения предназначен для сравнения данных своего канала и данных на выходе блока 13, полученных в результате мажоритирования.

Блок 10 задания режима (фиг, 5) обеспечивает включение системы в различных режимах работы. С помощью тумблера 61 и триггера 59 на выходе 48 формируется сигнал пуска своего канала, с помощью тумблера 62 и триггера 60 на выход 49 выдается сигнал перехода в независимый режим, с помощью тумблера 63 производится включение питания своего канала.

Триггеры -59 и 60 обеспечивают защиту от дребезга контактов тумбле ров 61 и 62,

Дешифратор .1 1 адреса в соответствии с кодом, поступающим на входы 34.6 и 34.7, при наличии разрешающего сигнала на шине 39,5 (соответствует сигналу ПРМ - приема информации) осуществляет управление выдачей информации из регистров 3 и 4 через блок 19 элементов И или из регистра 5 через блок 20 элементов И на шиНу 30 данных, а также занесение кулевого кода в регистры 3 и 4.

Дешифратор 12 производит преобразование кода конфигурации системы с выхода 45 блока 13 в код индикации, поступающий в блок 8.

Блок 7 управляемых мажоритарных

элементов осуществляет мажоритирова- JQ на RC-цепочке, в которой время заря- ние или коммутагццо информации, поступающей на его D-входы, и описывается следующей логической функцией:

да конденсатора определяет длительность формируемого импульса.

Триггер 18 управления предназначен дпя запоминания факта появления сбоя

f, - (D. D D.ot.

(

1 --i D,oi.

D,D, + )С, п

где D. Ы

- сигнал (сигналы) на 1-м информационном входе, i 1,3 сигнал работы в мажоритарном режиме; oi Д сигналы работы в режиме

мультиплексирования информации от своего, левого и правого каналов соответственно .

Сигналыс/. ,oi ° -м п являются попарно ортогональными и обращаются в единицу при поступлении на вход V блока 7 кодов конфигурации мажоритарного режима или мультиплексирования и нформации от своего, левого и правого каналов при избирательных обращениях к внешним устройствам только одного заданного канала.

Первый 14 и второй 15 управляемые мажоритарные элементы предназначены для мажоритирования сигналов сбоя и сбро.са соответственно. Они описываются следующей логической функцией:

- ( Д 15о

D,D,

10

14(,5, - , -2 -г-3 D C3)V-t-DV;

где D. и V - сигналы на i-м информа- ционном (i 1,3 ) и управляющем входах соответственно,

Одновибратор 16 предназначен для выдачи сигнала, длительность которого Т учитт 1вает (перекрывает) разброс времени установки в исходное состояние . микропроцессоров трех каналов системы:

Т 16

где Т

Е1

та,. { Т, - . ,

-1,3

- длительность сигнала установки, обеспечиваемая счетчиком 51 блока 6., т.е.

51

КТ

20 где К - коэффициент пересчета,

t - период следования импульсов

от генератора 52, Одновибратор 17 необходим для обеспечения надежной установки в ис- 25 ходное состояние регистра 4,

Одновибраторы формируют сигналы заданной длительности при поступлени сигнала на вход (при включении питания). Эти узлы могут быть выполнены

на RC-цепочке, в которой время заря-

да конденсатора определяет длительность формируемого импульса.

Триггер 18 управления предназначен дпя запоминания факта появления сбоя

своего канала и блокировки записи информации в регистр 3 через единичные входь: S 1 - S 3 до завершения прог- раммной обработки слова состояния канала, записанного в регистрах 3 и 4. Блоки элементов И 19 и 20 управляют выдачей на шину 30 данных информации, записанной в регистрах 3 и 4 и регистре 5 соответственно. Выдача информации на шину производится при

программном обращении к регистрам по адресу, поступающему на дешифратор 11. ,Элемент И 21 служит для управления формированием сигнала сбоя данного канала. Сигнал сбоя формируется при

единичном сигнале на выходе блока 9 сравнения по сигналу опроса, периоди-. чески поступающему на вход 34.10, и отсутствии сигнала блокировки, вырабатываемого на выходе 47 блока 13

конфигурации и контроля.

Элемент И 22 предназначен для формирования сигнала начала установки в исходное состояние канала пр выхоботы каналов,

Элемент И 23 формирует сигнал начала установки в исходное состояние при поступлении сигнала останова по команде HLT на входы 34.5 от своего канала, 36.1 и 36,2 от левого и правого каналов в режиме независимой работы.

Элементы-И 24, 26 и 27 управляют

записью информации о сигнале ошибки

в зависимости от состояния триггера

18 и сигналов на входах 34.9 и 34,8.

На вход 34.8 поступает сигнал

t5 рование сигналов установки своего, левого (вход 38.1) и правого (вход 38,2) каналов и производит обйуление микропроцессора своего канала (данный выход устройст ва условно не поЗАП V ВЫВ, на вход 34.9 - сигнал ПАМ. Это позволяет селектировать мо- мент появления ошибки,

Элемент И 25 управляет входом синхронизации триггера 18 и исключает его установку в нуль до обнуления ре-20 казан), а также регистров 2 и 3. Ну- гистра 3.левым сигналом с первого выхода реЭлемент И 28 формирует сигнал гистра 3 устанавливается в нулевое внешнего сбоя в случае поступления состояние триггер 18. Длительность на его входы единичного сигнала с вы- формируемого сигнала сброса обеспе- хода элемента И 21 и сигнала ЗАПУ ВЫВ 25 чивает надежную установку в исход- с входа 34,8,, ное состояние микропроцессоров и каЭлемент И 29 управляет записью информации в регистр 2 посредством формирования сигналов на его V-входе, В независимом режиме функционирова- ния он блокирует запись в регистр 2, исключая тем самым возможность доступа пользователя к блоку 13 конфи- герации и контроля (на выходе 46 в этом режиме - низкий потенциал).

П1ина 30 данных предназначена для обмена информацией с микропроцессором и памятью. Элементы схемы, с которых информация поступает на шину 30 данных, имеют высокоимпедансные выходы и соответствующими управляющими сигналами переводятся в требуемое состояние.

Элементы ИЛИ 31-33 предназначены для формирования сигнала установки в исходное состояние микропроцессоров системы, а также отдельных узлов устройства, Сигнашом с выхода элемента ИЛИ 31 производится также запись единичного сигнала в первый разряд регистра 4,

Предлагаемое устройство работает в двух основных режимах: контроля функционирования своего канала в мажоритарной конфигурации и контроля микропроцессорной системы при независимом функционировании каналов.

происходит следующим образом.

После подачи питания с выхода 50 блока 10 задания режима формирователи 16 и 17 выдают си гналы з аданной длительности. При этом происходит обнуление регистра 4, а через элемент ИЛИ 32 запускается формирователь 6 дпительности импульса сброса. Сигнал

с выхода формирователя 6 поступает на выход 41 устройства (на пр&вый и левый каналы) и на вход мажоритарного элемента 15.

Элемент 15 осуществляет мажоритирование сигналов установки своего, левого (вход 38.1) и правого (вход 38,2) каналов и производит обйуление микропроцессора своего канала (данный выход устройст ва условно не показан), а также регистров 2 и 3. Ну- левым сигналом с первого выхода реналов в целом с учетом возможного времени разброса. Мажоритирование. сигнала установки дает возможность обеспечения синхронного начал а работы микропроцессоров трех каналов.

По сигналу на входе 34.1 (фиг. 7) в регистр 1 записывается код, поступающий через шину 30 данных. Блок 7 производит Мажоритирование данных от своего, левого (вход 35,1) и правого (вход 35.2) каналов в соответствии с кодом настройки, поступающим с выхода 45 блока 13.конфигу- рации и контроля,

При совпадении кодов на входах блока 9 сравнения сигнал на его выходе отсутствует, и при обращении к элементу И 21 сигнал сбоя на его вы- ходе 42 не формируется,

В мажоритарном режиме в регистре 2 записан нулевой код, которому соответствуют единичные сигналы на выхо- дах 43, 47 и 46 блока 13 конфигурации и контроля, а на выходе 45 - код мажоритарной конфигурации системы.

Единичный сигнал на выходе 47 разрешает опрос элемента И 21, на выхо- де 46 закрывает элементы И 22, 23, обеспечивает Мажоритирование сигна- лов элементов 14 и открывает элемент И 29, разрешая тем самым прием информации в регистр 2 при появлении сигналов на входах 34.2 и 34,3, Еди

91

ничный сигнал на выходе 43 свидетельствует об отсутствии обращения в запрошенную зону ЗУ (в данном режиме механизм защиты памяти отключен). При несовпадении кодов на входах блока 9 сравнения по стробу на входе 34.10 устройства на выходе элемента И 21 появляется единичньй сигнал, который поступает на мажоритарный элемент 14 своего и соседних каналов (выход 42),

Если на один из входов (37.1 и 37,2) при этом также поступает сигнал сбоя одного из соседних каналов, то сигнал с выхода элемента 14 через элемент ИЛИ 32 запускает формирователь 6 длительности импульса сброса и устанавливает в единичное состояние второй разряд регистра 4.

В результате происходит рестарт системы по алгоритму, описанному выше для операции начального пуска, Поскольку обнуления регистра 4 при этом не происходит(так как он имеет индивидуальную схему сброса), то записанная в нем информация может быть затем передана в микропроцессор при обращении к данному регистру.

Сигнал с выхода элемента И 21 при сбое своего канала поступает также на элементы И 24-28, Так как триггер 18 к этому моменту находится в нулевом состоянии, то срабатывает элемент И 24 и устанавливается в единичное состояние первый разряд регистра 3, Если сбой произошел в цикле вывода данных по адресу ЗУ или устройства ввода-вывода системы, то на . входе 34.8 присутствует сигнал ЗАП V БЫВ, по которому формируется сигнал внешнего сбоя на выходе 44,1 элемента И 28 и устанавливается в единичное состояние второй разряд .регистра 3, поскольку на вход Б2 этого регистра поступает единичный сигнал с выхода элемента И 26.

Если сбой произошел при обращении к ЗУ, что подтверждается единичным сигналом ПАМ на входе 34.9, то срабатывает элемент И 27 и единица записывается в третий разряд регистра 3

После установки в единичное состояние первого разряда регистра 3 срабатывает элемент И 25 и триггер 18 записывает единицу. Это позволяет исключить изменение информации в регистрах 3 .и 5 до ее анализа микропроцессором (в регистр 5 записывается адресная информация на шине 30 данных в момент возникновения сбоя).

4110

При появлении единичного сигнала на первом выходе регистра 3, который выдается на шину 30, осуществляется прерывание системы и опрос слова состояния, записанного в регистрах 3 и 4, и адреса, записанного в регистре 5, Для этого с входа 34,5 подается разрешающий сигнал, а затем по двухразрядному адресу, поступающему

с входов 34.6 и 34.7 и дешифрируемому блоком 11, на шину 30 данйых последовательно передаются коды, записанные в регистрах 3, 4 (через блек элементов И 19) и регистре 5 (через

блок элементов И 20). После обработки слова состояния канала и адреса сбоя сигналом с выхода дешифратора 11, поступаюп им на входы синхронизации, происходит обнуление регистров

3 и 4, поскольку их информационные входы подключены к нулевому полюсу источника питания.

Таким образом, благодаря фиксации слова состояния канала и адреса сбоя

устройство обеспечивает повьппение оперативности восстановления, -а исключение возможности изменения информации о сбое до, окончания ее обра ботки повышает надежность функционирования канала и микропроцессорной системы в целом.

Дешифратор 12 в ходе работы устройства формирует единичные сигналы на одном из входов блока 8 индикации. Элементе 55-58 индикации позволяют контролировать конфигурацию, в которой функционирует система.

Работа устройства во втором режиме происходит следующим образом,

Особенностью работы устройства в этом режиме является то, что оно обеспечивает защиту выбранной области ЗУ от записи.

Переход устройства в этот режим

работы осуществляется занесением в регистр 2 соответствующего кода, После этого на выходе 46 блока 13 конфигурации и контроля появляется нулевой сигн;1л, которым закрывается

элемент И 29 и открываются элементы И 22 и 23. Кроме того, происходит блог кировка мажоритарного элемента 14 и настройка блока 7 мадоритарных эле- ментов на выдачу информации от своего канала.

При обрагцении к запрещенной зоне ЗУ на выходе 43 блока 13 конфигурации и контроля появляется нулевой сигнал, по которому внешними средст111

вами осуществляется блокировка исполнительных интерфейсных сигналов.

Выход из независимого режима работы осуществляется при поступлении сигнала с входа 39,2, В результате формируется единичный сигнал элемен- ,том И 22, который проходит черех элемент ИЛИ 31, записывается в первом разряде регистра 4 и, кроме того поступает через элемент ИЛИ 32 в счетчик 6, вызывая рестарт канала (системы).

Рестарт в этом режиме может быть вызван также при одновременном поступлении сигналов останова от своего (вход 34.5.) и соседних (входы 36.1 и 36.2) каналов, что приводит к срабатыванию элемента И 23.

Предлагаемое устройство позволяет проводить выборочный пуск каналов путем подачи сигнала на выход 48 блока 10 задания режимов. При контроле и отладке систеьы с помощью тумблера 62, формирующего сигнал на выходе 49 блока 10, обеспечивается необходимый режим работы блока 13 конфигурации и 1сонтроля и управляемого мажоритарного элемента 15.

Формула изобретения

1. Устройство для контроля и восстановления микропроцессорной системы, содержащее три канала, причем каждый канал содержит первый и второ регистры данных, первый и второй регистры слова состояния канала, формирователь длительности импульса сброса, блок конфигурации и контроля блок сравнения, дешифратор адреса, триггер управления, первый блок элементов И, с первого по седьмой элементы И, с первого по третий элементы ИЛИ, причем информационньш вход первого регистра данных подключен к входу канала устройства для подключения к шине данных контролируемой микропроцессорной системы, выход первого регистра данных соединен с первым входом блока сравнения и является информационным выходом канала устройства и подключен к информахщонным входам двух других каналов устройства, выход блока сравнения соединен с первым входом первого элемента И, выход второго регистра данных соеди- нен с первым информационным входом блока конфигурации и контроля, первы выход которого соединен с инверсным

11.

входом второго элемента И, отличающееся тем, что, с целью повьппения надежности и оперативности восстановления искаженной информации,

каждый канал устройства содержит регистр адреса сбоя, блок индикации, блок задания режима, дешифратор конфигурации системы, блок управляемых, мажоритарных элементов, второй блок

элементов И, первый и второй управляемые мажоритарные элементы, первый, второй и третий одновибраторы, восьмой и девятый элементы И, причем выход второго элемента И соединен с

первым входом первого элемента ИЛИ, первый и второй входы третьего элемента И подключены к первому и второму входам останова канала устройства и подключены к входным шинам управления двух других каналов устройства, вход синхронизации первого регистра данных, вход синхронизации второго регистра данных, первый управляющий вход блока конфигурации и контроля, третий вход третьего элемента И, первый и второй входы дешифратора адреса, второй вход первого элемента И подключены к группе входов канала устройства для подключеНИН к шине управления контролируемой микропроцессорной системы, выход первого регистра данных соединен с первым информационным входом блока управляемых мажоритарНЕ 1х элементов,

второй и третий информационные входы блока управляемых мажоритарных элементов подключены соответственно к первому и второму информационным входам канала устройства и подключены

к информационным выходам двух других каналов устройства, выход блока уп- равляемых мажоритарных элементов соединен с вторым входом блока сравнения и информационным входом второго

регистра данных, выход первого элемента И соединен с первым информаци- онньм входом первого управляемого мажоритарного элемента, с первыми входами четвертого, пятого, шестого

и седьмого элементов И, с прямым входом восьмого элемента И и является выходом сбоя канала устройства и подключен к входам сбоя двух других каналов, второй и третий информационные входы первого управляемого ма- жоритарного элемента являются соответственно первым и вторым входами сбоя канала устройства и подключены к выходам сбоя двух других каналов

1313

устройства, инверсный выход триггера управления соединен с вторыми входами четвертого, шестого и седьмого элементов И, инверсные входы шестого и восьмого элементов И, третий вход седьмого элемента И и первый вход девятого элемента И подключены к группе входов канала устройства для подключения к тине управления контролируемой микропроцессорной системы, первый, .второй и третий выходы дешифратора адреса соединены соответственно с синхровходами первого и второго регистров слова состояния канала, с управляющим входом первого блока элементов И и с управляющим входоМ второго блока элементов И, выход третьего элемента И через первый одновибра- тор соединен с вторым входом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ и единичным входом первого разряда второго регистра слова состояния канала, выход первого управляемого мажоритарного элемента соединен с вторым входом второго элемента ИЛИ и с единичным входом второго разряда второго регистра слова состояния каналаj выходы первого и второго регистров слова состояния канала подключены к .информационному входу первого блока элементов И, первый выход блока ко нфи урации и контроля соединен с управляющим входом первого управляемого мажоритарного элемента, вторым входом девятого элемента И и с инверсным входом третьего элемента И, прямой вход второго элемента И, второй информационный вход блока конфигура-: ции и контроля, информационный вход регистра адреса сбоя, третий вход дешифратора адреса подключены к группе входов канала устройства для подключения к шине данных контролируемой микропроцессорной системы, выходы первого и второго блоков элементов И, выход первого разря.да первого регистра слова состояния канала и выход восьмого элемента И подключены к группе выходов канала для подключения к тине данных контролируемой микропроцессорной системы, выход первого разряда первого регистра слова состояния канала соединен с вторым входом пятого элемента И, с информационным и инверсным нулевым входами триггера управления, инверсный выход пятого элемента И соединен с синхровходом триггера управления и

U

входом записи регистра адреса сбоя, выход которого соединен с информационным входом второго блока элементов И, выходы четвертого, шестого и седьмого элементов И соединены с единичными входами соответственно первого, второго и третьего разрядов первого регистра слова состояния канала, информационные входы первого и второго

регистров слова состояния канала подключены к шине нулевого потенциала, второй выход блока конфигурации и контроля является выходом защиты памяти канала устройства, третий выход

блока конфигурации и контроля соединен с входом дешифратора конфигурации системы, выход которого соединен с входом блока индикации, третий и четвертый выходы блока конфигурации

и контроля соединены соответственно с управляющим входом блока управляв мых мажоритарных элементов и с третьим входом первого элемента И, первый выход блока задания режима соединен с третьим входом второго элемента ИЛИ, второй выход блока задания режима соединен с вторым управ- ляюш.им входом блока конфигурации и контроля, управляющим входом второго

мажоритарного элемента и первым входом третьего элемента ИЛИ, третий выход блока задания режима через второй одновибратор соединен с четвертым входом второго элемента ШШ и через третий одновибратор - с нулевым входом второго регистра слова состояния канала, выход второго управляемого мажоритарного элемента соединен с нулевым входом первого регистра

слова состояния канала и с вторым входом третьего элемента ИЛИ, выход которого соединен с нулевым входом второго регистра данных, выход второго элемента ИЛИ соединен с входом

формироватепя длительности импульса сброса , выход которого соединен с первым информационным входом второго управляемого мажоритарного элемента и является выходом сброса канала устройства и подключен к входам сброса двух других каналов устройства, вто- рой и третий информационные входы второго управляемого мажоритарного элемента являются соответственно первым и вторым входами сброса канала устройства и подключены к выходам сброса двух других каналов устройства, выход девятого элемента И соединен с входом записи второго регистра данных.

15

2,Устройство по п. 1,отли- чающееся тем, что формирователь длительности импульса сброса содержит двоичный счетчик, генератор импульсов, первый и второй триггеры, причем вход формирователя соединен

с входом сброса двоичного счетчика и S-входом первого триггера, выход которого соединен с Б-входом второго триггера, выход генератора импульсов соединен со счетным входом двоичного счетчика и С-входом второго триггера, выход которого является выходом формирователя, выход переполнения двоичного счетчика и нулевой полюс источника питания соединены соответственно с С- и Ь-входами первого триггера.

3.Устройство поп, 1, отличающееся тем, что блок конфигурации содержит преобразователь кодов, схему сравнения и элемент ИЛИ, причем первый - пятый разряды перво13

«

V

« го

О 1 О 1 I 1

Независимый с защитой памяти

Примечание. /ЧУ

II

безразличное состояние.

, .

3174Д116

го информационного входа блока соединены соответственно с первым входом преобразователя кодов, первым входом элемента ИЛИ, первым - тре- г тьим разрядами первой группы входов .схемы сравнения, второй управляющий вход блока соединен с вторым входом элемента ИЛИ, выход которого соединен с вторым входом преобразователя

10 кодов, первый - третий разряды второго инфо4)мационного входа блока соединены соответственно с первым - третьим разрядами второй группы входов схемы сравнения, выход которой соеди15 нен с третьим входом преобразователя кодов, первый - второй разряды первого управляющего входа блока соединены соответственно с четвертым - пятым входами преобразователя кодов,

20 группа выходов которого образует с первого по ,четвертый выходы блока конфигурации и контроля,

1 О 001 It

0110

о о

о о 1 1 о о 0. U

фиг. Т

JO

Omff/toM J/ О

OPP

s с s

«/ -О

сриг.З

фиг A

фиг.5

фиг. 8

Редактор А. Маковская

Составитель Д. Ванюхин .Техред В.Кадар

Заказ 2425/44Тираж 672Подписное

ВНИШТИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/3

.,..«-... - -..- -. - - --.

Производственно-полиграфическое предприятие, г.. Ужгород, ул. Проектная, 4

Корректор Л. Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для резервирования и восстановления микропроцессорной системы | 1986 |

|

SU1374235A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| Многоканальное устройство для обмена данными микропроцессорной системы | 1985 |

|

SU1264193A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Многоканальное устройство для тестового контроля группы цифровых блоков | 1984 |

|

SU1238084A1 |

| Устройство для прерывания резервированной вычислительной системы | 1984 |

|

SU1218385A1 |

| Устройство контроля и управления реконфигурацией | 1984 |

|

SU1213554A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1989 |

|

SU1709569A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении ап:паратных средств оперативного диагностирования и восстановления контроллеров микропроцессорного управления повышенной надежности, выполненных, например, на основе микропроцессорного набора К580. Цель изобретения - повьш1ение надежности и оперативности восстановления искаженной информшщи. Сущность изобретения состоит в повышении надежности путем обеспечения защиты от записи выбран- ной области ЗУ и формирования сигнала микропроцессору при обращении в запрещенную область памяти, инициализации процедуры рестарта при сбое двух или более каналов системы с выдержкой во времени, необходимой для завершения групповых сбоев, мажори- тирования данных и информации в целях формирования сигналов сбоя, пуска, сброса; в повышении оперативнос- ; ти восстановления функционирования микропроцессорной системы за счет фиксации в программно доступных средствах информации о типе цикла обмена, в котором произошел сбой, и запоминания адреса обра1 (ения, при котором возник сбой. Устройство для контроля и восстановления микропроцессорной системы содержит три канала, каткдый из которых содержит первый и второй регистры данных, первый и второй регистры слова состояния канала, регистр адреса сбоя, формирователь длительности импульса сброса, блок управляемых мажоритарных элементов, блок индикации, ёлок сравнения, блок задания режима, дешифраторы адреса и конфигурации системы, блок конфигурации и контроля, первый и второй управляемые мажоритарные элементы, второй и третий од- новибраторы, триггер управления, первый и второй блоки элементов И, первьм - девятый элементы И, первый - третий Элементы ШШ. 2 з.п. ф-лы, 9 ил 1 табл Q S (Л CZ DO

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-15—Публикация

1985-09-11—Подача