1

Изобретение относится, к области вычислительной техники, и в частности, к устройствам, обеспечивающим переменную приоритетность сигналов прерываиия в электронных вычислительных машинах.

Из:вестпо устройство переменного приоритета, содержащее регистр приоритета, один выход которого соединен с дешифратором, а вход - с лер.вым выходом блока управления, второй выход которого соединен с нервЫ|М входом счетчика.

С целью сокращения оборудования устройства оно содержит блок выявления приоритетного разряда прерывания и циклический регистр сдвига, причем другой 1выход регистра приоритета соединен со вторым входом счетчика, третий вход которого соединен с одним выходом блока выявления приоритетного разряда прерывания, входы которого соединены с выхода,М1и дешифратора, счетчика и циклического регистра сдвига, вход которого соединен с третьим выходом блока управления, а вход блока управления соединен с другим выходо м блока выявления приоритетног разряда прерывания.

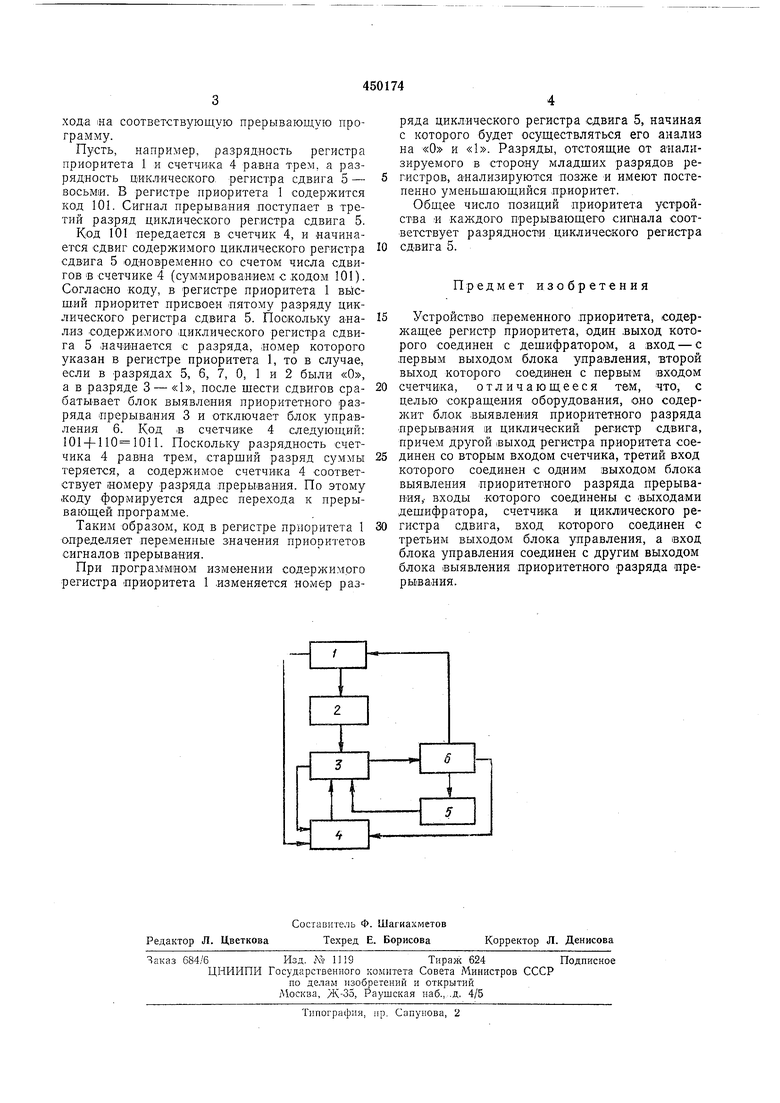

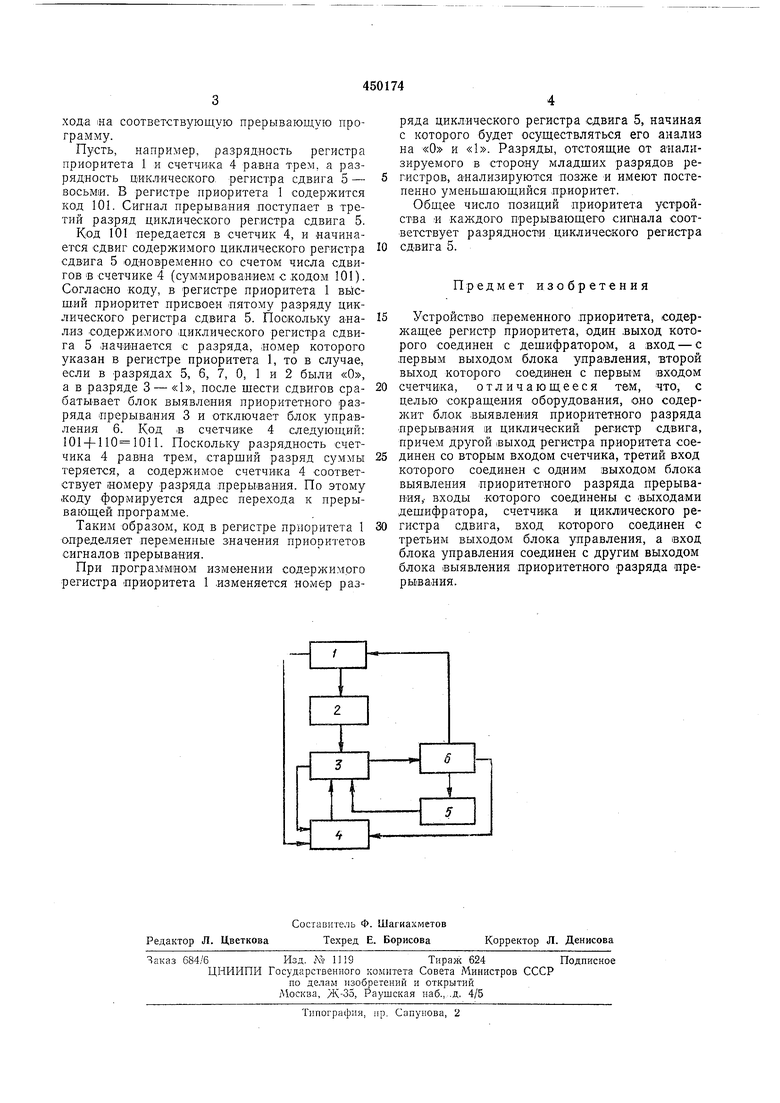

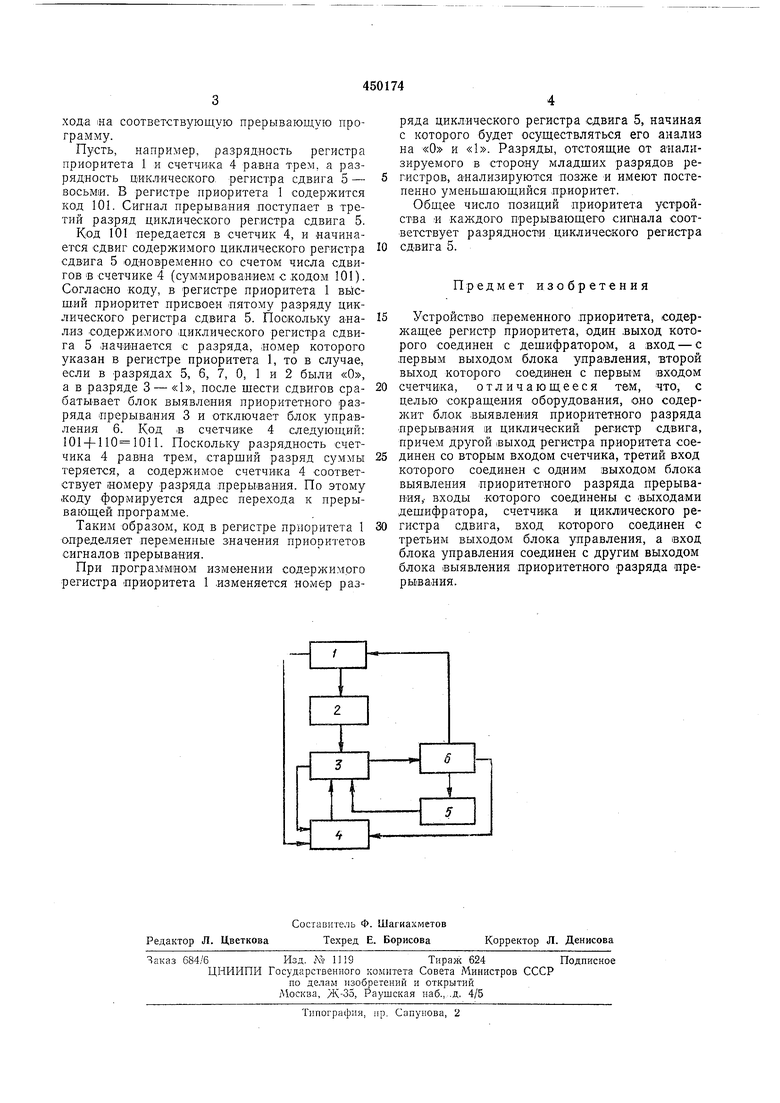

Блок-схема устройства приведена на чертеже.

Устройство переменного приоритета содержит: регистр приоритета 1, дешифратор 2, блок 3 выявления приоритетного разряда прерывания, счетчик 4, циклический регистр сдвига 5, блок управления 6.

Устройство работает следующим образом. В регистр приоритета 1 программно занооится код, соответствующий номеру разряда циклического регистра сдвига 5, связанный с которым сигнал прерывания должен иметь в данный момеит высший приоритет. Циклический регистр сдвига 5 и счетчик 4 устапавлнваются в «О.

При поступлении одного пли нескольких сигналов прерывания соответствующие разряды циклического регистра сдвига 5 устанавливаются в «1, выполнение текущей программы прерывается и начинает работать блок управления 6, в результате чего содержимое регистра приоритета 1 заносится в счетчик 4, а содержимое циклического регистра сдвига 5 начинает сдвигаться в сторону старшего разряда.

Одновременно после каждого такта сдвига блоком 3 выявления приоритетного разряда прерывания анализируется текущее состояппе определенного разряда циклического регистра

сдвига 5, выбранного кодом в регистре приоритета 1. При нулевом состоянии разряда в счетчик 4 добавляется «I, прп единичном состоянии разряда блок управления 6 отключается, а содержимое счетчика 4 используется

в качестве модулируемой части адреса перехода 1на соответствующую прерывающую программу.

Пусть, например, разрядность регистра приоритета 1 и счетчика 4 равна трем, а разрядность циклического, регистра сдвига 5 - восьми. В регистре приоритета 1 содержится код 101. Сигнал прерывания поступает в третий разряд циклического регистра сдвига 5.

Код 101 передается в счетчик 4, и начинается сдвиг содержимого циклического регистра сдвига 5 одновременно со счетом числа сдвигов в счетчике 4 (суммирован ием с .кодом 101). Согласно коду, в регистре приоритета 1 вЫсщ.ий приоритет присвоен пятому разряду циклического регистра сдвига 5. Поскольку анаЛИЗ .содержимого циклического регистра сдвига 5 -начинается с разряда, яомер которого указан в регистре приоритета 1, то в случае, если в разрядах 5, 6, 7, О, 1 и 2 были «О, а в разряде 3 - «1, после шести сдвигов ерабатывает блок выявления приоритетного разряда прерывания 3 и отключает блок управления 6. Код в счетчике 4 следующий: 101 + . Поскольку разрядность счетчика 4 равна трем, старший разряд суммы теряется, а содержимое счетчика 4 соответствует номеру разряда прерывания. По этому коду формируется адрес перехода к прерывающей .программе.

Таким образом, код в регистре приоритета 1 определяет переменные значения приоритетов сигналов прерывания.

При программном изменении содержимого регистра приоритета 1 изменяется номер разряда циклического регистра сдвига 5, начиная с которого будет осуществляться его анализ на «О и «1. Разряды, отстоящие от анализируемого в сторону младших разрядов регистров, анализируются позже и имеют постепенно уменьшающийся .пр.иоритет.

Общее число позиций приоритета устройства я каждого прерывающего сигнала соответствует разрядности циклического регистра сдвига 5.

Предмет изобретения

Устройство переменного .приоритета, содержа.щее регистр приоритета, один выход которого соединен с дешифратором, а вход - с первым выходом блока управления, второй выход которого соединен с первым входом счетчика, отличающееся тем, что, с целью сокращения оборудования, оно содержит блок выявления приоритетного разряда прерывания и циклический регистр сдвига, причем другой выход регистра приоритета соединен со вторым входом счетчика, третий вход которого соединен с одним выходом блока выявления приоритетного разряда прерывания,, входы .которого соединены с выходами дешифратора, счетчика и ци.клического регистра сдвига, вход которого соединен с третьим выходом блока управления, а вход блока управления соединен с другим выходом блока выявления приоритетного разряда прерывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переменного приоритета | 1975 |

|

SU547767A2 |

| Устройство переменного приоритета | 1981 |

|

SU962948A1 |

| Устройство переменного приоритета | 1978 |

|

SU746520A1 |

| Устройство переменного приоритета | 1974 |

|

SU506854A1 |

| Устройство переменного приоритета | 1988 |

|

SU1585797A1 |

| Устройство переменного приоритета | 1984 |

|

SU1270759A2 |

| Устройство переменного приоритета | 1987 |

|

SU1462308A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| Селектор импульсов по длительности | 1981 |

|

SU945973A2 |

| Устройство для приоритетного обслуживания запросов | 1981 |

|

SU955069A1 |

Авторы

Даты

1974-11-15—Публикация

1972-12-25—Подача