(54) УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переменного приоритета | 1988 |

|

SU1585797A1 |

| Устройство переменного приоритета | 1987 |

|

SU1418715A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| Устройство для обработки прерываний | 1985 |

|

SU1282124A1 |

| Устройство смешанного приоритета | 1989 |

|

SU1619272A1 |

| Устройство для обмена информацией | 1984 |

|

SU1180905A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1224805A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

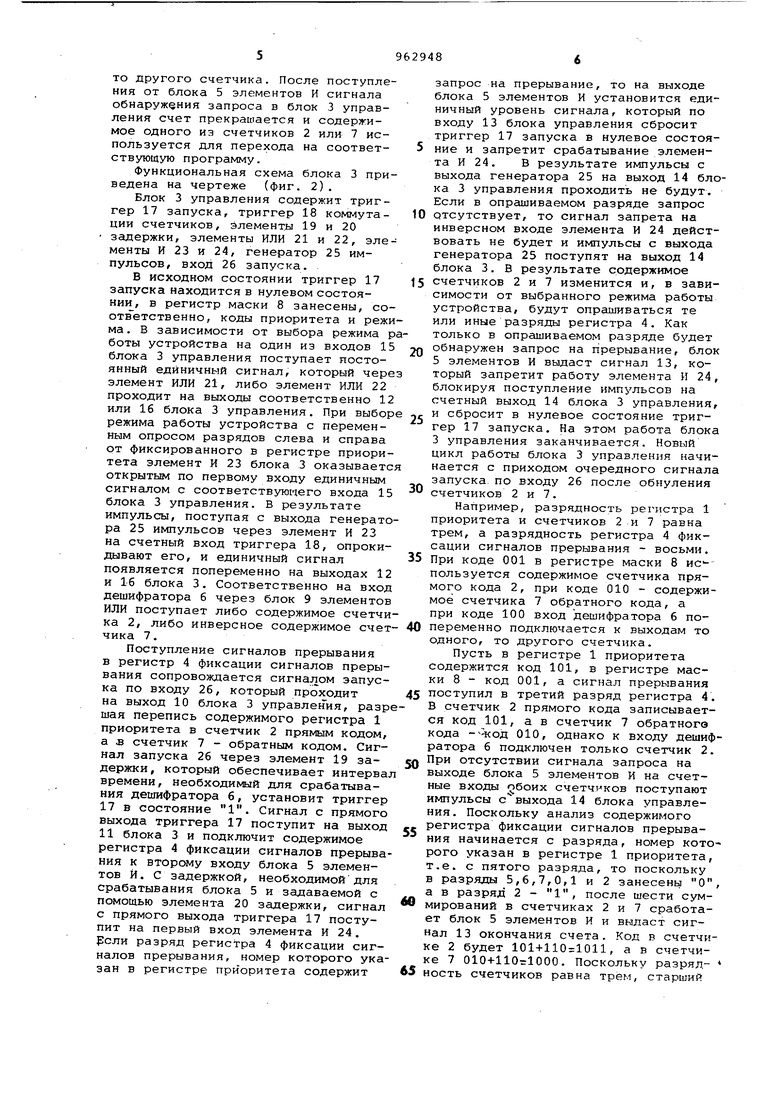

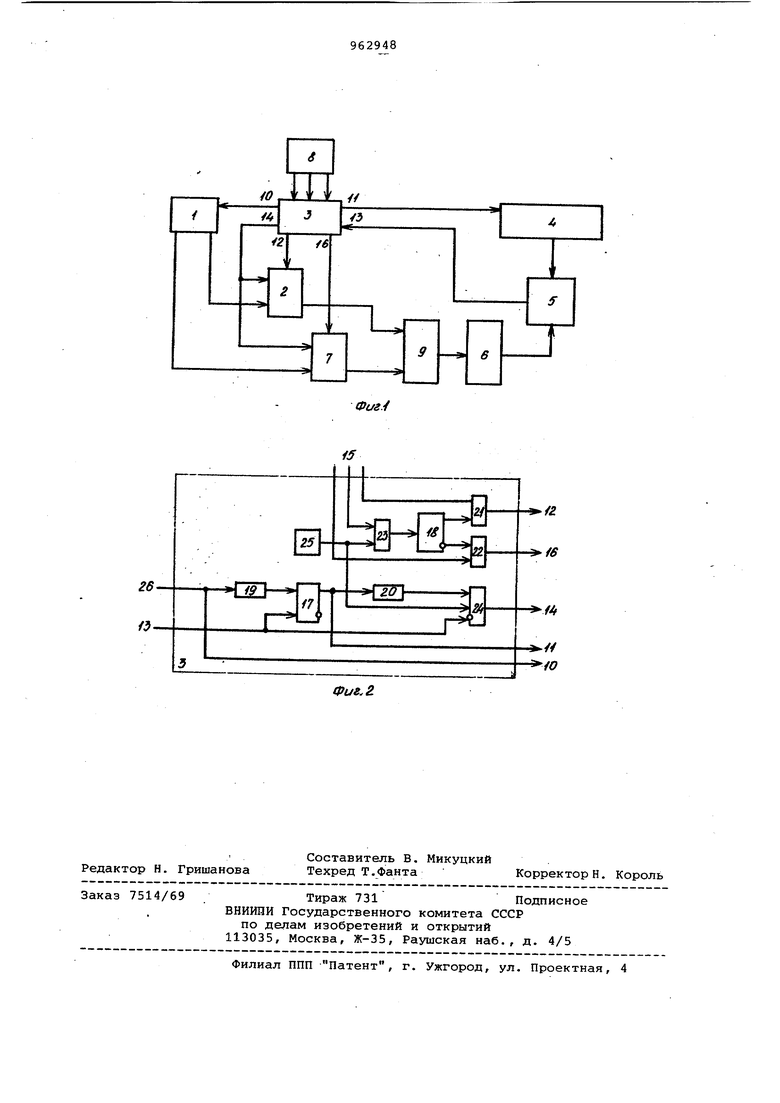

Изобретение относится к вычислительной технике, в частности к устройствам, обеспечивающим переменную приоритетность сигналов прерывания в электронных вычислительных машинах Известно устройство переменного приоритета, содержащее регистр прио ритета, блок управления, счетчик, циклический регистр сдвига ClJ Недостаток устройства - низкое быстродействие, обусловленное сдвигами в циклическом регистре сдвига. Наиболее близким техническим решением к предлагаемому является уст ройство, содержащее регистр приорит та, выход которого соединен с кодовым входом счетчика, блок управления, выходы которого подключены к управляющим входам соответственно регистра приоритета, регистра фикса ции сигналов прерывания и счетчика, схему совпадения, дешифратор. Это устройство позволяет получит удвоенное по сравнению с разрядностью регистра фиксации прерываний число позиций приоритета 2J. Цель изобретения - расширение об ласти применения устройства путем увеличения числа позиций приоритета и сигналов прерывания. Поставленная цель достигается тем, что устройство переменного приоритета, содержащее регистр приоритета, прямой выход которого соединен с кодовым входом счетчика прямого кода, блок управления, первый, второй и третий выходы которого подключены к управляющим входам соответственно регистра приоритета, регистра фиксации сигналов прерывания и счетчика кода, блок элементов И, первый И второй выходы которого соединены с выходами соответственно дешифратора и регистра фиксации сигналов прерывания, а рыход подключен к первому входу блока управления, дополнительно содержит регистр маски, блок элементов ИЛИ и счетчик обратного кода, кодовый вход которого подключен к инверсному выходу регистра приоритета, а счетный вход соединен со счетным входом счетчика прямого кода и с четвертым выходом блока управления, второй, третий и четвертый входы блока управления подключены к выходам регистра маски, а пятый выход соединен с управляющим входом счетчика обратного кода, инверсный кодовый выход которого подключей к первому входу блока элементов или, второй вход которого подключен к прямому кодовому выходу счетчика прямого кода, а выход блок элементов ИЛИ соединен с входом дешифратора. Кроме того, блок управления соде жит первый и второй элементы ИЛИ, первый и второй элементы И, генератор импульсов, первый и второй элементы задержки, триггер запуска и триггер ко1 1мутации счетчиков, прямой и инверсный выходы которого сое динены соответственно с первыми вхо дами первого и второго элементов ИЛ вторые входы которых подключены к второму и четвертому входам блока у равления соответственно, а выходы к третьему и пятому выходам блока управления соответственно, счетный вход триггера коммутации соединен с выходом первого элемента И, первы вход, которого подключен к третьему входу блока управления, а второй вход - к выходу генератора импульсо и к первому прямому входу второго элемента И, второй прямой.вход кото рого соединен с выходом первого эле мента задержки, вход которого соединен с прямым выходом триггера запуска и с вторым входом блока управления, причем установочный вход Триггера запуска соединен с выходом второго элемента задержки, а сбросо вый вход - с первым входом блока управления и и-нверсным входом второ го элемента И, выход которого соединен с четвертые выходом блока управления, а выход второго элемента задержки подключен к первому выходу и к входу запуска блока управления. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема блока управления. Устройство содержит регистр 1 приоритета, прямой выход которого соединен с кодовым входом счетчика прямого кода, блок 3 управления, регистр 4 фиксации сигналов прерыва ния, блок 5 элементов И, входы которого соединены с выходами соответственно регистра 4 и дешифратора 6, счетчик 7 обратного кода, кодовый выход которого подключен к инверсно му выходу регистра 1 приоритета, р.егистр маски 8, блок 9 элементов И1ЛИ, причем выходы 10-12 блока 3 уп равления подключены к управляющим входам регистра 1, регистра 4 и сче чика 2, выход дешифратора б подключен к входу 13 блока 3 управления, счетный вход счетчика 7 соединен со счетным входом счетчика 2 прямого кода и с выходом 14 блока 3 управле ния, а выход регистра маски 8 подключен к входам 15 блока 3, выход 1 которого соединен с управляющим вхо дом счетчика обратного кода 7. Устройство работает следующим образом. В регистр 1 приоритета программно заносится код, определяющий номер того разряда регистра 4 фиксации сигналов прерываний, связанный с которым сигнал прерывания должен иметь наивысший приоритет. Одновременно в один из трех разрядов регистра маски 8 заносится единица, свидетельствующая о выборе одного из трех режимов работы устройства, отличающихся друг от друга последовательностью опроса разрядов прерывания. Опрос производится, начиная от фиксированного в регистре 1 приоритета старшего разряда, либо влево, либо вправо, либо попеременно опрашивается разряд слева и разряд справа от фиксированного. Регистр 4 фиксации сигналов прерывания и счетчики 2 и 7 в исходном состоянии устанавливаются в О. При поступлении одного или нескольких сигналов прерывания соответствующие разряды регистра 4 фиксации сигналов прерывания устанавливаются в 1. При этом выполнение текущей программы приостанавливается и начинает работать блок 3 управления , по сигналам которого содержимое регистра 1 приоритета заносится в счетчик 2 прямого кода прямым кодом и в счетчик 7 обратного кода обратным кодом. По сигналу от блока . 3 управления содержимое счетчика 2 прямого кода или инверсное содержимое счетчика 7 обратного кода через блок 9 элементов ИЛИ поступает на дешифратор 6, выходной сигнал с помощью блока 5 элементов И проверяет наличие 1 .в том разряде регистра 4, номер которого был определен кодом в регистре 1 приоритета. При отсутствии запроса на прерывание в опрашиваемом разряде к содержимому обоих счетчиков 2 и 7, емкость которых равна числу разрядов регистра фиксации сигналов прерываний 4, прибавляется 1. На прямом выходе счетчика 2 будет формироваться возрастающая, а на инверсном выходе счетчика 7 - убывающая последовательности двоичных величин, начиная с кода числа, занесенного на регистр 1 приоритета, пока блок 5 элементов И не выдаст сигнал, свидетельствующего о том, что в оправшиваемом разряде зафиксирован запрос на прерывание. В зависимости от кода, занесенного на регистр маски 8, блок 3 управления выдает управляющие сигналы, по которым на вход дешифратора 6 код может поступать с прямого выхода счетчика 2 прямого кода, с инверсного выхода счетчика 7 обратного кода, либо попеременно с выходов то одного.

то другого счетчика. После поступления от блока 5 элементов И сигнала обнаружения запроса в блок 3 управления счет прекрашается и содержимое одного из счетчиков 2 или 7 используется для перехода на соответствующую nporpai iMy.

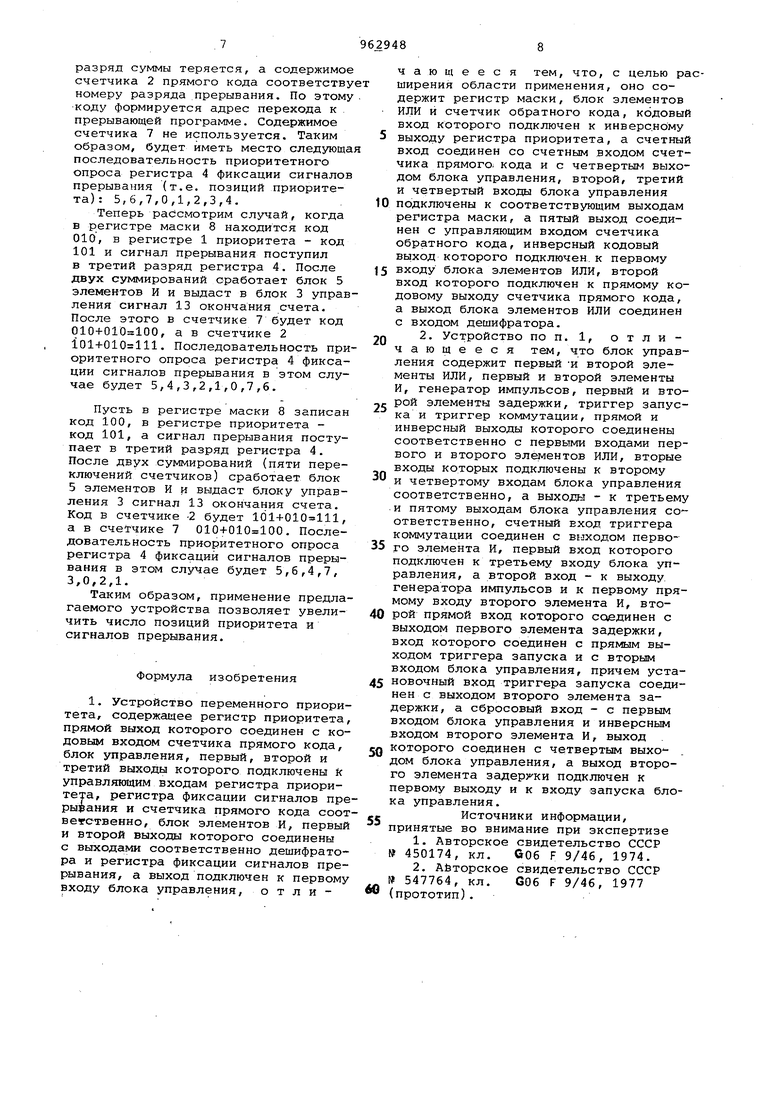

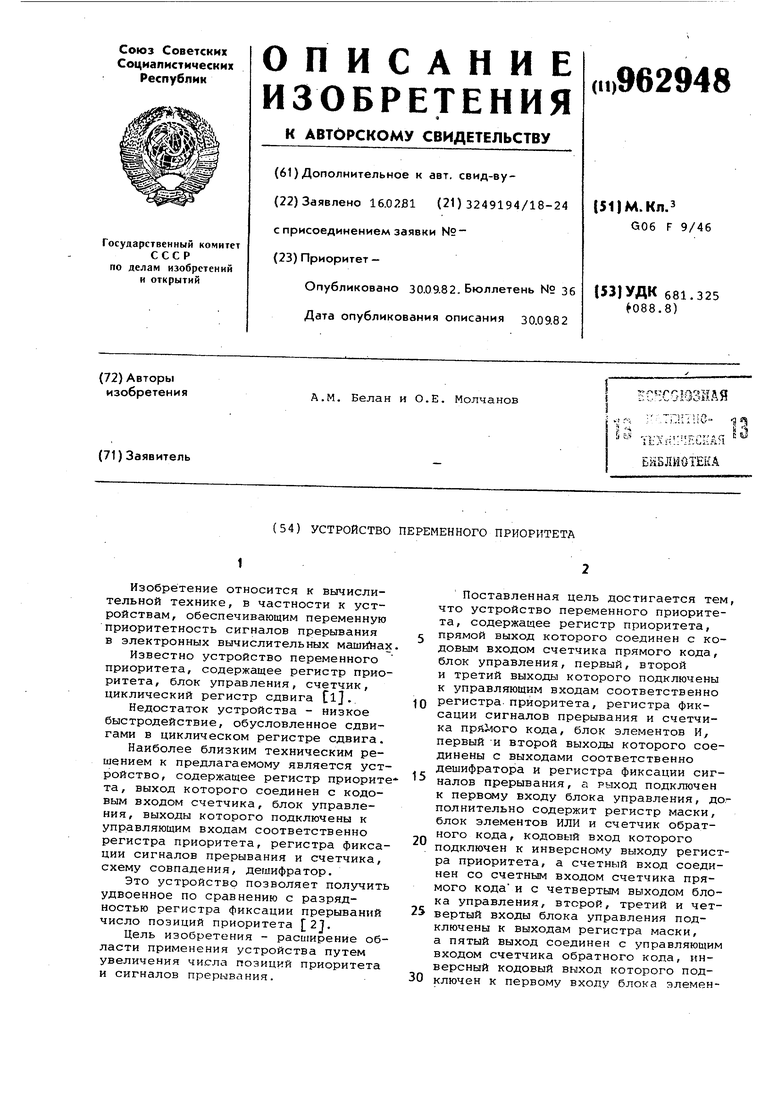

Функциональная схема блока 3 приведена на чертеже (фиг. 2).

Блок 3 управления содержит триггер 17 запуска, триггер 18 комгиутации счетчиков, элементдл 19 и 20 задержки, элементы ИЛИ 21 и 22, элементы И 23 и 24, генератор 25 импульсов, вход 26 запуска.

В исходном состоянии триггер 17 запуска находится в нулевом состоянии, в регистр маски 8 занесены, соотвЪтственно, коды приоритета и режима. В зависимости от выбора режима работы устройства на один из входов 15 блока 3 управления поступает постоянный единичный сигнал, который через элемент ИЛИ 21, либо элемент ИЛИ 22 проходит на выходы соответственно 12 или 16 блока 3 управления. При выборе режима работы устройства с переменным опросом разрядов слева и справа от фиксированного в регистре приоритета элемент И 23 блока 3 оказывается открытым по первому входу единичным сигналом с соответствующего входа 15 блока 3 управления. В результате импульсы, поступая с выхода генератора 25 импульсов через элемент И 23 на счетный вход триггера 18, опрокидывают его, и единичный сигнал появляется попеременно на выходах 12 и 16 блока 3. Соответственно на вход дешифратора 6 через блок 9 элементов ИЛИ поступает либо содержимое счетчика 2, либо инверсное содержимое счетчика 7.

Поступление сигналов прерывания в регистр 4 фиксации сигналов прерывания сопровождается сигналом запуска по входу 26, который проходит на выход 10 блока 3 управления, разрешая перепись содержимого регистра 1 приоритета в счетчик 2 прямым кодом, а в счетчик 7 - обратным кодом. Сигнал запуска 26 через элемент 19 задержки, который обеспечивает интервал времени, необходимый для срабатывания дешифратора 6, установит триггер 17 в состояние 1. Сигнал с прямого выхода триггера 17 поступит на выход 11 блока 3 и подключит содержимое регистра 4 фиксации сигналов прерывания к второму входу блока 5 элементов И. С задержкой, необходимой для срабатывания блока 5 и задаваемой с помощью элемента 20 задержки, сигнал с прямого выхода триггера 17 поступит на первый вход элемента И 24. РСЛИ разряд регистра 4 фиксации сигналов прерывания, номер которого указан в регистре приоритета содержит

запрос на прерывание, то на выходе блока 5 элементов И установится единичный уровень сигнала, который по входу 13 блока управления сбросит триггер 17 запуска в нулевое состояние и запретит срабатывание элемента И 24. В результате импульсы с выхода генератора 25 на выход 14 блока 3 управления проходить не будут. Если в опрашиваемом разряде запрос

0 отсутствует, то сигнал запрета на инверсном входе элемента И 24 действовать не будет и импульсы с выхода генератора 25 поступят на выход 14 блока 3. В результате содержимое счетчиков 2 и 7 изменится и, в зави5симости от выбранного режима работы устройства, будут опрашиваться те или иные разряды регистра 4. Как только в опрашиваемом разряде будет обнаружен запрос на прерывание, блок

0 5 элементов И выдаст сигнал 13, который запретит работу элемента И 24, блокируя поступление импульсов на счетный выход 14 блока 3 управления, и сбросит в нулевое состояние триг5гер 17 запуска. На этом работа блока 3 управления заканчивается. Новый цикл работы блока 3 управления начинается с приходом очередного сигнала запуска по входу 26 после обнуления

0 счетчиков 2 и 7.

Например, разрядность регистра 1 приоритета и счетчиков 2 и 7 равна трем, а разрядность регистра 4 фиксации сигналов прерывания - восьми.

5 При коде 001 в регистре маски 8 используется содержимое счетчика прямого кода 2, при коде 010 - содержимое счетчика 7 обратного кода, а при коде 100 вход дешифратора 6 по0переменно подключается к выходам то одного, то другого счетчика.

Пусть в регистре 1 приоритета содержится код 101, в регистре маски 8 - код 001, а сигнал прерывания поступил в третий разряд регистра 4.

5 В счетчик 2 прямого кода записывается код 101, а в счетчик 7 обратного кода 010, однако к входу дешифратора 6 подключен только счетчик 2. При отсутствии сигнала запроса на

0 выходе блока 5 элементов И на счетные входы обоих счетчиков поступают импульсы с выхода 14 блока управления. Поскольку анализ содержимого регистра фиксации сигналов прерыва5ния начинается с разряда, номер которого указан в регистре 1 приоритета, т.е. с пятого разряда, то поскольку в разряды 5,6,7,0,1 и 2 занесены О, а в разряд 2 - 1, после шести сумвмирований в счетчиках 2 и 7 сработает блок 5 элементов И и выдаст сигнал 13 окончания счета. Код в счетчике 2 будет 101+110 1011, а в счетчике 7 010+110 1000. Поскольку разряд-

5 ность счетчиков равна трём, старший разряд суммы теряется, а содержимое счетчика 2 прямого кода соответству номеру разряда прерывания. По этому коду формируется адрес перехода к прерывающей программе. Содержимое счетчика 7 не используется. Таким образом, будет иметь место следующа последовательность приоритетного опроса регистра 4 фиксации сигналов прерывания (т.е. позиций приоритета): 5,6,7,0,1,2,3,4. Теперь рассмотрим случай, когда в регистре маски 8 находится код 010, в регистре 1 приоритета - код 101 и сигнал прерывания поступил в третий разряд регистра 4. После двух суммирований сработает блок 5 элементов И и выдаст в блок 3 управ ления сигнал 13 окончания счета. После этого в счетчике 7 будет код 010+010 100, а в счетчике 2 101+010 111. Последовательность при оритетного опроса регистра 4 фиксации сигналов прерывания в этом случае будет 5,4,3,2,1,0,7,6. Пусть в регистре маски 8 записан код 100, в регистре приоритета код 101, а сигнал прерывания поступает в третий разряд регистра 4. После двух суммирований (пяти переключений счетчиков) сработает блок 5 элементов И и выдаст блоку управления 3 сигнал 13 окончания счета. Код в счетчике -2 будет 101+010 111, а в счетчике 7 010+010 100. Последовательность приоритетного опроса регистра 4 фиксаций сигналов прерывания в этом случае будет 5,6,4,7, 3,0,2,1. Таким образом, применение предла гаемого устройства позволяет увеличить число позиций приоритета и сигналов прерывания. Формула изобретения 1. Устройство переменного приори тета, содержащее регистр приоритета прямой выход которого соединен с ко довым входом счетчика прямого кода, блок управления, первый, второй и третий выходы которого подключены fc управляющим входам регистра приоритета, регистра фиксации сигналов пр рырания и счетчика прямого кода соо ветственно, блок элементов И, первы и второй выходы которого соединены с выходами соответственно дешифрато ра и регистра фиксации сигналов пре рывания, а выход подключен к первом входу блока управления, о т л и чающееся тем, что, с целью расширения области применения, оно содержит регистр маски, блок элементов ИЛИ и счетчик обратного кода, кодовый вход которого подключен к инверсному выходу регистра приоритета, а счетный вход соединен со счетным входом счетчика прямого, кода и с четвертыг- выходом блока управления, второй, третий и четвертый входы блока управления подключены к соответствующим выходам регистра маски, а пятый выход соединен с управляющим входом счетчика обратного кода, инверсный кодовый вь1ход которого подключен, к первому входу блока элементов ИЛИ, второй вход которого подключен к прямому кодовому выходу счетчика прямого кода, а выход блока элементов ИЛИ соединен с входом дешифратора. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит первый и второй элементы ИЛИ, первый и второй элементы И, генератор импульсов, первый и второй элементы задержки, триггер запуска и триггер коммутации, прямой и инверсный выходы которого соединены соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы которых подключены к второму и четвертому входам блока управления соответственно, а выходы - к третьему и пятому выходам блока управления соответственно, счетный вход триггера коммутации соединен с выходом первого элемента И, первый вход которого подключен к третьему входу блока управления, а второй вход - к выходу генератора импульсов и к первому прямому входу второго элемента И, второй прямой вход которого соединен с выходом первого элемента задержки, вход которого соединен с прямым выходом триггера запуска и с вторым входом блока управления, причем установочный вход триггера запуска соединен с выходом второго элемента задержки, а сбросовый вход - с первым входом блока управления и инверсным входом второго элемента И, выход . которого соединен с четвертым выхо . дом блока управления, а выход второго элемента задержки подключен к первому выходу и к входу запуска блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 450174, кл. G06 F 9/46, 1974. 2.АЁторское свидетельство СССР 547764, кл. G06 F 9/46, 1977 (прототип).

Авторы

Даты

1982-09-30—Публикация

1981-02-16—Подача