О Ч

сл

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переменного приоритета | 1987 |

|

SU1462308A1 |

| Устройство переменного приоритета | 1978 |

|

SU746520A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство переменного приоритета | 1975 |

|

SU547767A2 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Устройство переменного приоритета | 1981 |

|

SU962948A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство переменного приоритета | 1974 |

|

SU506854A1 |

УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА по авт.св. № 506854, личающееся тем, что, с целью расширения функциональных воэможностей за счет организации режима равных приоритетов сигналов прерывания, в него введен триггер режима равных приоритетов, выход которого соединен с третьим входом блока управления, а кодовый выход счетчика с кодовьм входом регистра приоритета, единичный и нулевой входы триггера равных приоритетов соединены соответственно с входом режима равных приоритетов и входом установки в нуль устройства.

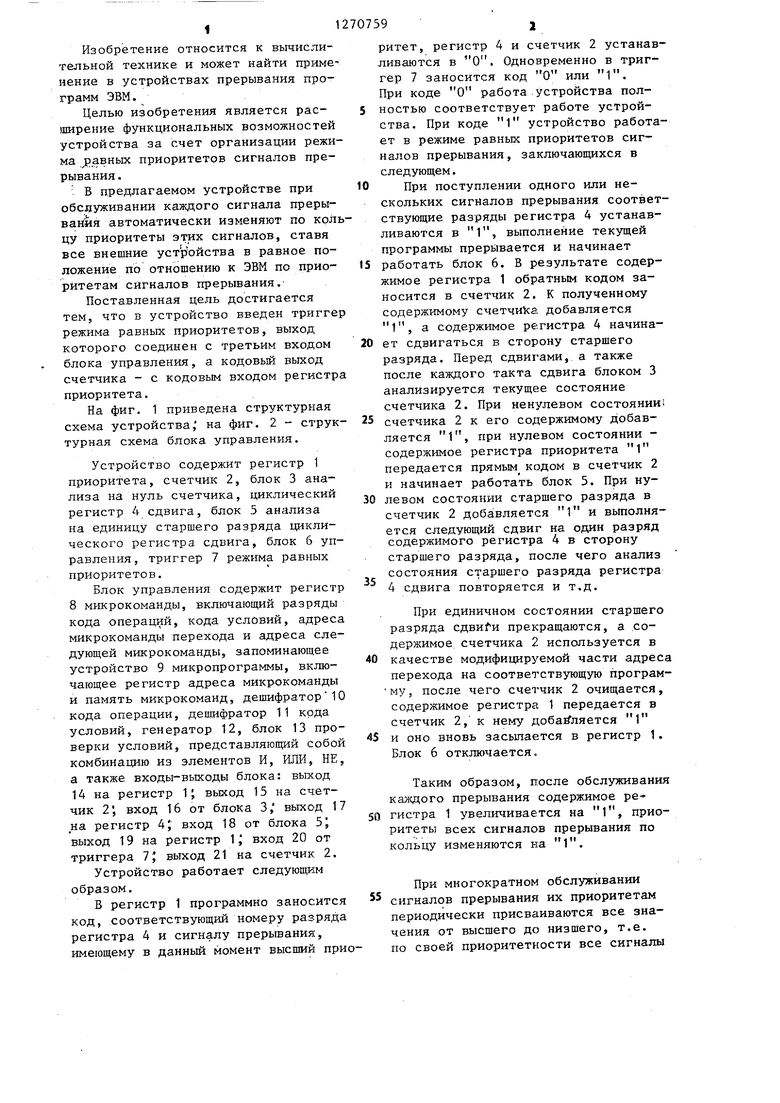

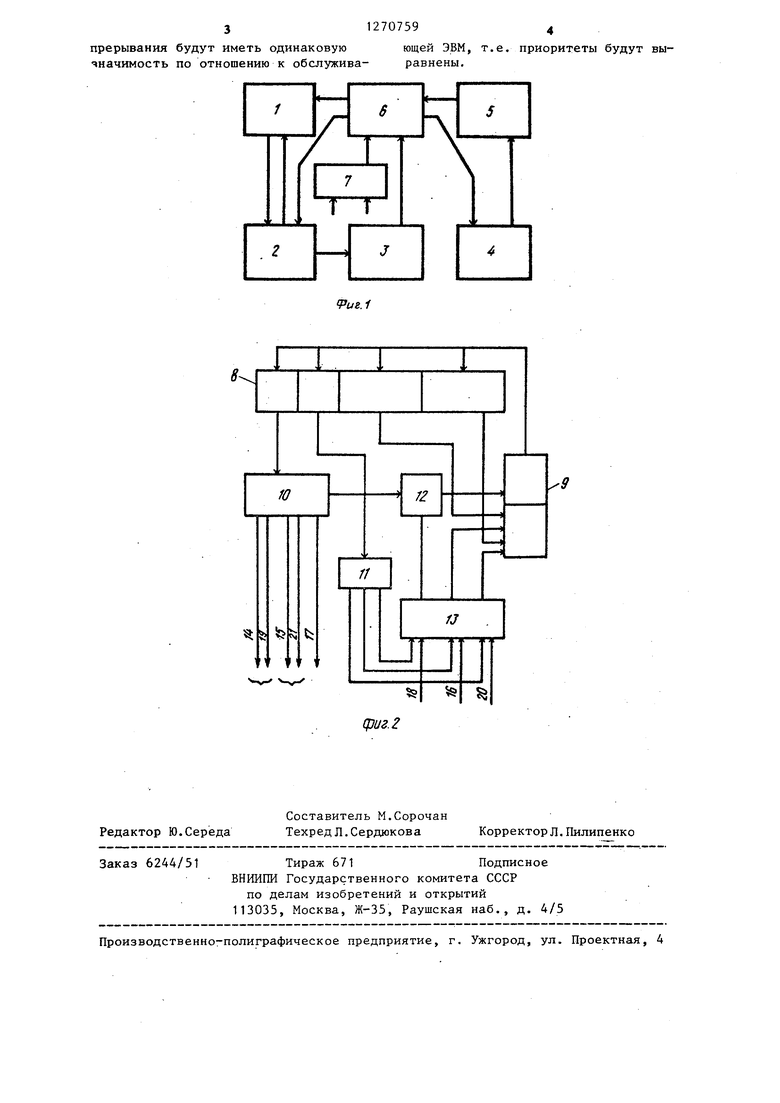

гч: Изобретение относится к вычислительной технике и может найти приме иение в устройствах прерывания программ ЭВМ. Целью изобретения является расширение функциональных возможностей устройства за счет организации режи ма травных, приоритетов сигналов прерывания . . В предлагаемом устройстве при обслуживании каждого сигнала прерывания автоматически изменяют по кол цу приоритеты этих сигналов, ставя все внешние устройства в равное положение по отношению к ЭВМ по приоритетам сигналов прерывания.Поставленная цель достигается тем, что в устройство введен тригге режима равных приоритетов, выход которого соединен с третьим входом блока управления, а кодовый выход счетчика - с кодовым входом регистр приоритета. На фиг. 1 приведена структурная схема устройства, на фиг. 2 - струк турная схема блока управления. Устройство содержит регистр 1 приоритета, счетчик 2, блок 3 анализа на нуль счетчика, циклический регистр 4 сдвига, блок 5 анализа на единицу старшего разряда циклического регистра сдвига, блок 6 управления, триггер 7 режима равных приоритетов. Блок управления содержит регистр 8 микрокоманды, включающий разряды кода операций, кода условий, адреса микрокоманды перехода и адреса следующей микрокоманды, запоминаюш,ее устройство 9 микропрограммы, включающее регистр адреса микрокоманды и память микрокоманд, дешифратор10 кода операции, дешифратор 11 кода условий, генератор 12, блок 13 проверки условий, представляющий собой комбинацию из элементов И, ИЛИ, НЕ, а также входы-выходы блока: 14 на регистр 1J выход 15 на счетчик 2, вход 16 от блока 3, выход 17 на регистр 4J вход 18 от блока 5J выход 19 на регистр 1j вход 20 от триггера 7J выход 21 на счетчик 2. Устройство работает следующим образом. В регистр 1 программно заносится код, .соответствующий номеру разряда регистра 4 и сигналу прерывания, имеющему в данный момент высший при ритет, регистр 4 и счетчик 2 устанавливаются в 0. Одновременно в триггер 7 заносится код О или 1. При коде О работа устройства полностью соответствует работе устройства. При коде 1 устройство работает в режиме равных приоритетов сигналов прерывания, заключающихся в следующем. При поступлении одного или нескольких сигналов прерывания соответствующие разряды регистра 4 устанавливаются в 1, выполнение текущей программы прерывается и начинает работать блок 6. В результате содержимое регистра 1 обратным кодом заносится в счетчик 2. К полученному содержимому счетчика добавляется 1, а содержимое регистра 4 начинает сдвигаться в сторону старшего разряда. Перед сдвигами, а также после каждого такта сдвига блоком 3 анализируется текущее состояние счетчика 2. При ненулевом состоянии; счетчика 2 к его содержимому добавляется 1, при нулевом состоянии содержимое регистра приоритета 1 передается прямым кодом в счетчик 2 и начинает работать блок 5. При нулевом состоянии старшего разряда в счетчик 2 добавляется 1 и вьтолняется следующий сдвиг на один разряд содержимого регистра 4 в сторону старшего разряда, после чего анализ состояния старшего разряда регистра 4 сдвига повторяется и т.д. При единичном состоянии старшего разряда сдвиги прекращаются, а содержимое счетчика 2 используется в качестве модифицируемой части адреса перехода на соответствующую программу, после чего счетчик 2 очищается, содержимое регистра 1 передается в счетчик 2, к нему добавляется 1 и оно вновь засыпается в регистр 1. Блок 6 отклк чается. Таким образом, после обслуживания каяодого прерывания содержимое ре гистра 1 увеличивается на 1, приоритеты всех сигналов прерывания по кольцу изменяются на 1. При многократном обслуживании сигналов прерывания их приоритетам периодически присваиваются все значения от высшего до низшего, т.е. по своей приоритетности все сигналы прерывания яначимость 312707594 будут иметь одинаковую ющей ЭВМ, т.е. приоритеты будут выпо отношению к обслужива- равнены.

Ю

9

72

| Устройство переменного приоритета | 1974 |

|

SU506854A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1986-11-15—Публикация

1984-08-02—Подача