Изобретение относится к вычислительной технике, в частности к устройствам приоритетного обслуживания запросов прерывания, и может быть использовано в цифровых вычислительных машинах.

Цель изобретения - расширение функциональных возможностей устройства за счет задания уровня приоритета для любой линии запросов во всем диапазоне приоритетности.

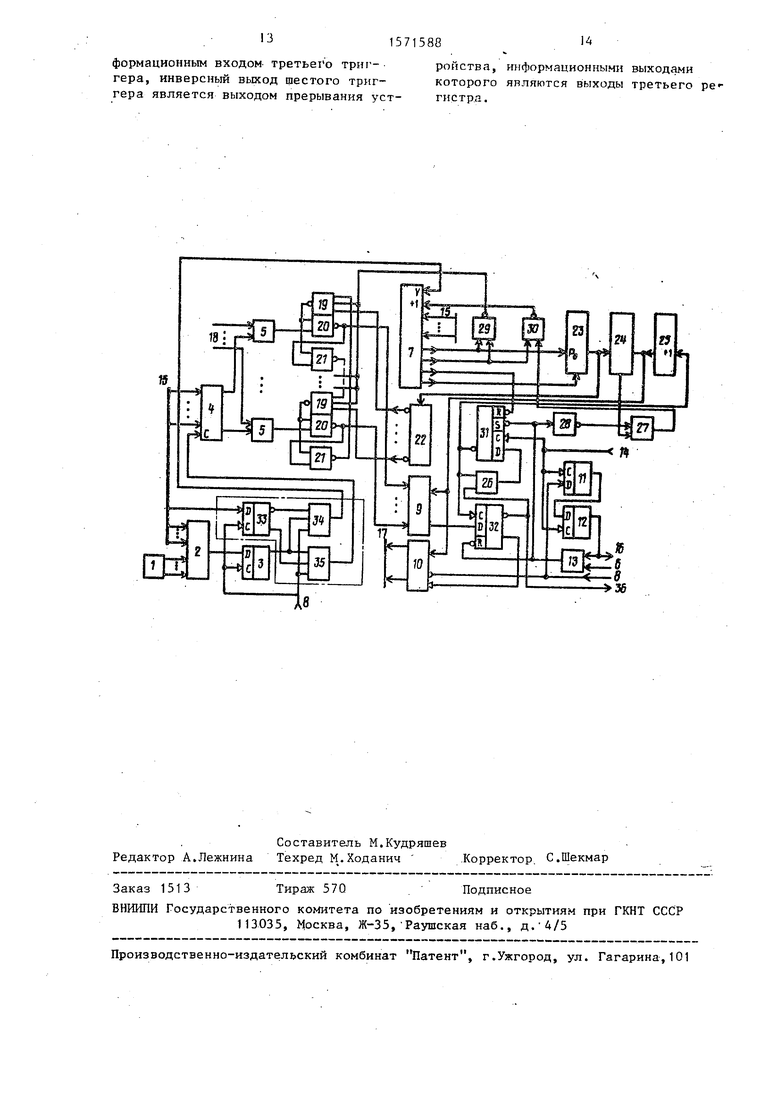

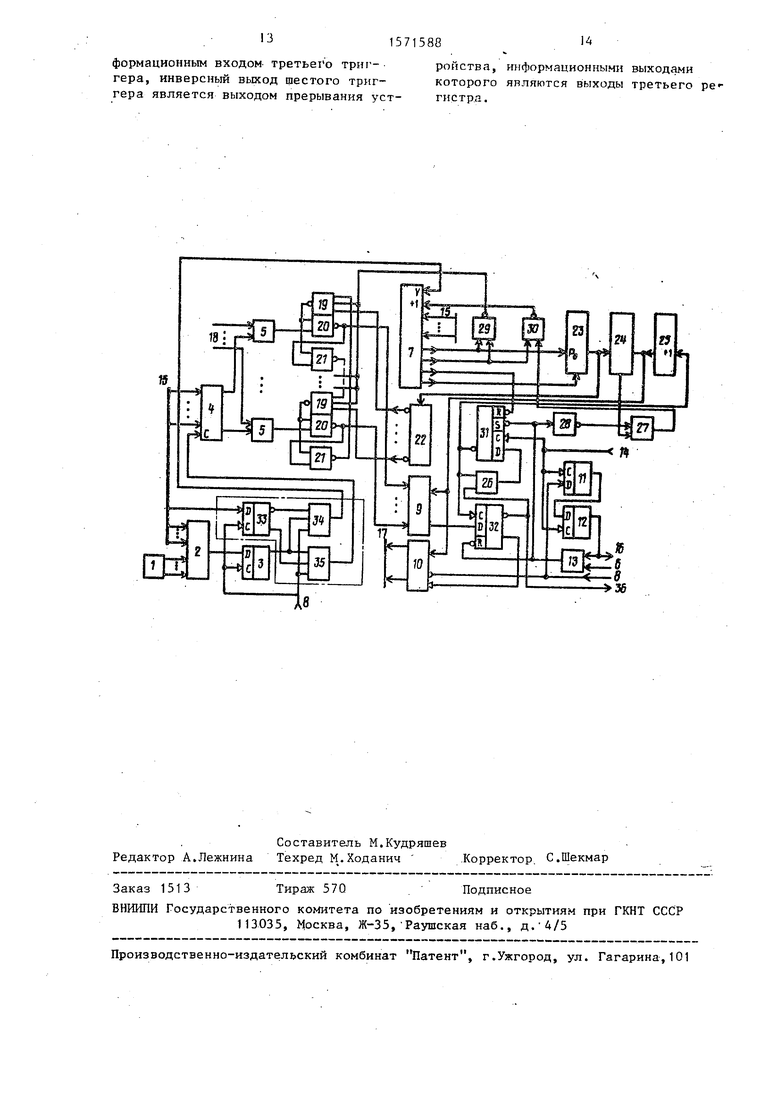

На чертеже приведена структурная схема предлагаемого устройства.

Устройство для обслуживания запросов содержит регистр 1, схему 2 сравнения, триггер 3, регистр 4, группу элементов И 5, вход 6 сброса устройства, блок 7 хранения информации, вход 8 запуска устройства, мультиплексор 9, регистр 10, триггеры 11 и 12, элемент И 13, тактовый вход 14 устройства, группу 15 информационных входов устройства, сигнальный выход 16 устройства, группу 17 информационных выходов устройства, группу входов 18 запросов устройства, группы элементов И-НЕ 19-21, дешифратор 22, сумматор 23, схему 24 сравнения, счетчик 25, элементы И 26 и 27, элемент НЕ 28, элементы И-НЕ 29 и 30, триггер 31,

31 1

СП

00 00

триггеры 32 и 33, элементы И 34 и 35 выход 36 прерывания устройства.

Регистр 1{ представляет собой поле перемычек, подключающих к входам схемы 2 сравнения уровни напряжений О И 1 в такой последовательности, что их совокупность образует двоичный код адреса регистра А маски.

Бпок 7 представляет собой регистр, который функционально является составным и в котором три разряда (младших) предназначены только для записи, а четыре (старших) допускают инкремент и выполнены на основе счетчиков с параллельной записью. Первый из них предназначен только для параллельной записи (т.е. используется как буферный регистр) t а второй производит инкремент по положительному перепаду с выхода элемента И-НЕ 29. Исходная установка счетчиков производится путем записи в них информации о режиме обработки запросов с входов 15.

Устройство работает следующим образом.

Сигналом, подаваемым на вход 6, производятся сброс триггера 32 и установка триггера 31.

По окончании действия сигнала на входе 6 триггер 31 формирует импульсы внутренней синхронизации с частотой в два раза ниже исходной (подаваемой на вход 14). В результате счетчик 25 инкремектирует, а триггер 32 производит запись состояния выхода мультиплексора 9 по каждому импульсу с инверсного выхода триггера 31 (причем в качестве рабочих используются оба фронта импульсов). Синхронно со счетчиком 25 мультиплексором 9 производится последовательная коммутация состояний выходов элементов И-НЕ 20 на информационный вход триггера 32. Как только скоммутированным окажется нулевой уровень напряжения с выхода какого-либо элемента И-НЕ 20 (т.е. сигнал запроса с разрешенной линии), взводится триггер 32. При этом в регистр 10 положительным перепадом сигнала с прямого выхода триггера 32 производится запись состояния счетчика 25 (т.е. определяется переменная часть формата вектора прерывания однозначно соответствующая уровню скоммутированного запроса прерывания) а уровень О, .формируемого на втором входе элемента И 26 с инверсного

0

5

0

5

0

35

40

45

50

55

выхода триггера 32, запрещает дальнейшую генерацию рабочих импульсов триггером 31, который до момента обработки запроса сохраняет свое нулевое состояние.

Низкий уровень напряжения с инверсного выхода триггера 32 поступает на выход 36, извещая ЭВМ о требовании прерывания. Реагируя на него, ЭВМ отвечает процедурой чтения вектора прерывания. Сигнал чтения вектора прерывания низкого уровня с входа 8 поступает на вход выборки регистра 10, коммутируя сформированный вектор на выходы 17. Спустя время задержки (равное периоду частоты синхронизации на входе 14), триггерами 11 и 12 формируется сигнал на выход 16, стробирующий прием в ЭВМ вектора с выходов 17.

По сигналу с выхода триггера 12, поступающему на первый вход элемента И 13, производятся сброс триггера 32 и установка триггера 31, в результате чего сигнал требования прерывания исчезает, а счетчик 25 инкремен- тирует, следовательно, мультиплексор 9 уходит с состояния коммутаций линии с только что обработанным запросом.

Устройство готово к селекции и регистрации нового запроса.

Регистрация запросов с входов 18 производится по правилу, определяемому другими структурными элементами устройства.

Регистрироваться могут запросы лишь тех входов 18, которые не замаскированы регистром 4.

Запись в регистр 4 производится с входов 15 по сигналу с входа 8 (через элемент И 34) в том случае,если адресация к регистру 4 достоверна, т.е. когда код адреса, хранимый в регистре 1, совпадает с выставленным по входам 15 и единичный уровень с выхода схемы 2 сравнения фиксируется триггером 3 стробом адреса, поступающего с входа 8.

Те разряды регистра 4, которые содержат единицу, с помощьк} элементов И 5 размаскируют соответствующие входы 18.

Приоритет обработки запросов размаскированных линий определяется состоянием блока 7. Запись в блок 7 производится анапогично регистру 4, но по сигналу, с ie-дуемому через зле515

мент И 35, Блок 7 имеет адрес, отличающийся от регистра 4 младшим разрядом .

Однозначность обращения к регистрам контролирует триггер 33.

Состояния трех младших разрядов блока 7 однозначно задают режимы работы:

100- фиксация наивысшего приоритета;

101- фиксация наинизшего приоритета;

110- циклический приоритет;

111- бесприоритетный;

ОХХ - останов обработки запросов (X - состояние разряда - может быть любым).

Рассмотрим режим оаботы устройства в указанной последовательности.

Состояние 100 младших разрядов блока 7 соответствует приоритетной обработке запросов с программируемой линией высокого уровня. Номер входа 18, двоичный код которого задается четырьмя старшими разрядами блока 7, в этом режиме является самым высокоприоритетным и, начиная с него, приоритет входов 18 (в последовательном порядке опроса счетчиком 25 мультиплексора 9) убывает.

Будем считать, что блок 7 имеет поразрядное содержимое 0000100, т.е. назначен режим приоритетной обработки, при этом первый вход 18 имеет самый высокий уровень приоритета. В этом случае кодовая комбинация 0000 номера входа 18 поступает на входы сумматора 23 и без изменения (т.е. без инкремента входной информации) подается с выходов сумматора на входы дешифратора 22. Следовательно, на первом выходе дешифратора 22 формируется низкий уровень, а на всех остальных - высокий. Такая совокупность выходных сигналов дешифратора 22 блокирует действие связи: выход элемента И-НЕ 21 последнего по приоритету на первый вход элемента И-НЕ 19 первого по приоритету, а значит, состояние последнего входа 18 не влияет на логику блокирования запросов с первого входа 18.

Состояние всех остальных входов 18 определяется по правилу: запросы каждого последующего входа 18 могут восприниматься устройством только при отсутствии запросов на всех предшествующих.

5886

Как только по выходу первого элемента И 5 появляется высокий уровень запроса, на выходе первого элемента И-НЕ 20 возникает низкий уровень напряжения, поступающий как на первый вход мультиплексора 9 (это состояние может фиксироваться триггером 32, когда счетчик 25 опроса входов нахо0 дится в нулевом состоянии), так и на второй вход элемента И-НЕ 21, соответствующего первому входу 18, в результате чего на выходе элемента И-НЕ 21 появляется высокий уррвень

5 напряжения, который, поступая на первый вход элемента И-НЕ 19 следующего входа 18, вызывает появление логического нуля на первых входах элементов И-НЕ 70 и 21, блокирующего

0 размаскированные запросы. Блокирование каждой последующей линии логически осуществляется присутствием высоких уровней по входам элемента И-НЕ 19, которые поступают от трех различ5 ных источников: на первый вход - с выхода предыдущего элемента И-НЕ 21, на второй вход - с выхода элемента И-НЕ 29 (низкий выходной сигнал которого появляется только в режиме

0 бесприоритетной обработки запросов), а на третий вход - с соответствующего выхода дешифратора 22, единичное значение которого сохраняется до тех пор, пока данный выход не адресует

5

запрос с наивысшим приоритетом.

Таким образом, сигнал низкого . уровня присутствует только на выходе первого элемента И-НЕ 20, а для всех остальных элементов И-НЕ 20 их

0 выходы имеют высокие уровни. Следовательно, не важно, в каком состоянии находится счетчик 25, а важно, что только при его состоянии 0000 на выходе мультиплексора 9 появляется

с низкий уровень сигнала, соответствующий наиболее приоритетному запросу, который и фиксируется триггером 32. Как только триггер 32 зафиксирует сигнал запроса прерывания, он

п взводится, а с его инверсного выхода на выход 36 поступает сигнал требования прерывания. Одновременно блокируется через элемент И 26 дальнейшее изменение состояния триггера 31, который продолжает находиться в нулевом состоянии. При установке триггера 32 на его прямом выходе формируется положительный перепад сигнала, по которому в регистр 10 производится запись состояния счетчика 25 (в данном случае состояние 0000),

Такое состояние сохраняется до процедуры чтения вектора прерывания, назначаемой ЭВМ после восприятия выставленного триггером 32 требования.

Сигнал чтения вектора прерывания низкого уровня поступает с входа 8 на вход выборки регистра 10 и на информационный вход триггера 11. Следовательно, сформированный ранее вектор прерывания оказывается скоммути- рованным на выход 17, а затем через время, формируемое триггерами 11 и 12 стробируется в ЭВМ сигналом квитирования с выхода триггера 12.

Сигнал квитирования через элемент И 13 производит исходную установку в единичное состояние триггера 31 и в нулевое триггера 32, в результате че- I го счетчик 25 производит инкремент, но триггер 31 продолжает формирование рабочих импульсов синхронизации толь- ко по окончании действия сигнала квитирования.

Так как ЭВМ приняла вектор прерывания, соответствующий самому приоритетному запросу, запрос на пре- рывание по этому входу может быть снят.

По окончании действия сигнала квитирования устройство продолжает работу по регистрации и фиксации за- просов прерывания.

Аналогично работает устройство при назначении в качестве самого высокоприоритетного входа 18 с другим порядковым номером.

Состояние 101 младших разрядов блока 7 соответствует приоритетной обработке запросов с программируемой (задаваемой) линией низкого приоритета.

В этом режиме, начиная с задаваемого в порядке, обратном последовательности счета счетчика 25, приоритет входов 18 возрастает, а самым

ВЫСОКОПрИОрИТеТНЫМ СТаНОВИТСЯ ВХОД

18, имеющий номер на единицу больше, чем заданный.

Допустим, что шестой вход 18 (код 0110) задан в качестве входа с самым низким приоритетом.

В этом случае кодовая комбинация номера шестого входа 18 поступает на входы сумматора 23, вход переноса которого принудительно удерживается

0

$

0

5

Q

5

в состоянии логической единицы младшим разрядом блока 7 (так как код режима 101). Инкрементированное значение с выходов сумматора 23 (в данном случае это комбинация 0111) поступает на входы дешифратора 22. Следовательно, на восьмом выходе дешифратора 22 формируется низкий уровень, а на всех остальных - высокий. Тогда выход элемента И-НЕ 21, соответствующий последнему по приоритету входу 18, не оказывает влияния на логику (элементы И-НЕ 20 и 21) блокирования запросов с седьмого входа 18 (так как третий вход элемента И-НЕ 19 для линии этого входа подключен к восьмому выходу дешифратора 22) и устройство производит приоритетную обработку запросов соответственно самыми высоко- и низкоприоритетными.Устройство в этом режиме работает аналогично рассмотренному.

Работа устройства незначительно меняется в режиме 110 (циклическая обработка запросов). В этом случае приоритет входов 18 изменяется последовательно по кругу (циклически): после обработки текущего запроса с самым высоким приоритетом его статус изменяется на противоположный, а уровень наивысшего приоритета приобретает вход 18 со следующим порядковым номером, т.е. происходит сдвиг приоритетного распределения линий запросов. В этом режиме устройство работает следующим образом. Единичное значение второго разряда блока 7 удерживает первый выход .элемента И-НЕ 30 под высоким логическим уровнем напряжения, в результате чего на выходе этого элемента по окончании сигнала квитирования (по цепи его следования элемент И 13, элемент НЕ 28, элемент И 27) формируется сигнал инкременти- рования номера входа 18 в регистр 7, а значит, происходит сдвиг приоритетности линий запросов. Сигнал ин- крементирования блока 7 формируется при обработке только того запроса, который соответствует самой приоритетной линии. Если обнаруженный (благодаря опросу счетчиком 25 состояний входов мультиплексора 9) и зафиксированный (триггером 32) запрос не принадлежит высокоприоритетной линии (определяемой четырьмя старшими разрядами блока 7 через сумматор 23 и дешифратор 22), то коды номеров входов ТЯ с выходов сумматоров 23 и счетчика 25, поступающие на входы схемы 24 сравнений, не совпадают и с выхода не появляется сигнал сравнения единичного уровня, в результате чего сигнал квитирования, формируемый устройством в процедуре чтения вектора прерывания, инвертируясь элементом НЕ 28, не вызывает появления сигнала высокого уровня на выходе элеме н- та И 27, а следовательно, инкремент блока 7 не производится.

При фиксации самого высокоприоритетного запроса состояние счетчика 25 совпадает с номером этой линии и на второй вход элемента И 27 с выхода схемы 24 поступает высокий уровень напряжения, который разрешает прохождение сигнала квитирования единичного уровня с выхода элемента НЕ 28 че- /рез элемент И 27 на второй вход элемента И-НЕ 30. Так как эта процедура имеет место и в других режимах устройства, то необходимо ее использовать только для режима циклической обработки запросов, назначаемой комбинацией 110 трех младших разрядов блока 7. Это достигается наличием элемента И-НЕ 30, у которого первый вход подключен к второму разряду блока 7.Следовательно, сигнал инкрементирования блока 7 низкого уровня может появляться с выхода элемента И-НЕ 30 только при наличии единичного значения во втором разряде блока 7,т.е. как раз только в режиме циклической обработки запросов прерывания.

Режим бесприоритетной (равновероятностной) обработки запросов назначается устройству кодовой комбинацией 111 по трем младшим разрядам блока 7. В этом режиме приоритетный механизм селекции запросов выключен. Единичное значение двух младших разрядов блока 7 узнается элементом И-НЕ 29, благо- даря чему на его выходе в этом режиме всегда присутствует низкий уровень напряжения, удерживающий по вторым входам элементов И-НЕ 19 единичные значения уровней их выходов, в результате чего сигнал запроса по незамаскированному входу 18 с выхода каждого предыдущего элемента И 5 не может блокировать сигнал запроса с выхода каждого последующего элемента И 5.

Так, если по выходу элемента И 5, соответствующему первому входу 18, появляется сигнал запроса единично7158810

го уровня, то на выходе элемента И-НЕ 20, первый вход которого удерживается элементом И-НЕ 19 в единичном

, значении, возникает низкий уровень напряжения, который, инвертируясь через элемент И-НЕ 21, не может привести выход элемента И-НЕ 19 для последующего входа 18 в состояние лоЮ гического нуля, в результате чего второй вход элемента И-НЕ 20 для последующего входа 18 не может изменять в рассматриваемом режиме своего единичного состояния.

15 Следовательно, на мультиплексор 9 поступают все реально существующие запросы с немаскируемых входов 18, которые фиксируются триггером 32 при их коммутации .мультиплексором 9.Счет20 чик 25 производит останов последовательного счета только тогда, когда регистрируется запрос, и продолжает счет с состояния останова после выполнения процедуры чтения вектора

25 прерывания.

Режим временного останова существует при нулевом значении третьего разряда блока 7. Состояния остальных разрядов блока 7 на работу уст30 ройства в этом режиме влияния не оказывают.

В этом режиме нулевое состояние третьего разряда удерживает триггер 31 в нулевом состоянии, следовательно, триггер не генерирует рабочие импульсы синхронизации, а значит, опрос и регистрация запросов не производятся.

Такое состояние существует до тех пор, пока не изменится состояние третьего разряда блока 7. Как только оно становится единичным, устройство продолжает свою работу в режиме, определяемом двумя младшими разрядами блока 7.

35

40

45

Формула изобретения

Устройство для обслуживания запросов, содержащее блок хранения информации, два регистра, первую схему „ сравнения, два триггера, мультиплексор, пять элементов И, группу элементов И, причем информационные входы первого регистра и блока хранения информации и первая группа входов первой схемы сравнения соединены с группой информационных входов устройства, вторая группа входов первой схе11

1571

мы сравнения подключена к выходам второго регистра, выход первой схемы сравнения подключен к информацией ому входу первого триггера, такто- ый вход которого подключен к такто- ому входу устройства,выходы первого регистра подключены к первым входам элементов И группы, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет задания уровня при- эритета для любой линии запросов во зсем диапазоне приоритетности, в него введены три группы элементов И-НЕ5 третий регистр, третий, четвертый, пятый,и шестой триггеры, элемент НЕ„ (дешифратор, сумматор, вторая схема (сравнения, счетчик и два элемента и-НЕ, причем каждый запросный вход устройства соединен с вторым входом одноименного элемента И группы, выход каждого элемента И группы соединен с первым входом одноименного элемента И-НЕ первой группы, второй вход каждого элемента И-НЕ первой группы и первый вход каждого элемента И-НЕ второй группы соединены с выходом одноименного элемента И-НЕ третьей группы, второй вход каждого элемента И-НЕ второй группы соединен с выходом одноименного элемента первой группы, первый вход каждого элемента И-НЕ третьей группы, начиная с второго, соединен с выходом одноименного элемента И-НЕ второй группы, первый вход первого элемента И-НЕ третьей группы соединен с выходом последнего элемента И-НЕ второй группы, вторые входы элементов И-НЕ третьей группы соединены с выходом первого элемента И-НЕ, третий вход каждого элемента И-НЕ третьей группы соединен с одноименным выходом дешифратора, группа входов которого соединена с группой выходов сумматора и первой группой входов второй схемы сравнения вторая группа входов которой соединена с группой выходов счетчика и группой адресных входов мультиплексора, информационные входы которого соединены с выходами элементов И-НЕ первой группы, тактовые входы первого и второго триггеров и первые входы первого и второго элементов И соединены с входом запуска устройства, тактовые входы третьего, четвертого и пятого триггеров соединены с тактовым входом устройства, прямой вы8812

ход первого триггера соединен с вторыми входами первого и второго элементов И, инверсный и прямой выходы второго триггера соединены соответственно с третьими входами первого и второго элементов И, выходы которых соединены соответственно с входами управления, записью блока хранения информации и входом синхронизации первого регистра, информационный вход второго триггера соединен с соответствующим входом группы информационных входов устройства, счетg ный вход блока хранения информации соединен с выходом второго элемента И-НЕ, группа входов сумматора соединена с группой выходов блока хранения информации, первый разрядный выход

0 которого соединен с входом сумматора и первым входом первого элемента И-НЕ, второй вход которого и первый вход второго элемента И-НЕ соединены с вторым разрядным выходом блока хра5 нения информации, третий разрядный выход которого соединен с входом

Л.

сброса третьего триггера, вход установки в 1 которого соединен с выходом третьего элемента И и через элемент НЕ с первым входом четвертого элемента И, второй вход которого соединен с выходом второй схемы сравнения, выход четвертого элемента И соединен с вторым входом второго элемента И-НЕ, выход четвертого триггера соединен с информационным входом пятого триггера, выход которого является сигнальным выходом устройства и соединен с первым входом третьего элемента И, второй вход и выход которого соединены соответственно с вхо- / дом сброса устройства 1и входом сброса шестого триггера,прямой выход которого соединен с входом синхронизации третьего регистра,вход управления записью которого соединен с входом запуска устройства и информационным входом четвертого триггера, группа информационных входов третьего регистра соединена с группой выходов счетчика, информационный вход шестого триггера соединен с выходом мультиплексора, тактовый вход шестого триггера соединен с инверсным выходом третьего триггера, первым входом пятого элемента И и счетным входом счетчика, инверсный выход шестого триггера со единен с вторым входом пятого элемента И, выход которого соединен с ин0

5

0

0

5

формационным входом третьего триггера, инверсный выход шестого триггера является выходом прерывания устройства, информационными выходами которого являются выходы третьего ре гистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| УСТРОЙСТВО ПРИОРИТЕТНЫХ ПРЕРЫВАНИЙ | 1991 |

|

RU2006920C1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1550518A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Многоканальное программное задающее устройство | 1986 |

|

SU1383297A1 |

Изобретение относится к вычислительной технике, в частности к устройствам приоритетного обслуживания запросов прерывания, и может быть использовано в цифровых вычислительных машинах. Цель изобретения - расширение функциональных возможностей за счет задания уровня приоритета для любой линии запросов приоритетности. Устройство для обслуживания запросов содержит три регистра, две схемы сравнения, шесть триггеров, три группы элементов И-НЕ, элемент НЕ, дешифратор, сумматор, счетчик, группу элементов И, блок хранения информации и пять элементов И. В устройстве обеспечивается такой механизм изменения приоритетной обработки запросов, который предусматривает не только смену приоритетности типа самый старший уровень запросов становится самым младшим (циклический приоритет обработки), но и обеспечивает программирование любой линии запросов в качестве самой высокоприоритетной или в качестве самой низкоприоритетной. Данное устройство реализует безприоритетный (равновероятностный) режим обработки и временный останов обработки запросов. 1 ил.

75

3б

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1277107A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1283768A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-15—Публикация

1988-11-02—Подача