Изобретение относится Е шшуль сной технике.

Известен счетчик импульсов, со-держащий элеиентарные счетяики рдинаковой разрядности со схеиой ЯЛИ на входе, триггер со схемой И if на единичное выходе, элеиент задержки и узел контроля нулевого состояния устройства, причеи первы входы схеи МЛИ соединены с выходом схеш И, вход которой соединен с шиной входных импульсов контроля, выход переноса каждого элементарного счетчика соединен с вторым входом схемы ИЛИ последующего элементарного счетчика, единичный :вход триггера соединен с шиной контроля.

Целью изобретения является повышение полноты мсокращения времени контроля и расширение функциональных возможностей устройства.

Для этого оно дополнительно содержит многовходовую схему МИ, входы которой соединены с выходами

1пёреноса элементарных счетчиков, а выход соединен с нулевым входом тр1иггера, выход схемы И соединен с первым входом схемы ИЛИ первого

5 элементарного счетчика через элв. мент задержки, шина контроля дополнительно соединена с входами установки нуля старших разрядов всех элементарных счетчиков, с входами

0 установки нуля младших разрядов всех элементарных счетчиков, кроме первого, и с входами установки единицы всех остальных разрядов элементарных счетчиков.

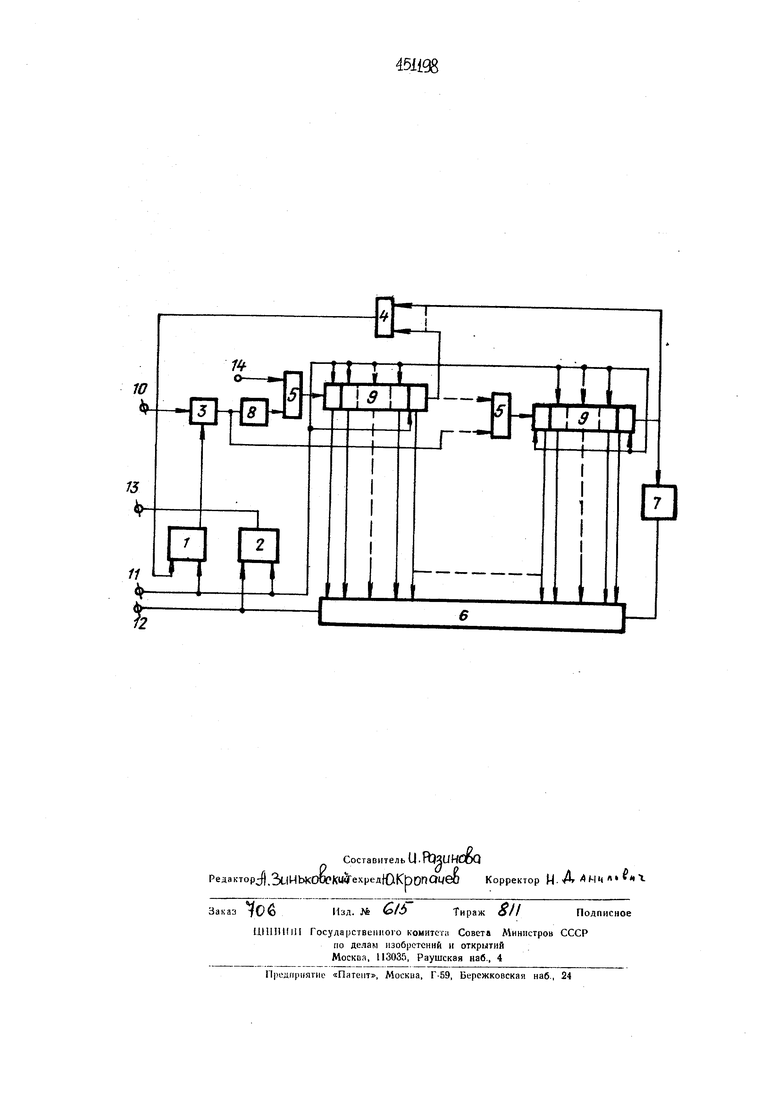

5 На чертеже приведена функциональная блок схема счетчиков.

Счетчик импульсов содержит триггеры , 2, схему И 3, многовходовые схемы ИЛИ ч, 5, много0 входовую схему И б, элементы за-, держки 7,8, элементарные счетчики 9 одинаковой разрядности, шину входных импульсов контроля iO, ШИНУ

контроля li, шину исправно 12, 1ШИНУ неисправно 13. вхол сч15тчи5 |Ш|1ну неисправно ка в режиме раооты после окончания проверки i4. Счетчик работает следующим обра ри поступлении сигнала на шину 11 триггеры I и 2 устанавливаются в состояние 1, в первом счетчике 9 устанавливается число , где т- число разрядов элементарного счетчика, а в осталь ных счетчиках У устанавливается числоМа г --Я Схема И 3 открывается и пропускает входные импульсы на входы всех счетчиков 9 После поступления на шину J-O числа импульсов, равного 2 - , в первом счетчике S будет зафиксировано число , а в остальных счетчиках - число , Следующий импульс входной часто ты устанавливает все счетчики 9. кроме первого, в состояние , а при поступлении импульса с выхода элемента 8 на выходе первого счетчика 9 формируется импульс переполнения, который вызывает переполнение всех остальных счетчиков 9, В результате все разряды счетчиков 9 устанавливаются в состояние О, Импульс переполнения с выхода первого счетчика 9 поступает через схему ИЛИ 4 на нулевой вход триггера -t, Схема И 3-закрывается, и поступление входных импульсов на входы счетчиков 9 прекращается. Импульс переполнения последнего счетчика задерживается элементом 7 на время I, где Т - период следования входных импульсов. ЕСЛИ все разряды счетчика установлены в 6 открыта то схема состояние и импульс с выхода элемента v поступает на ШИНУ 12 и на нулевой вход триггера 2. ЕСЛИ вследствие неисправности не будет установлен в состояние V какои либо разряд счетчика 9 или триггер I, то сигнал на выходе схемы б не формируется, триггер 2 остается в состоянии 1 и с шины ХЗ можно снять сигнал неисправно. При форшровании ложного импульса переполнения в каком либо счетчике 9 триггер 1 будет установлен в состояние О, и поступление входных иипульсов на входы счетчиков прекращается, следствие этого импульс на выходе схемы И 6 не формируется и триггер .2 остается в состоянии 1. ПРЕДМЕТ ИЗОБРЕТЕНИЯ Счетчик импульсов, содерасащий элементарные счетчики одинаковой разрядности со схемой ИЛИ на входе, триггер со схемой И на единичном выходе, элемент задержки и узел контроля нулевого состояния устройства, причем первые входы схем МИ соединены с выходом схемы И, вход которой соединен с шиной входных импульсов контроля, выход переноса каждого элементарного счетчика соединен с вторым входом схемы ИЛИ последующего элементарного счетчика, единичный вхцд триггера соединен с шиной контроля, отличающийся тем, что, с целью повышения полноты и сокращения времени контроля и расширения функциональных возможностей устройства, оно дополнительно содержит многовходовую схему ШШ, входы которой соединены с выходами переноса элементарных счетчиков, а выход соединен с нулевым входом триггера, выход схемы И соединен с первым входом схемы ИЛИ первого элементарного счетчика через элеибнг задержки, шина контроля дополнительно соединена с входами установки нуля старших разрядов всех элементарных счетчиков, с входами установки нуля младшихразрядов всех элементарных счетчиков, кроме первого, и с входами установки едивицы всех остальных разрядов эле- i ментарных счетчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Преобразователь двоичного кода в число-импульсный код | 1977 |

|

SU734671A1 |

| Устройство для контроля -разряд-НОгО СчЕТчиКА | 1979 |

|

SU839060A1 |

| Двоичный счетчик с контролем ошибок | 1981 |

|

SU970704A1 |

| Устройство для контроля @ -кодов Фибоначчи | 1984 |

|

SU1203711A1 |

| Генератор равномерно распределенных псевдослучайных чисел | 1977 |

|

SU674007A2 |

| Двоичный счетчик с контролем ошибок | 1983 |

|

SU1121781A2 |

| Счетчик с контролем | 1988 |

|

SU1649523A1 |

| Устройство для формирования серий импульсов | 1984 |

|

SU1166280A1 |

| Устройство для контроля блоков памяти | 1988 |

|

SU1631608A1 |

Авторы

Даты

1974-11-25—Публикация

1972-09-08—Подача