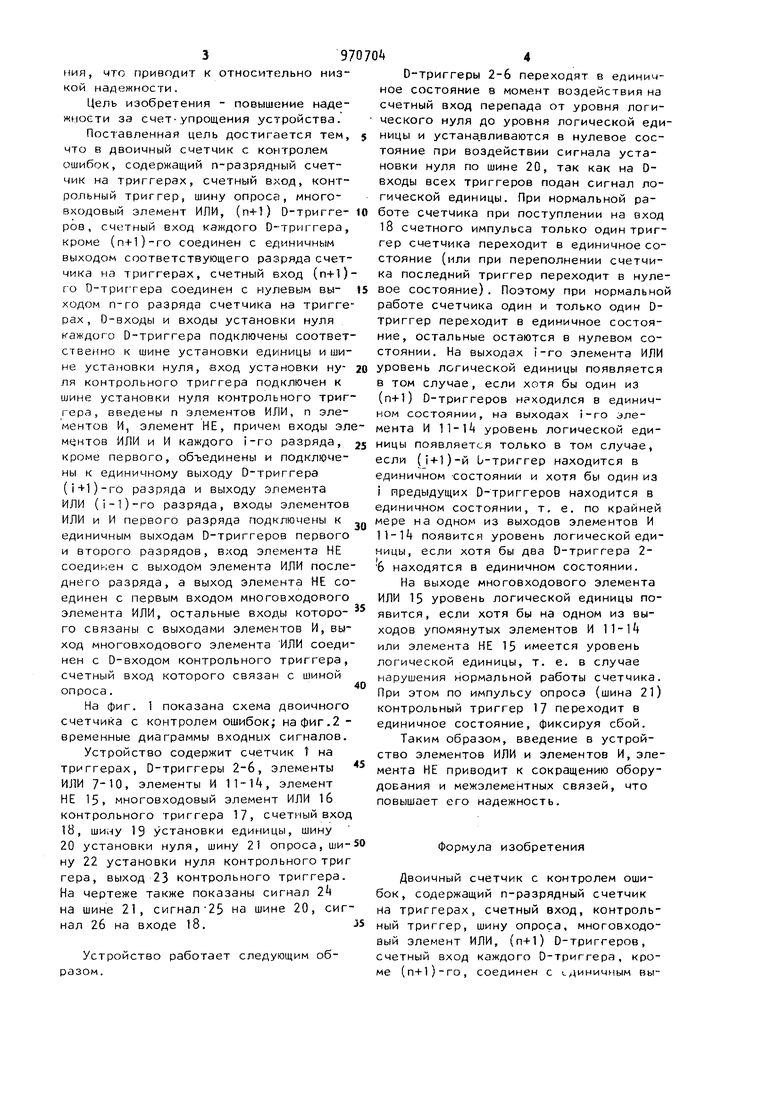

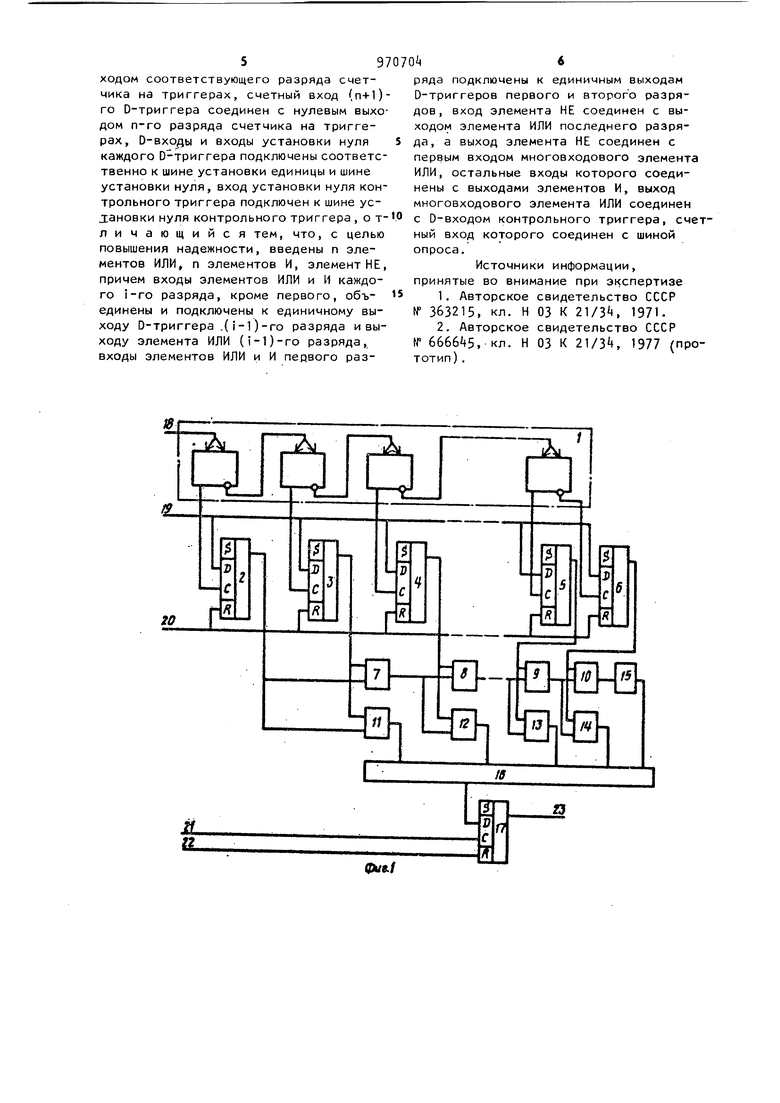

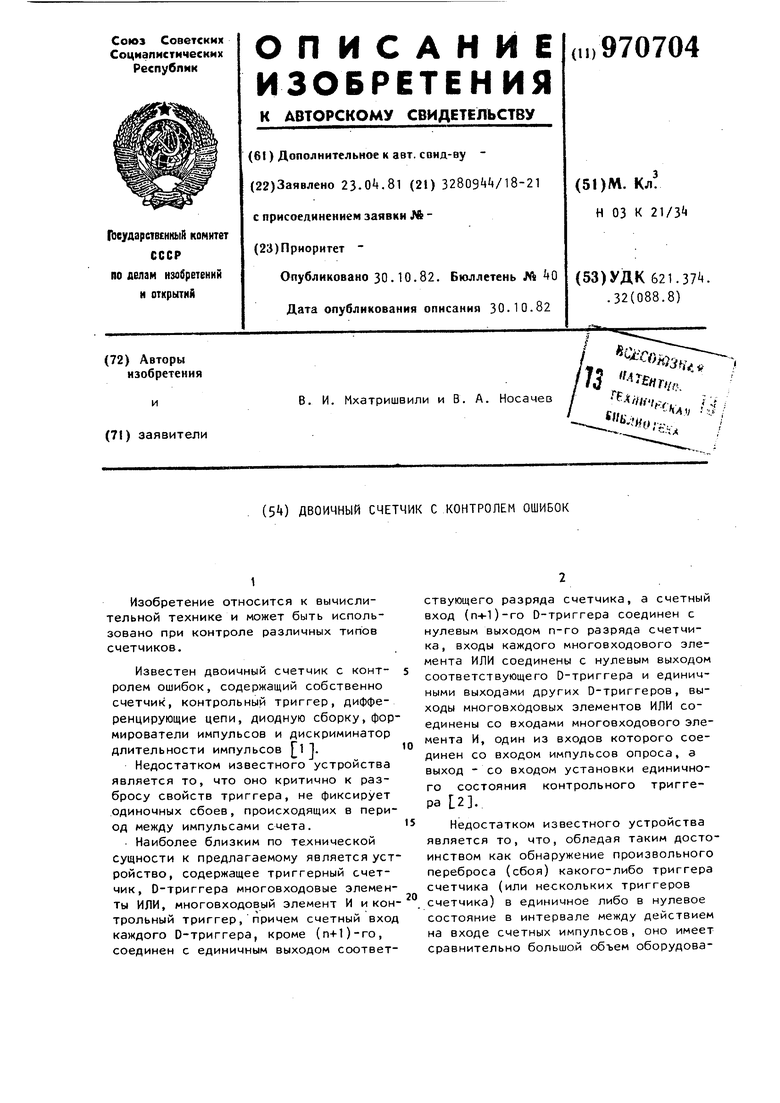

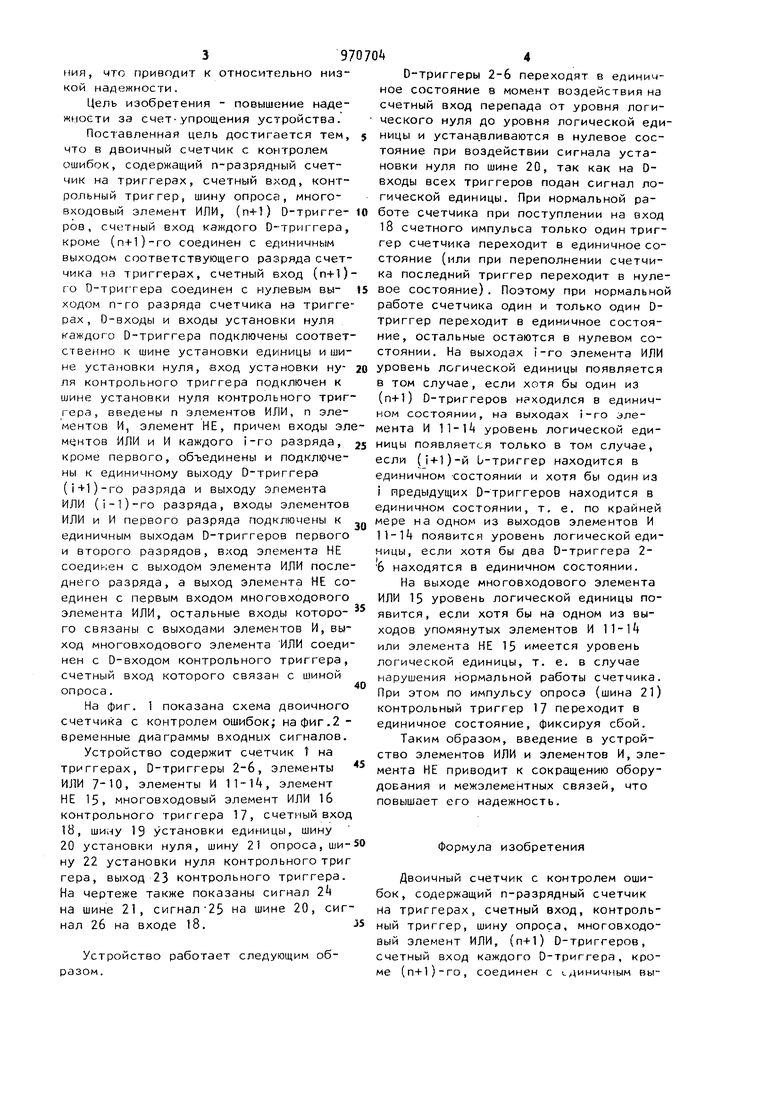

Изобретение относится к вычислительной технике и может быть использовано при контроле различных типов счетчиков. Известен двоичный счетчик с контролем ошибок, содержащий собственно счетчик, контрольный триггер, дифференцирующие цепи, диодную сборку, фор мирователи импульсов и дискриминатор длительности импульсов 1 . Недостатком известного устройства является то, что оно критично к разбросу свойств триггера, не фиксирует одиночных сбоев, происходящих в период между импульсами счета. Наиболее близким по технической сущности к предлагаемому является уст ройство, содержащее триггерный счетчик, D-триггера многовходовые элементы ИЛИ, многовходовый элемент И и кон трольный триггер,причем счетный вход каждого D-триггера, кроме (п+1)-го, соединен с единичным выходом соответствующего разряда счетчика, а счетный вход ()-го О-триггера соединен с нулевым выходом п-го разряда счетчика, входы каждого многовходового элемента ИЛИ соединены с нулевым выходом соответствующего D-триггера и единичными выходами других D-триггеров, выходы многовходовых элементов ИЛИ соединены со Входами многовходового элемента И, один из входов которого соединен со входом импульсов опроса, а выход - со входом установки единичного состояния контрольного триггера 2, Недостатком известного устройства является то, что, обладая таким достоинством как обнаружение произвольного переброса (сбоя) какого-либо триггера счетчика (или нескольких триггеров счетчика) в единичное либо в нулевое состояние в интервале между действием на входе счетных импульсов, оно имеет сравнительно большой объем оборудова97ния, МТС приводит к относительно низкой надежности. Цель изобретения - повышение надежности за счет-упрощения устройства. Поставленная цель достигается тем, что в двоичный сметчик с контролем ошибок, содержащий п-разрядный счетчик на триггерах, счетный вход, контрольный триггер, шину опроса, многовходовый элемент ИЛИ, (n+l) 0-триггеров, счетный вход каждого D-триггера, кроме (п-+-1)-го соединен с единичным выходом соответствующего разряда счетчика на триггерах, счетный вход (n+l)го О-триггера соединен с нулевым выходом п-го разряда счетчика на триггерах , D-входы и входы установки нуля каждого D-триггера подключены соответственно к шине установки единицы и шине установки нуля, вход установки нуля контрольного триггера подключен к шине установки нуля контрольного триг гера, введены п элементов ИЛИ, п элементов И, элемент НЕ, причем входы эле MtjHTOB ИЛИ и И каждого i-ro разряда, кроме первого, объединены и подключены к единичному выходу D-триггера ()-ro разряда и выходу элемента ИЛИ (i-l)-ro разряда, входы элементов ИЛИ и И первого разряда подключены к единичным выходам D-триггеров первого и второго разрядов, вход элемента НЕ соединен с выходом элемента ИЛИ последнего разряда, а выход элемента НЕ соединен с первым входом многовходового элемента ИЛИ, остальные входы которого связаны с выходами элементов И, выход многовходового элемента ИЛИ соединен с О-входом контрольного триггера, счетный вход которого связан с шиной опроса. На фиг. 1 показана схема двоичного счетчика с контролем ошибок; на фиг.2временные диаграммы входных сигналов. Устройство содержит счетчик t на триггерах, D-триггеры 2-6, элементы ИЛИ 7-10, элементы И 11-14, элемент НЕ 15, многовходовый элемент ИЛИ 16 контрольного триггера 17, счетный вход 18, шину 19 установки единицы, шину 20 установки нуля, шину 21 опроса, шину 22 установки нуля контрольного триг гера, выход 23 контрольного триггера. На чертеже также показаны сигнал 2k на шине 21, сигнал-25 на шине 20, сигнал 26 на входе 18. Устройство работает следующим образом. 4 D-триггеры 2-6 переходят в единичное состояние в момент воздействия на счетный вход перепада от уровня логического нуля до уровня логической единицы и устана.вливаются в нулевое состояние при воздействии сигнала установки нуля по шине 20, так как на Dвходы всех триггеров подан сигнал логической единицы. При нормальной работе счетчика при поступлении на вход 18 счетного импульса только один триггер счетчика переходит в единичное состояние (или при переполнении счетчика последний триггер переходит в нулевое состояние). Поэтому при нормальной работе счетчика один и только один Dтриггер переходит в единичное состояние, остальные остаются в нулевом состоянии. На выходах i-ro элемента ИЛИ уровень логической единицы появляется в том случае, если хотя бы один из (п+1) D-триггеров находился а единичном состоянии, на выходах i-ro элемента И 11-1А уровень логической единицы появляется только в том случае, если (|+1)-й Ь-триггер находится в единичном -состоянии и хотя бы один из I предыдущих D-триггеров находится в единичном состоянии, т, е. по крайней мере на одном из выходов элементов И ll-1i появится уровень логической единицы, если хотя бы два D-триггера 26 находятся в единичном состоянии. На выходе многовходового элемента ИЛИ 15 уровень логической единицы появится, если хотя бы на одном из выходов упомянутых элементов И 11-И или элемента НЕ 15 имеется уровень логической единицы, т. е. в случае нарушения нормальной работы счетчика. При этом по импульсу опроса (шина 21) контрольный триггер 17 переходит в единичное состояние, фиксируя сбой. Таким образом, введение в устройство элементов ИЛИ и элементов И, элемента НЕ приводит к сокращению оборудования и межэлементных связей, что повышает его надежность. Формула изобретения Двоичный счетчик с контролем ошибок, содержащий п-разрядный счетчик на триггерах, счетный вход, контрольный триггер, шину опроса, многовходовый элемент ИЛИ, () D-триггеров, счетный вход каждого D-триггера, кроме (п+1)-го, соединен с единичным выходом соответствующего разряда счетчика на триггерах, счетный вход (n+l)го D-триггера соединен с нулевым выходом п-го разряда счетчика на триггерах, D-входы и входы установки нуля каждого О-триггера подключены соответственно к шине установки единицы и шине установки нуля, вход установки нуля контрольного триггера подключен к шине ус11Д-1ЛОП -1 - 11-Г11 I ., -|-,j...-- -Л:ановки нуля контрольного триггера, о т личающийся тем, что, с целью повышения надежности, введены п элементов ИЛИ, п элементов И, элемент НЕ, причем входы элементов ИЛИ и И каждого i-ro разряда, кроме первого, объединены и подключены к единичному выходу О-триггера .(i-l)-ro разряда ивыходу элемента ИЛИ (i-l)-ro разряда, входы элементов ИЛИ и И первого раз974 ряда подключены к единичным выходам D-триггеров первого и второго разрядов, вход элемента НЕ соединен с выходом элемента ИЛИ последнего разряда, а выход элемента НЕ соединен с первым входом многовходового элемента ИЛИ, остальные входы которого соединены с выходами элементов И, выход многовходового элемента ИЛИ соединен с D-входом контрольного триггера, счет ный вход которого соединен с шиной ..«..,л.«..п..- « 1 и п1 | 1е | 1 111ЫЫОЫ опроса. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 363215, кл. И 03 К 21/3, 19712.Авторское свидетельство СССР ff бббб+б, кл. Н 03 К 21/3t, 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик с контролем ошибок | 1983 |

|

SU1121781A2 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Двоичный счетчик с контролем ошибок | 1977 |

|

SU666645A1 |

| Пересчетное устройство | 1982 |

|

SU1115242A1 |

| Устройство для моделирования сетевых графов | 1981 |

|

SU1013965A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Пересчетное устройство с контролем | 1982 |

|

SU1019452A1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

т

5

(J)ui2

Авторы

Даты

1982-10-30—Публикация

1981-04-23—Подача