Изобретение относится к вычислительной технике и может быть использовано для контроля блоков памяти.

Цель изобретения - сокращение времени контроля блоков памяти и получение информации о наличии сбоев и неисправностей, возникающих при решении задачи.

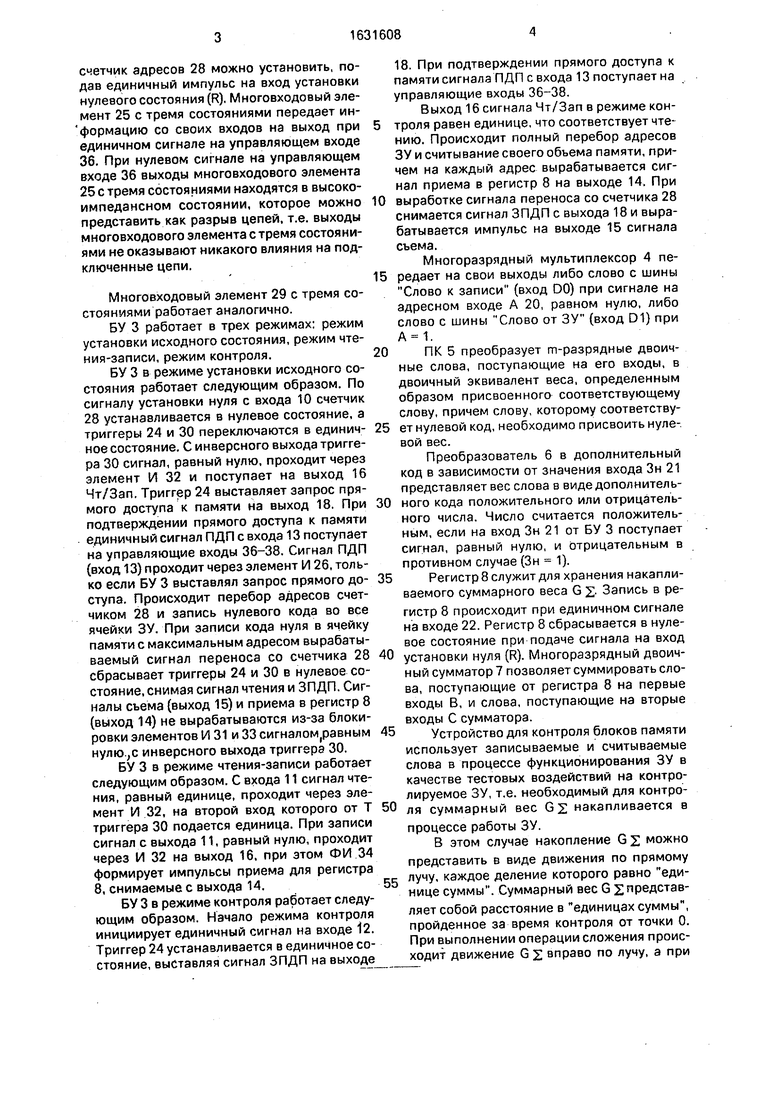

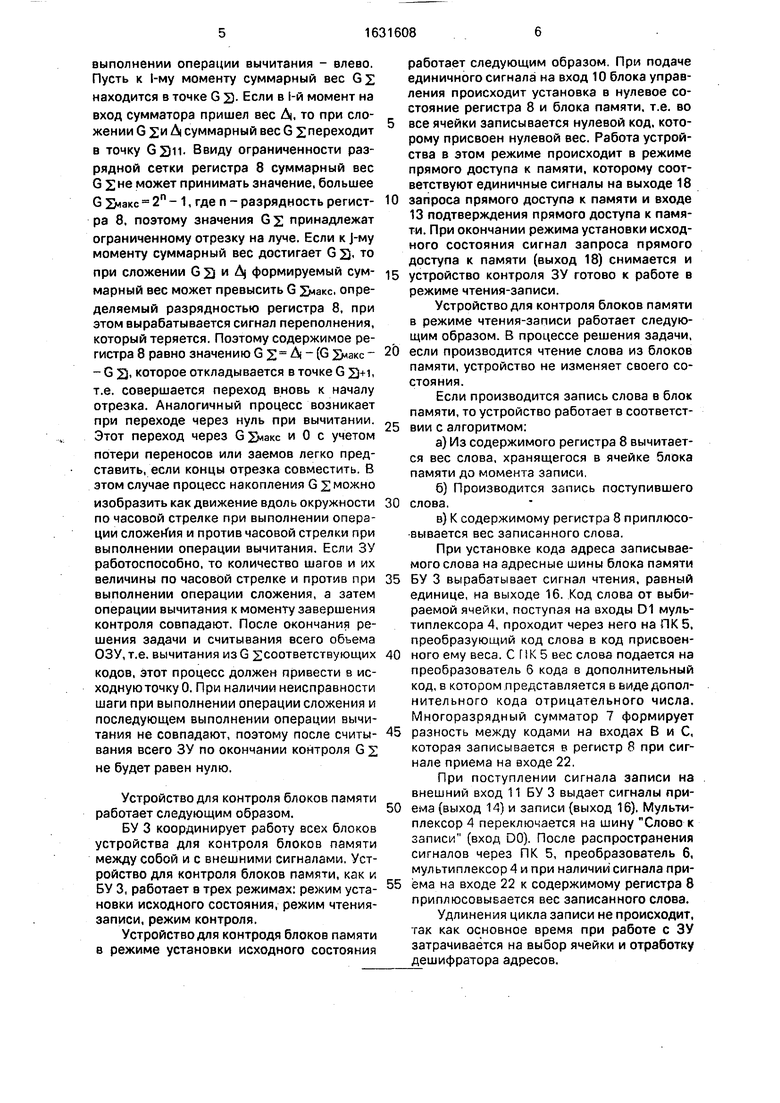

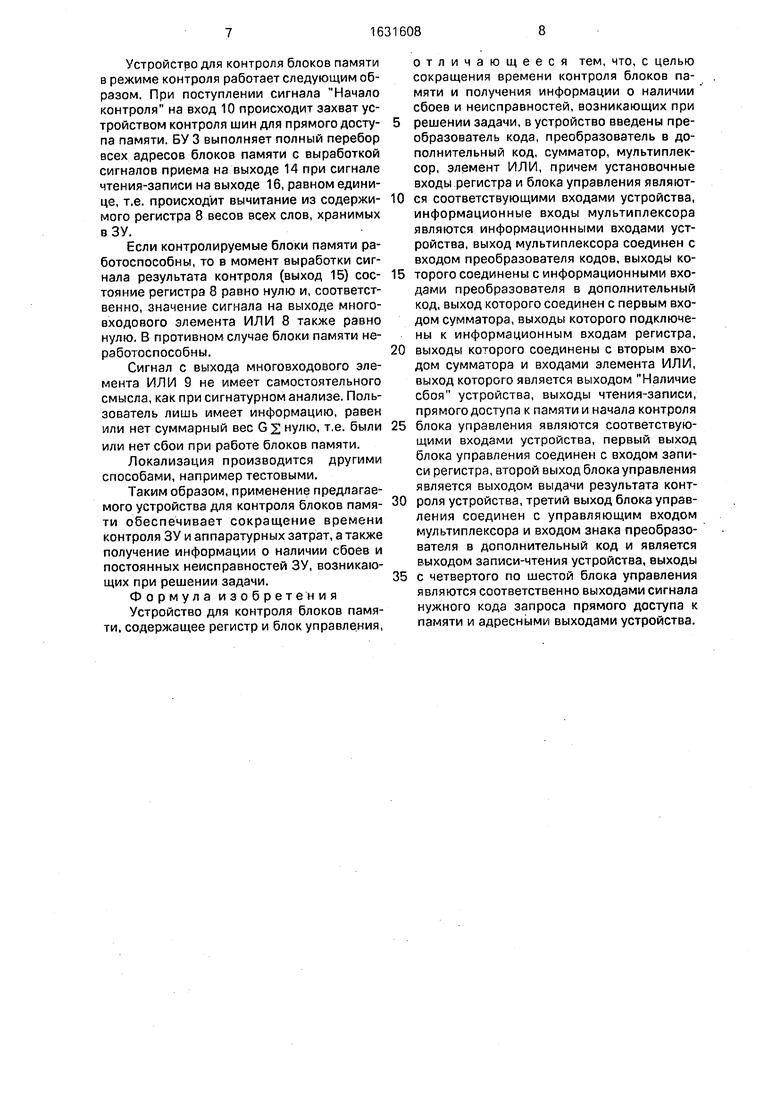

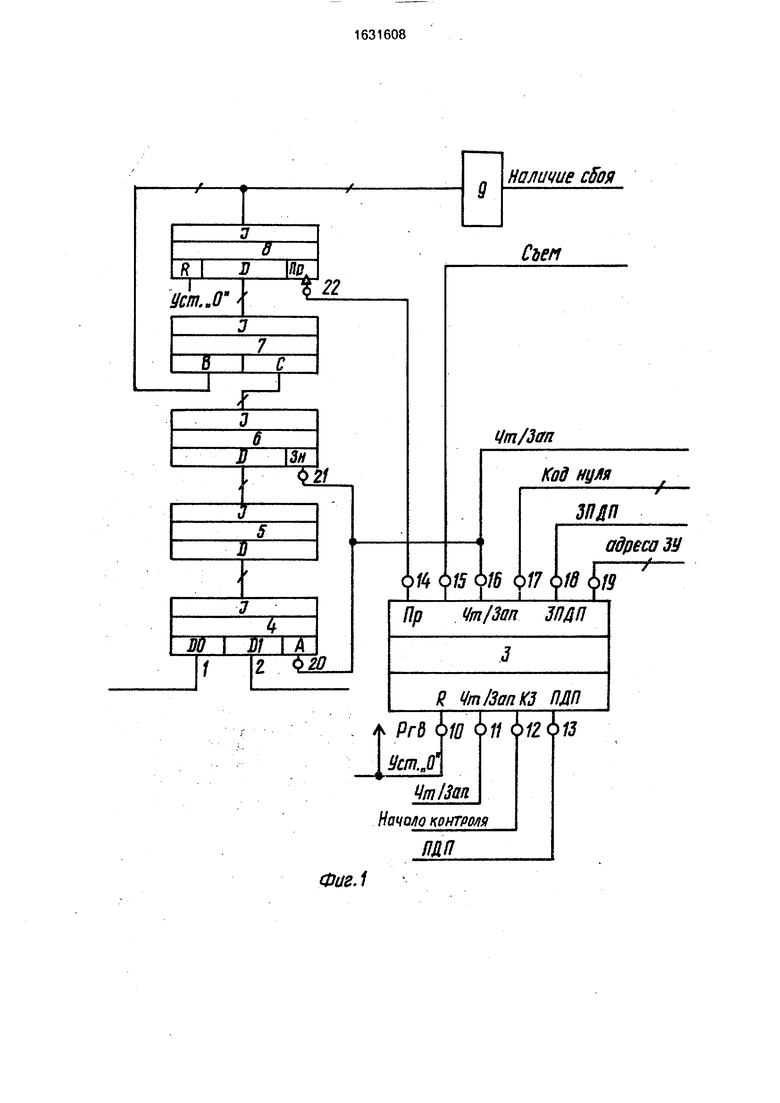

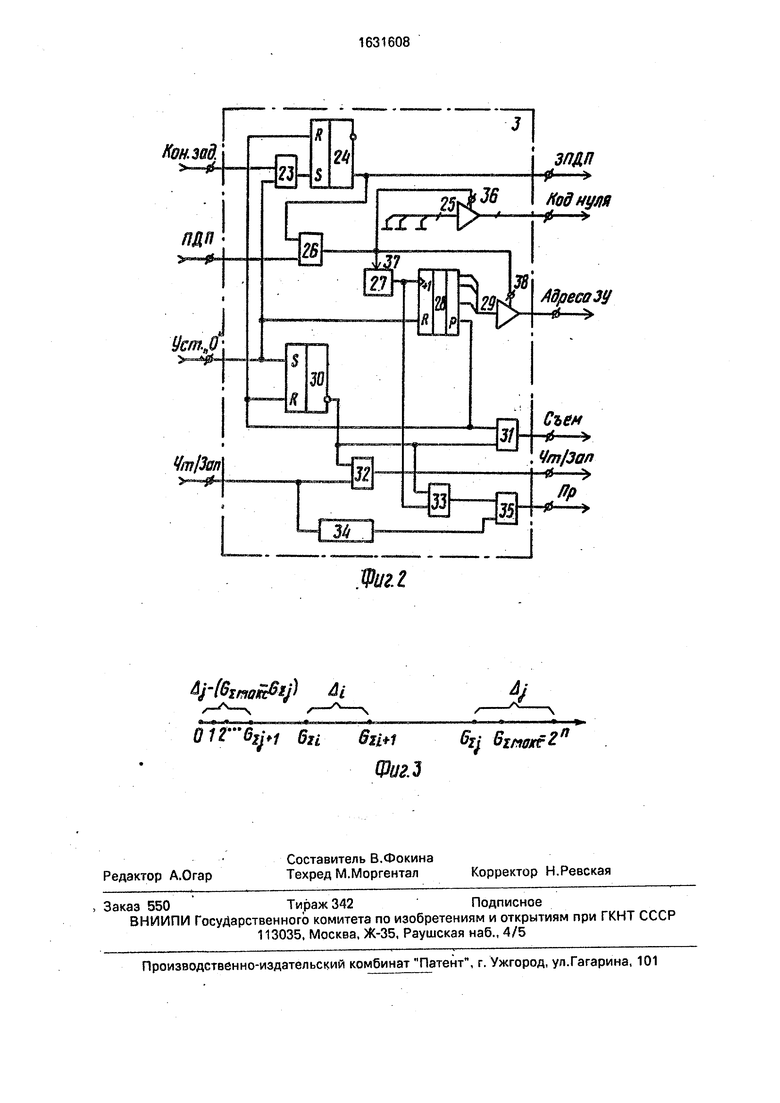

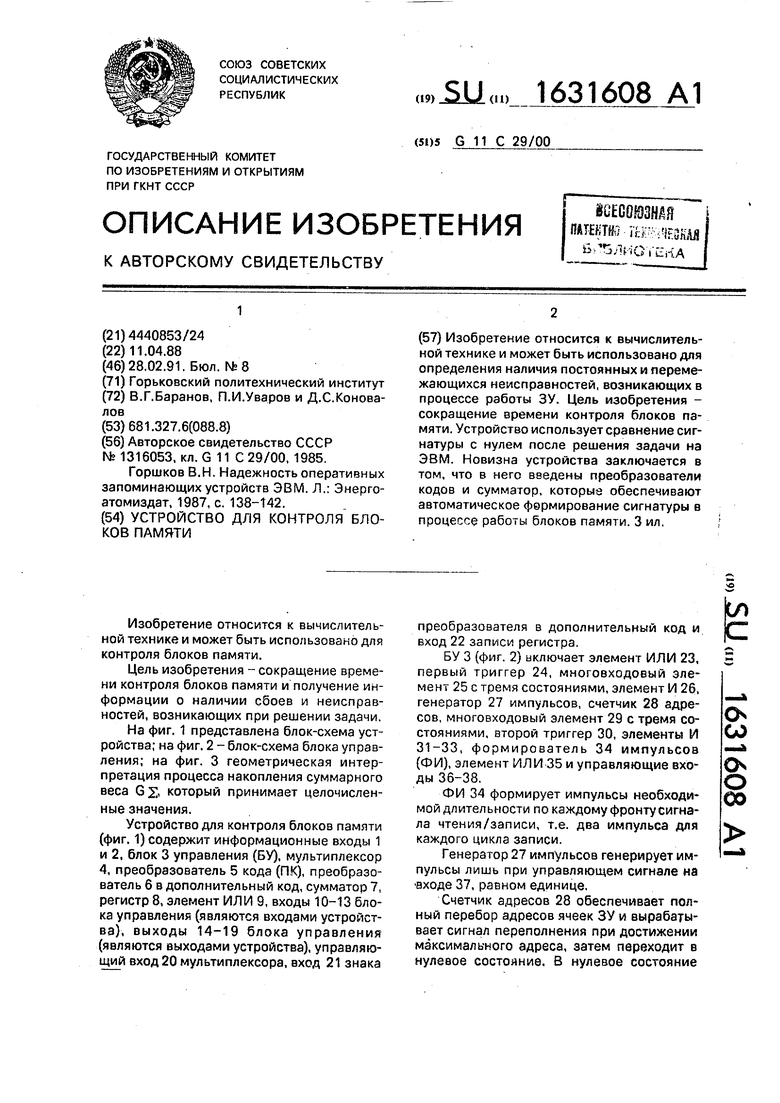

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема блока управления; на фиг. 3 геометрическая интерпретация процесса накопления суммарного веса GX который принимает целочисленные значения.

Устройство для контроля блоков памяти (фиг, 1) содержит информационные входы 1 и 2, блок 3 управления (БУ), мультиплексор 4, преобразователь 5 кода (ПК), преобразователь 6 в дополнительный код, сумматор 7, регистр 8, элемент ИЛИ 9, входы 10-13 блока управления (являются входами устройства), выходы 14-19 блока управления (являются выходами устройства), управляющий вход 20 мультиплексора, вход 21 знака

преобразователя в дополнительный код и вход 22 записи регистра.

БУ 3 (фиг. 2) включает элемент ИЛИ 23, первый триггер 24, многовходоеый элемент 25 с тремя состояниями, элемент И 26, генератор 27 импульсов, счетчик 28 адресов, многовходовый элемент 29 с тремя состояниями, второй триггер 30, элементы И 31-33, формирователь 34 импульсов (ФИ), элемент ИЛИ 35 и управляющие входы 36-38.

ФИ 34 формирует импульсы необходимой длительности по каждому фронту сигнала чтения/записи, т.е. два импульса для каждого цикла записи.

Генератор 27 импульсов генерирует импульсы лишь при управляющем сигнале на входе 37, равном единице,

Счетчик адресов 28 обеспечивает полный перебор адресов ячеек ЗУ и вырабатывает сигнал переполнения при достижении максималиного адреса, затем переходит в нулевое состояние. В нулевое состояние

О

со

Ј о

со

счетчик адресов 28 можно установить, подав единичный импульс на вход установки нулевого состояния (R), Многовходовый элемент 25 с тремя состояниями передает ин- формацию со своих входов на выход при единичном сигнале на управляющем входе 36. При нулевом сигнале на управляющем входе 36 выходы многовходового элемента 25 с тремя состояниями находятся в высоко- импедансном состоянии, которое можно представить как разрыв цепей, т.е. выходы многовходового элемента с тремя состояниями не оказывают никакого влияния на подключенные цепи.

Многовходовый элемент 29 с тремя состояниями работает аналогично.

БУ 3 работает в трех режимах: режим установки исходного состояния, режим чтения-записи, режим контроля.

БУ 3 в режиме установки исходного состояния работает следующим образом. По сигналу установки нуля с входа 10 счетчик 28 устанавливается в нулевое состояние, а триггеры 24 и 30 переключаются в единичное состояние. С инверсного выхода триггера 30 сигнал, равный нулю, проходит через элемент И 32 и поступает на выход 16 Чт/Зап. Триггер 24 выставляет запрос прямого доступа к памяти на выход 18. При подтверждении прямого доступа к памяти единичный сигнал ПДП с входа 13 поступает на управляющие входы 36-38. Сигнал ПДП (вход 13) проходит через элемент И 26, только если БУ 3 выставлял запрос прямого доступа. Происходит перебор адресов счетчиком 28 и запись нулевого кода во все ячейки ЗУ. При записи кода нуля в ячейку памяти с максимальным адресом вырабатываемый сигнал переноса со счетчика 28 сбрасывает триггеры 24 и 30 в нулевое состояние, снимая сигнал чтения и ЗПДП. Сигналы съема (выход 15) и приема в регистр 8 (выход 14) не вырабатываются из-за блокировки элементов И 31 и 33 сигналом(равным нулю.;с инверсного выхода триггера 30.

БУ 3 в режиме чтения-записи работает следующим образом. С входа 11 сигнал чтения, равный единице, проходит через элемент И 32, на второй вход которого от Т триггера 30 подается единица. При записи сигнал с выхода 11, равный нулю, проходит через И 32 на выход 16, при этом ФИ 34 формирует импульсы приема для регистра 8, снимаемые с выхода 14.

БУ 3 в режиме контроля работает следующим образом. Начало режима контроля инициирует единичный сигнал на входе 12. Триггер 24 устанавливается в единичное состояние, выставляя сигнал ЗПДП на выходе

18. При подтверждении прямого доступа к памяти сигнала ПДП с входа 13 поступает на управляющие входы 36-38.

Выход 16 сигнала Чт/Зап в режиме контроля равен единице, что соответствует чтению. Происходит полный перебор адресов ЗУ и считывание своего объема памяти, причем на каждый адрес вырабатывается сигнал приема в регистр 8 на выходе 14. При

выработке сигнала переноса со счетчика 28 снимается сигнал ЗПДП с выхода 18 и вырабатывается импульс на выходе 15 сигнала съема.

Многоразрядный мультиплексор 4 передает на свои выходы либо слово с шины Слово к записи (вход DO) при сигнале на адресном входе А 20, равном нулю, либо слово с шины Слово от ЗУ (вход D1) при А 1.

ПК 5 преобразует m-разрядные двоичные слова, поступающие на его входы, в двоичный эквивалент веса, определенным образом присвоенного соответствующему слову, причем слову, которому соответствует нулевой код, необходимо присвоить нулевой вес.

Преобразователь 6 в дополнительный код в зависимости от значения входа Зн 21 представляет вес слова в видедополнительного кода положительного или отрицательного числа. Число считается положительным, если на вход Зн 21 от БУ 3 поступает сигнал, равный нулю, и отрицательным в противном случае (Зн 1).

Регистр 8 служит для хранения накапливаемого суммарного веса G Ј. Запись в регистр 8 происходит при единичном сигнале на входе 22. Регистр 8 сбрасывается в нулевое состояние при подаче сигнала на вход

установки нуля (R). Многоразрядный двоичный сумматор 7 позволяет суммировать слова, поступающие от регистра 8 на первые входы В, и слова, поступающие на вторые входы С сумматора.

Устройство для контроля блоков памяти использует записываемые и считываемые слова в процессе функционирования ЗУ в качестве тестовых воздействий на контролируемое ЗУ, т.е. необходимый для контроля суммарный вес G2 накапливается в процессе работы ЗУ.

В этом случае накопление GЈ можно представить в виде движения по прямому

ЛУЧУ- каждое деление которого равно единице суммы. Суммарный вес G 2представляет собой расстояние в единицах суммы, пройденное за время контроля от точки 0. При выполнении операции сложения происходит движение G Ј вправо по лучу, а при

выполнении операции вычитания - влево. Пусть к 1-му моменту суммарный вес G2 находится в точке G 2- Если в 1-й момент на вход сумматора пришел вес Д, то при сложении G 2й А суммарный вес G 2 переходит в точку G211- Ввиду ограниченности разрядной сетки регистра 8 суммарный вес G Ј не может принимать значение, большее G 2иакс 2n - 1, где n - разрядность регистра 8, поэтому значения G 2 принадлежат ограниченному отрезку на луче. Если к j-му моменту суммарный вес достигает G 2- то при сложении G2 и Д( формируемый суммарный вес может превысить G , определяемый разрядностью регистра 8, при этом вырабатывается сигнал переполнения, который теряется. Поэтому содержимое регистра 8 равно значению G 2 А - (G - - G 2- которое откладывается в точке G 3+1. т.е. совершается переход вновь к началу отрезка. Аналогичный процесс возникает при переходе через нуль при вычитании. Этот переход через G и 0 с учетом потери переносов или заемов легко представить, если концы отрезка совместить. В этом случае процесс накопления G 2 можно изобразить как движение вдоль окружности по часовой стрелке при выполнении операции сложей ия и против часовой стрелки при выполнении операции вычитания. Если ЗУ работоспособно, то количество шагов и их величины по часовой стрелке и против при выполнении операции сложения, а затем операции вычитания к моменту завершения контроля совпадают. После окончания решения задачи и считывания всего объема ОЗУ, т.е. вычитания из G 2соответствующих

кодов, этот процесс должен привести в исходную точку 0. При наличии неисправности шаги при выполнении операции сложения и последующем выполнении операции вычитания не совпадают, поэтому после считывания всего ЗУ по окончании контроля G 2 не будет равен нулю.

Устройство для контроля блоков памяти работает следующим образом.

БУ 3 координирует работу всех блоков устройства для контроля блоков памяти между собой и с внешними сигналами, Устройство для контроля блоков памяти, как и БУ 3, работает в трех режимах: режим установки исходного состояния, режим чтения- записи, режим контроля.

Устройство для контродя блоков памяти в режиме установки исходного состояния

работает следующим образом. При подаче единичного сигнала на вход 10 блока управления происходит установка в нулевое состояние регистра 8 и блока памяти, т.е. во

все ячейки записывается нулевой код, которому присвоен нулевой вес. Работа устройства в этом режиме происходит в режиме прямого доступа к памяти, которому соответствуют единичные сигналы на выходе 18

0 запроса прямого доступа к памяти и входе 13 подтверждения прямого доступа к памяти. При окончании режима установки исходного состояния сигнал запроса прямого доступа к памяти (выход 18) снимается и

5 устройство контроля ЗУ готово к работе в режиме чтения-записи.

Устройство для контроля блоков памяти в режиме чтения-записи работает следующим образом. В процессе решения задачи,

0 если производится чтение слова из блоков памяти, устройство не изменяет своего состояния.

Если производится запись слова в блок памяти, то устройство работает в соответст5 вии с алгоритмом:

а)Из содержимого регистра 8 вычитается вес слова, хранящегося в ячейке блока памяти до момента записи.

б)Производится запись поступившего 0 слова.

в)К содержимому регистра 8 приплюсовывается вес записанного слова.

При установке кода адреса записываемого слова на адресные шины блока памяти

5 БУ 3 вырабатывает сигнал чтения, равный единице, на выходе 16. Код слова от выбираемой ячейки, поступая на входы D1 мультиплексора 4, проходит через него на ПК 5, преобразующий код слова в код присвоен0 ного ему веса. С ПК 5 вес слова подается на преобразователь 6 кода в дополнительный код, в котором представляется в виде дополнительного кода отрицательного числа. Многоразрядный сумматор 7 формирует

5 разность между кодами на входах В и С, которая записывается в регистр 8 при сигнале приема на входе 22.

При поступлении сигнала записи на внешний вход 11 БУ 3 выдает сигналы при0 ема (выход 14) и записи (выход 16). Мультиплексор 4 переключается на шину Слово к записи (вход DO). После распространения сигналов через ПК 5, преобразователь 6, мультиплексор 4 и при наличии сигнала при5 ема на входе 22 к содержимому регистра 8 приплюсовывается вес записанного слова. Удлинения цикла записи не происходит, так как основное время при работе с ЗУ затрачивается на выбор ячейки и отработку дешифратора адресов.

Устройство для контроля блоков памяти в режиме контроля работает следующим образом. При поступлении сигнала Начало контроля на вход 10 происходит захват устройством контроля шин для прямого доступа памяти. БУ 3 выполняет полный перебор всех адресов блоков памяти с выработкой сигналов приема на выходе 14 при сигнале чтения-записи на выходе 16, равном единице, т.е. происходит вычитание из содержимого регистра 8 весов всех слов, хранимых в ЗУ.

Если контролируемые блоки памяти работоспособны, то в момент выработки сигнала результата контроля (выход 15) состояние регистра 8 равно нулю и, соответственно, значение сигнала на выходе много- входового элемента ИЛИ 8 также равно нулю. В противном случае блоки памяти неработоспособны.

Сигнал с выхода многовходового элемента ИЛИ 9 не имеет самостоятельного смысла, как при сигнатурном анализе. Пользователь лишь имеет информацию, равен или нет суммарный вес G 2 нулю, т.е. были или нет сбои при работе блоков памяти.

Локализация производится другими способами, например тестовыми.

Таким образом, применение предлагаемого устройства для контроля блоков памяти обеспечивает сокращение времени контроля ЗУ и аппаратурных затрат, а также получение информации о наличии сбоев и постоянных неисправностей ЗУ, возникающих при решении задачи.

Формула изобретения

Устройство для контроля блоков памяти, содержащее регистр и блок управления,

отличающееся тем, что, с целью сокращения времени контроля блоков памяти и получения информации о наличии сбоев и неисправностей, возникающих при

решении задачи, в устройство введены преобразователь кода, преобразователь в дополнительный код, сумматор, мультиплексор, элемент ИЛИ, причем установочные входы регистра и блока управления являются соответствующими входами устройства, информационные входы мультиплексора являются информационными входами устройства, выход мультиплексора соединен с входом преобразователя кодов, выходы которого соединены с информационными входами преобразователя в дополнительный код, выход которого соединен с первым входом сумматора, выходы которого подключены к информационным входам регистра,

выходы которого соединены с вторым входом сумматора и входами элемента ИЛИ, выход которого является выходом Наличие сбоя устройства, выходы чтения-записи, прямого доступа к памяти и начала контроля

блока управления являются соответствующими входами устройства, первый выход блока управления соединен с входом записи регистра, второй выход блока управления является выходом выдачи результата контроля устройства, третий выход блока управления соединен с управляющим входом мультиплексора и входом знака преобразователя в дополнительный код и является выходом записи-чтения устройства, выходы

с четвертого по шестой блока управления являются соответственно выходами сигнала нужного кода запроса прямого доступа к памяти и адресными выходами устройства.

б

Цт/Зап

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1010660A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Запоминающее устройство с тестовым самоконтролем | 1986 |

|

SU1396160A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1594610A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

Изобретение относится к вычислительной технике и может быть использовано для определения наличия постоянных и перемежающихся неисправностей, возникающих в процессе работы ЗУ. Цель изобретения - сокращение времени контроля блоков памяти. Устройство использует сравнение сигнатуры с нулем после решения задачи на ЭВМ. Новизна устройства заключается в том, что в него введены преобразователи кодов и сумматор, которыз обеспечивают автоматическое фермирование сигнатуры в процессе работы блоков памяти. 3 ил.

В 3н

I

02/

В

БО I Д/ I A

/

2 5Ж

Фиг.1

Код нуля

w&n

адреса ЗУ

6/4 0/5 0/5 ф/7 })tf (j)/ Я/7 (fa/ftw

Чт/ЗапКЗ ПДП РгВ blO btibК # Smjf-.

Чт/Зап

Начало КОНТРОЛЯ fluff

&Г$1пак$$ &i

oir-вуц вп бц

ФигЗ

.Ш1

| Устройство для контроля блоков памяти | 1985 |

|

SU1316053A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Горшков В.Н | |||

| Надежность оперативных запоминающих устройств ЭВМ | |||

| Л.: Энерго- атомиздат, 1987, с, 138-142 | |||

Авторы

Даты

1991-02-28—Публикация

1988-04-11—Подача