1

Изобретение относится к области вычислительной техники и предназначено для распределения управляющих сигналов последовательно по т выходным шинам.

Известен датчик тактов, содержащий .V-разрядпый регистр, каждый разряд которого состоит ИЗ двух триггеров. Единичные входы первых триггеров каждого разряда соединены с пулевыми выходами вторых триггеров того же разряда, а единичные выходы - с входом тактовой частоты устройства.

Известпые устройства обладают недостаточно широкими возможностями, что затрудняет формирование управляюш,их сигналов.

Целью изобретения является расширение класса решаемых задач, т. е. увеличение числа разновидностей выходных сигналов.

С этой целью в .каждый разряд регистра введена схема «И-НЕ, первый вход которой соединен с нулевым входом первого триггера данного разряда и единичным входом первого триггера соседнего младшего разряда, а второй вход подключен к единичному выходу первого триггера данного разряда. Выход этой схемы соедипен с нулевым .входом второго триггера соседнего старшего разряда.

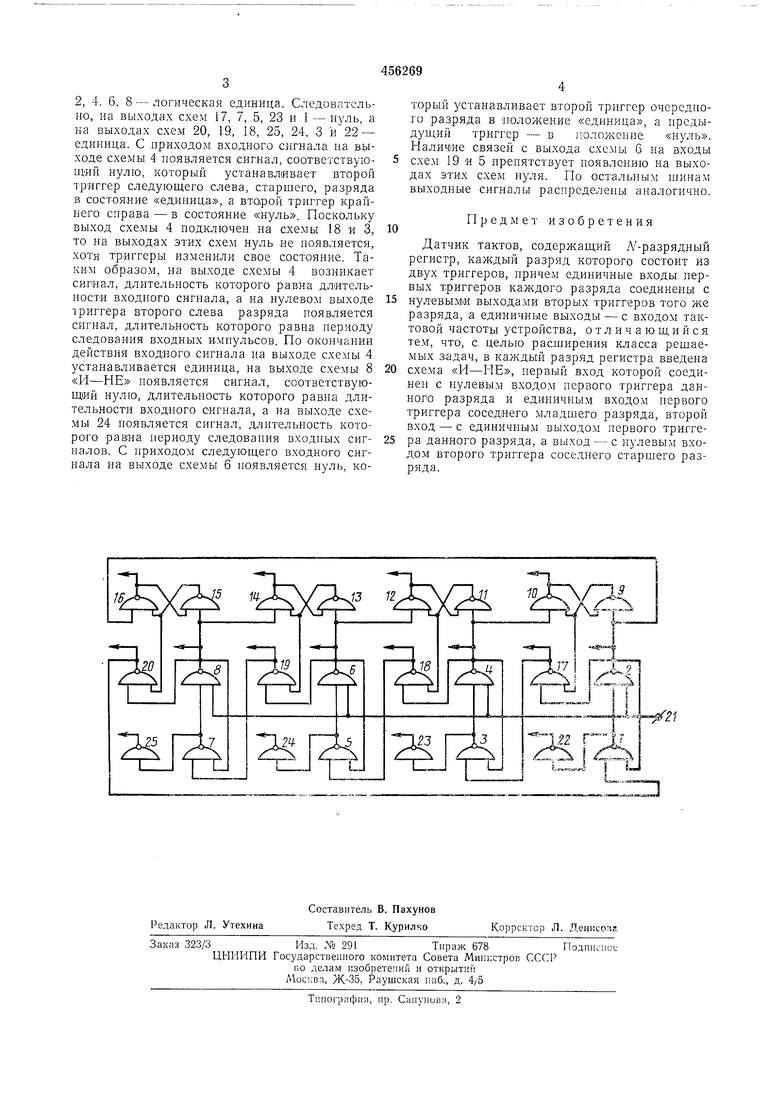

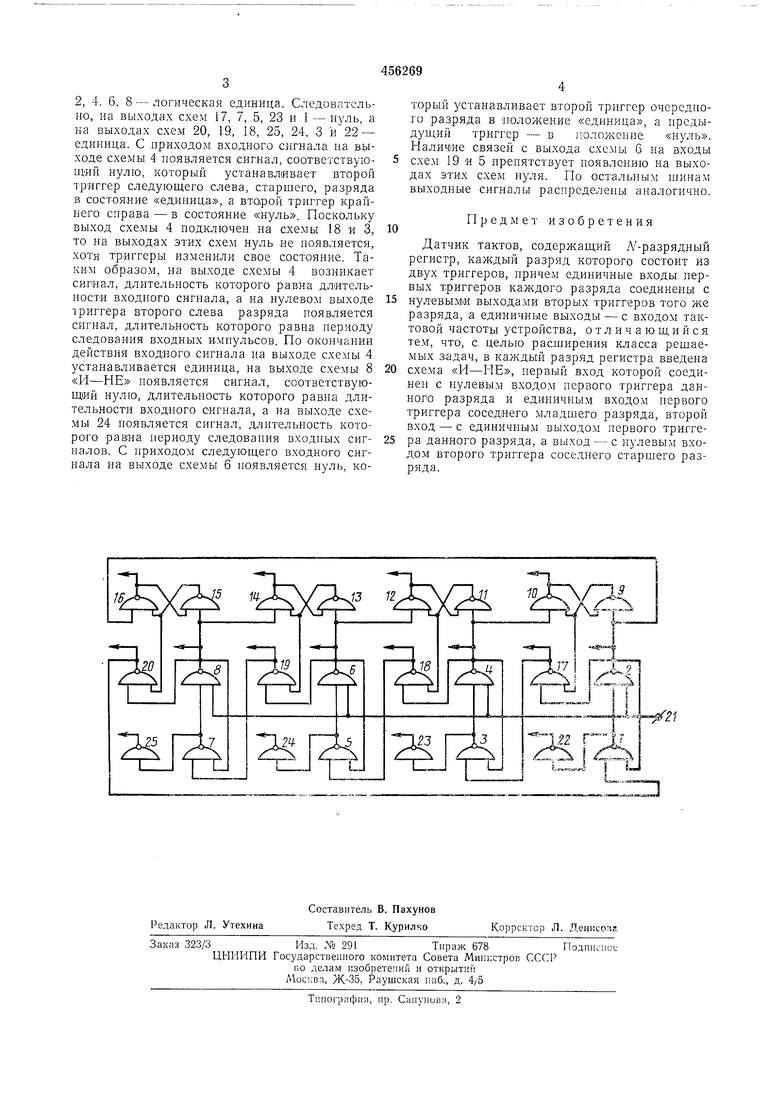

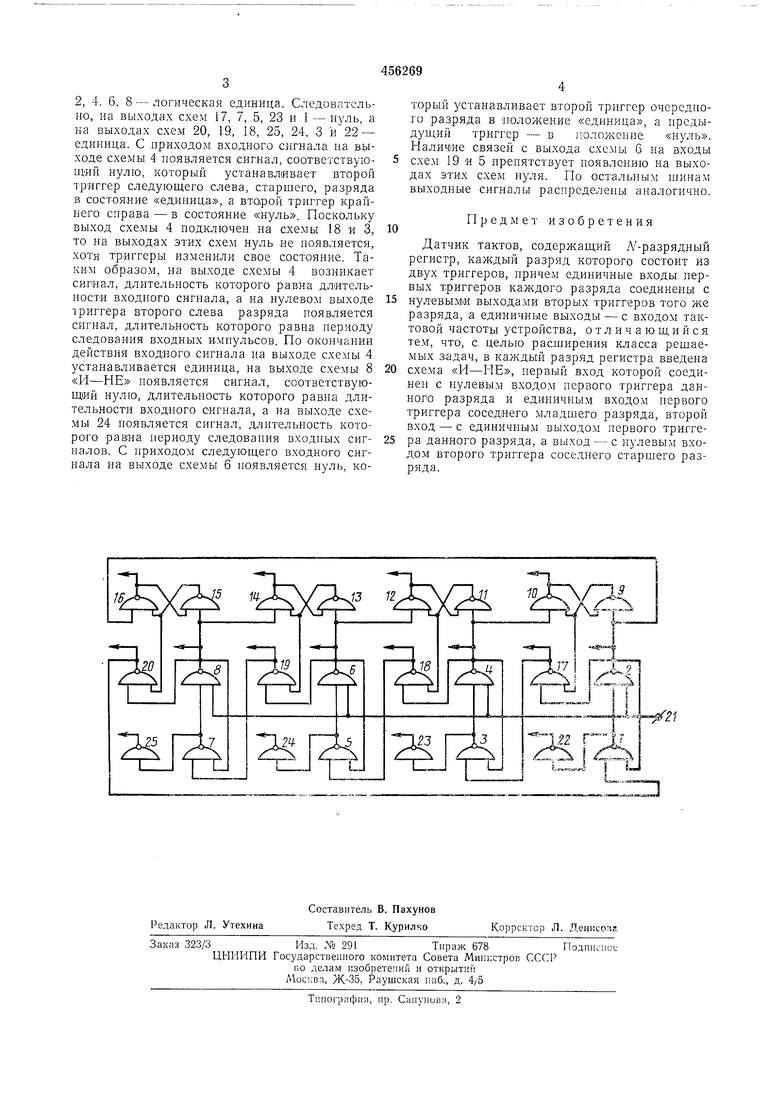

На чертеже нредставлсна схема датчика тактов для числа разрядов .

Устройство содержит регистр, каждый разряд которого включает два триггера.

Нервые триггеры всех разрядов состояв пз схем «НЕ 1-8, а вторые триггеры - из схем чИ-НЕ 9-16.

Нулевые выходы первых триггеров (выходы схем 2-8) соединены с единичным входами вторых триггеров (входами схем 9-15), с пулевыми входами соседних младших вторых триггеров (входами схем 10-16) и с дополнительными схемами «И-НЕ 17-20, другой

вход которых подключен к единичным выходам первых триггеров (выходам схем 9-15). Выходы схем 17-20 соединены с нулевыми входами второго триггера соседнего старшего разряда (входами схем 1-7). Единичные входы первых триггеров (входы схем 2-8) соединены со входом 21 тактовой частоты.

С.хемы «И-НЕ 22-25 служат для инверсии выходных сигналов. Устройство работает следуюш,им образом.

В начальный момент времени второй триггер одного из разрядов устанавливается в положение «единица (например, крайний справа- младший). Осальные триггеры находятся в состоянии «нуль. В этом случае на выходе схем «И-НЕ 9, 12, 14 -и 16 - логическая единица, на выходе схем «И-НЕ 10, И, 13, 15 - логический нуль.

Пусть в начальный момент времени входной сигнал тактовой частоты отсутствует, т. е. равен логическому нулю, тогда на выходе схем

2, 4, 6, 8 - логическая единица. Следовательно, на выходах схем 17, 7, 5, 23 и I - нуль, а на выходах схем 20, 19, 18, 25, 24, 3 и 22- единица. С приходом входного сигнала на выходе схемы 4 ноявляется сигнал, соответствуюнщй нулю, который устанавливает второй триггер следующего слева, старшего, разряда в состояние «единица, а второй триггер крайнего снрава - в состояние «нуль. Поскольку выход схемы 4 подключен на схемы 18 и 3, то на выходах этих схем нуль не ноявляется, хотя триггеры изменили свое состояние. Таким образом, на выходе схемы 4 возникает сигнал, длительность которого равна длительности входного сигнала, а на нулевом выходе триггера второго слева разряда ноявляется сигнал, длительность которого равна периоду следования входных имнульсов. По окончании действия входного сигнала на выходе схемы 4 устанавливается единица, на выходе схемы 8 «И-ПЕ появляется сигнал, соответствуюНЦ1ИЙ нулю, длительность которого равна длительности входного сигнала, а на выходе схемы 24 ноявляется сигнал, длительность которого равна периоду следования входных сигналов. С приходом следующего входного сигнала на выходе схемы 6 ноявляется нуль, который устанавливает второй триггер очередного разряда в положение «единица, а предыдущий триггер - в 5оложение «нуль. Налич-ие связей с выхода схемы 6 на входы схе.м 19 и 5 препятствует ноявлению на выходах этих схем нуля. По остальным пшнам выходные сигналы распределены аналогично.

Предмет изобретения

Датчик тактов, содержащий Л-разрядный регистр, каждый разряд которого состоит из двух триггеров, причем единичные входы первых триггеров каждого разряда соединены с нулевымй выходами вторых триггеров того же разряда, а единичные выходы - с входом тактовой частоты устройства, отличающийся тем, что, с целью расширения класса решаемых задач, в каждый разряд регистра введена схема «И-ПЕ, первый вход которой соединен с нулевым входом первого триггера данного разряда и единичным входом первого триггера соседнего младшего разряда, второй вход - с едииичным выходом первого триггера данного разряда, а выход - с нулевым входом второго триггера соседнего старшего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения первого и последнего импульсов в пачке | 1989 |

|

SU1672560A2 |

| Датчик тактов | 1976 |

|

SU615470A2 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Устройство для коррекции сбойных кодов в кольцевом распределителе | 1979 |

|

SU888125A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| Формирователь синхроимпульсов биимпульсного кода | 1983 |

|

SU1128373A1 |

| Устройство для коррекции погрешности аналого-цифровых преобразователей | 1986 |

|

SU1341717A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1974 |

|

SU494744A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

L,

Авторы

Даты

1975-01-05—Публикация

1973-01-11—Подача