сд со

СО

Изобретение относится к радиотехнике, может быть использовано в устройствах автоподстройки частоты.

Целью изобретения является повышение быстродействия.

На чертеже представлена структурная электрическая схема устройства. Устройство содержит делитель 1 с переменным коэффициентом деления, кодозадающий блок 2, частотньй детектор (ЧД) 3, опбрный генератор (ОГ) 4, итерационный вычислительный блок

Й(ИВБ) 5, преобразователь 6 код - напряжение, перестраиваемый генератор 7, смеситель 8, умножитель 9 частоты,

I ключ 10, счетчик 11, блок 12 сравне- ния кодов, регистр 13 последователь-

1ных приближений, формирователь 14 импульсов s первый триггер 15, элемент И 16, дополнительный счетчик 17, дешифратор 18, элемент ИЛИ 19, второй триггер 20, удвоитель 21 частоты, коммутатор 22, реверсивный счетчик 23, блок сдвига кода (БСК) 24, дополнительный триггер 25, дополнительный элемент ИЛИ 26..

Устройство работает следующим образом.

Величина управляющего напряжения на выходе преобразователя 6 код - напряжение может принимать п фиксированных значений. Число п обычно выбирается исходя из требуемой точности подстройки перестраиваемого генератора 7 следующим образом:

п int(f

макс J +

где f

макс

иЈ

МНИ

int...

-соответственно мак- симальная и минимальная частота перестраиваемого генератора 7;

-означает операцию взятия целой части числа, заключенного в скобки.

В соответствии с выбранным значением п число двоичных разрядов реверсивного счетчика 23 и входящего в итерационный вычислительный блок 5 регистра 13 выбирается равным

я

int + 1 .

В статическом режиме после окончания подстройки частота сигнала на выходе перестраиваемого равна

генератор 7

вы.

f0N + pfe ± f

С Ш

5

0

5

0

5

0

5

0

5

где f с

N

оы

частота ОГ 4;

коэффициент деления делителя 1, величина которого устанавливается кодозадающим блоком 2;

коэффициент умножения умножителя 9;

величина абсолютной погрешности частоты., не превышающая требуемой точности подстройки и f ,

На частотный детектор 3 поступают сигналы, частоты которых отличаются друг от друга на величину f0bl/N. Это значение разницы частот не превышает величины зоны нечувствительности ЧД 3, которая выбирается равной f/Ы 0 с В этом случае на выходе ЧД 3 имеется постоянный уровень напряжения, в регистре 13 и реверсивном счетчике 23 сохраняется код, соответствующий требуемой рабочей частоте, триггеры 25 и 20 находятся в состоянии, при котором сигналы с выходов коммутатора 22 и смесителя 8 не проходят соответственно через элемент И 16 и ключ 10 на входы счетчиков 17 и II соответственно. Триггер 15 находится в нулевом состоянии, в результате чего на выход коммутатора 22 проходит сигнал с выхода ОГ 4 частотой Ј0 , а БСК 24 передает входной код на выход без сдвига. При смене кода частоты в кодозада- ющем блоке 2 изменяется коэффициент деления делителя 1, и частотная ошибка между сравниваемыми сигналами ЧД 3 превышает величину его зоны нечувствительности. В результате на выходе ЧД 3 формируется сигнал, который поступает на вход ИВБ 5, следствием чего является появление импульса на выходе формирователя 14, л начинается процесс подстройки.

Подстройка частоты осуществляется в два этапа. На первом этапе система автоподстройки работает в режиме смещения границ исследуемого диапазона частот за счет последовательного половинного деления диапазона перестройки во время каждого цикла. При этом производится поразрядное изменение выходного кода ИВБ 5 и его коррекция на основе сигнала частотного

рассогласования, формируемого блоком 12. Реверсивный счетчик 23 работает на этом этапе как буферный регистр. На первом этапе подстройка осуществляется за k циклов, каждый из которых состоит из 1 тактов измерения и двух дополнительных тактов. Максимальное число циклов kMOKC определяется количеством разрядов .регистра 13

кость которого выбирается равной h - 1 + 2.

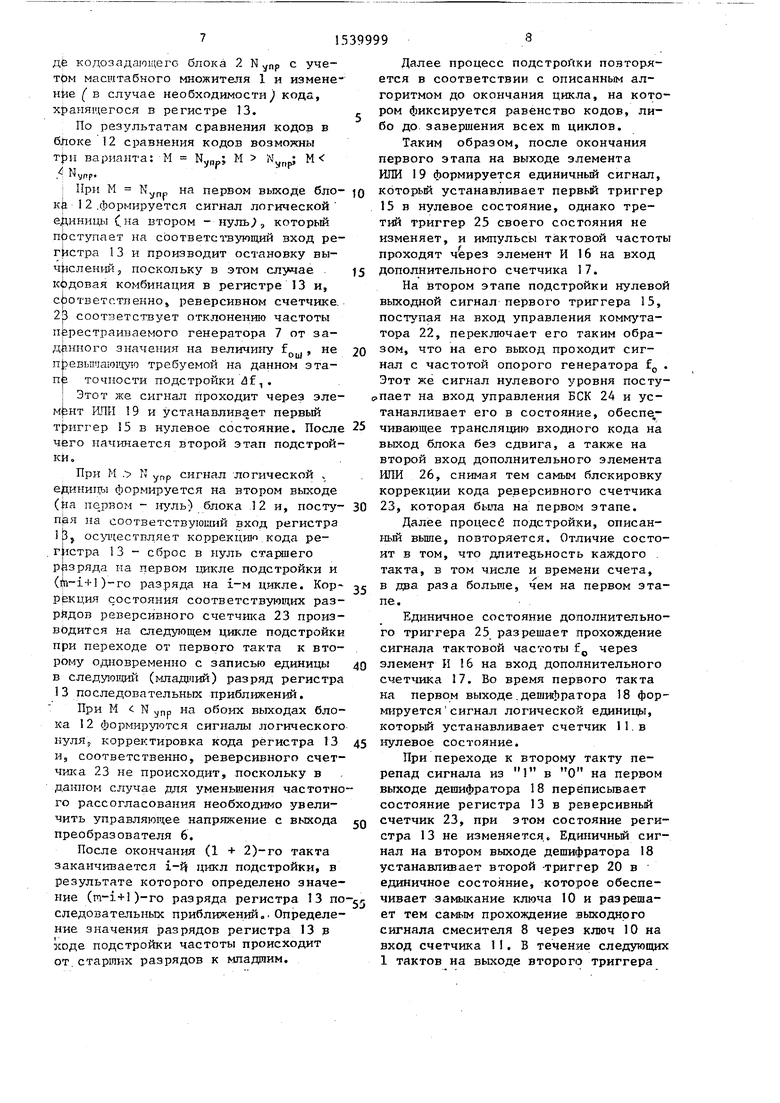

Дешифратор 8 осуществляет преобразование кода дополнительного счетчика 17 в трехразрядный позиционный код на своих выходах в соответствии с таблицей истинности

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической подстройки частоты | 1985 |

|

SU1298915A1 |

| Частотный компаратор | 1981 |

|

SU1023630A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Частотный компаратор | 1983 |

|

SU1167719A2 |

| Число-импульсное устройство для решения задач автоматического дозирования | 1983 |

|

SU1098000A1 |

| Устройство для индикации | 1978 |

|

SU734755A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия. Устройство автоматической подстройки частоты содержит делитель 1 с переменным коэф.деления, кодозадающий блок 2, частотный детектор 3, опорный г-р 4, интерационный вычислительный блок 5, преобразователь 6 код-напряжение, перестраиваемый г-р 7, смеситель 8, умножитель 9 частоты, ключ 10, счетчики 11 и 17, блок сравнения 12 кодов, регистр 13 последовательных приближений, формирователь 14 импульсов, триггеры 15, 20 и 25, эл-т И 16, дешифратор 18, эл-ты ИЛИ 19 и 26, удвоитель 21 частоты, коммутатор 22, реверсивный счетчик 23 и блок сдвига 24 кода. Цель достигается путем обеспечения работы с удвоенной тактовой частотой. 1 ил.

макс

m int С log 2n 1 + 1

Число тактов измерения в каждом цикле зависит от требуемой точности подстройки иf т 24f и частоты, поступающей на тактовый вход ИВБ 5

1 int С 2 fc tut i + 1 int f0/df J + 1.

На втором этапе подстройки, состоящем из одного цикла, производится измерение частотного рассогласования с удвоенной точностью (df) для значе- ния кода управления, записанного в реверсивном счетчике 23 после окончания первого этапа, и коррекция этого значения на плюс-минус единицу младшего разряда при необходимости в соот ветствии с алгоритмом описанным ниже. Таким образом, подстройка частоты в предложенном устройстве производится за (те+1) циклов.

Первый цикл подстройки начинается после появления импульса на выходе формирователя 14 импульсов, который устанавливает первый триггер 15 и дополнительный триггер 25 в единичное состояние, а дополнительный счетчик 17 и регистр 13 в нулевое состояние. Единичный выходной сигнал первого триггера 15 переключает коммутатор 22 в состояние, когда на его выход проходит сигнал 2 Ј0 с выхода опорного нератора 4 через удвоитель 21, этот сигнал переключает БСК 24 в состояние, обеспечивающее сдвиг кода частотного рассогласования с выхода счетчика 11 влево на один разряд, т.е. умножение на два, и через дополнительный элемент ИЛИ 26 переводит реверсивный счетчик 23 в режим работы буферного регистра, запрещая работу в режиме счета. Единичный сигнал на выходе третьего триггера 25 разрешает прохождение импульсов удвоенной тактовой частоты 2 Ј0 через элемент И 16 на вход дополнительного счетчика 17, ем

15

20

35

25 зо

40 45

0

5

Во время первого такта на парном выходе дешифратора 18 формируется сигнал логической единицы, который производит установку счетчика 11 в нулевое состояние.

При переходе к второму такту по перепаду сигнала из единицы в нуль на первом выходе дешифратора 18 производится запись единицы в m-й (старший) разр яд регистра 13 на первом ,цикле, а на i-м цикле подстройки в (m-i+1)-й разряд. Этот же сигнал производит перезапись кода регистра 13 в реверсивный счетчик 23, и этот код после преобразования в преобразователе 6 в управляющее напряжение определяет частоту выходного сигнала перестраиваемого генератора 7.

Во время второго такта единичный сигнал на втором выходе дешифратора 18 устанавливает второй триггер 20 в единичное состояние, которое обеспечивает замыкание ключа 10 и разрешает тем самым прохождение выходного сигнала смесителя 8 на вход счетчика 11.

В течение последующих 1 тактов на выходе второго триггера 20 сохраняется сигнал единичного уровня и производится измерение частоты выходного (Сигнала смесителя 8 путем заполнения счетчика 11.

Во время (1 + 2)-го такта единичный сигнал на третьем выходе дешифратора 18 устанавливает второй триггер 20 в нулевое состояние, размыкая тем самым ключ 10 и прекращая заполнение счетчика 11. За время этого такта производится сравнение кода, накопленного счетчиком 11 к моменту окончания счета М N1, с кодом на выходё кодозадающего блока 2 N vnp с уче- тфм масштабного множителя 1 и изменение ( в случае необходимости кода, хранящегося в регистре 13.

По результатам сравнения кодов в блоке 12 сравнения кодов возможны

три варианта: М Ny)lp; M

W м

NUBP.

При М МуП„ на первом выходе блока 12 формируется сигнал логической единицы С на втором - пуль),, который поступает на соответствующий вход регистра 13 и производит остановку вычислений, поскольку в этом случае кодовая комбинация в регистре 13 и, соответственно, реверсивном счетчике 2J3 сооттетствует отклонению частоты перестраиваемого генератора 7 от заданного значения на величину f , не превышающую требуемой на данном эта- пр точности подстройки 4f,.

Этот же сигнал проходит через элемент ИЛИ 19 и устанавливает первый триггер 15 в нулевое состояние. После чего начинается второй этап подстройки.

При М . N упр сигнал логической , единиц формируется на втором выходе (На первом - нуль) блока 12 и, поступая на соответствующий вход регистра 1р7 осуществляет коррекцию кода регистра 13 - сброс в нуль старшего ррзряда па первом цикле подстройки и (m-i+l)-ro разряда на i-м цикле. Коррекция состояния соответствующих разрядов реверсивного счетчика 23 производится на следующем цикле подстройки при переходе от первого такта к второму одновременно с записью единицы в следующий (младший) разряд регистра 13 последовательных приближений.

При М N уПр на обоих выходах блока 12 формируются сигналы логического нуля корректировка кода регистра 13 и9 соответственно, реверсивного счетчика 23 не происходит, поскольку в ранном случае для уменьшения частотного рассогласования необходимо увеличить управляющее напряжение с выхода преобразователя 6.

После окончания (1 + 2)-го такта заканчивается i-й/ цикл подстройки, в результате которого определено значение (m-i+l)-ro разряда регистра 13 по- следовательных приближений.. Определение значения разрядов регистра 13 в ходе подстройки частоты происходит от старших разрядов к младшим.

Далее процесс подстройки повторяется в соответствии с описанным алгоритмом до окончания цикла, на котором фиксируется равенство кодов, либо до завершения всех m циклов.

Таким образом, после окончания первого этапа на выходе элемента ИЛИ 19 формируется единичный сигнал,

0 который устанавливает первьй триггер 15 в нулевое состояние, однако третий триггер 25 своего состояния не изменяет, и импульсы тактовой частоты проходят через элемент И 16 на вход

5 дополнительного счетчика 17.

На втором этапе подстройки нулевой выходной сигнал первого триггера 15, поступая на вход управления коммутатора 22, переключает его таким обра0 зом, что на его выход проходит сигнал с частотой спорого генератора Ј0 . Этот же сигнал нулевого уровня посту- опает на вход управления БСК 24 и устанавливает его в состояние, обеспе,5 чивающее трансляцию входного кода на выход блока без сдвига, а также на второй вход дополнительного элемента ИЛИ 26, снимая тем самым блокировку коррекции кода реверсивного счетчика

0 23, которая была на первом этапе.

Далее процесс подстройки, описанный выше, повторяется. Отличие состоит в том, что длительность каждого такта, в том числе и времени счета,

5 в два раза больше, чем на первом этапе.

Единичное состояние дополнительного триггера 25 разрешает прохождение сигнала тактовой частоты 1:0 через

0 элемент И 16 на вход дополнительного счетчика 17. Во время первого такта на первом выходе дешифратора 18 формируется сигнал логической единицы, который устанавливает счетчик 11 в

5 нулевое состояние.

При переходе к второму такту перепад сигнала из 1 в О на первом выходе дешифратора 18 переписывает состояние регистра 13 в реверсивный

Q счетчик 23, при этом состояние регистра 13 не изменяется. Единичный сигнал на втором выходе дешифратора 18 устанавливает второй -триггер 20 в единичное состояние, которое обеспег чивает замыкание ключа 10 и разрешает тем самым прохождение выходного сигнала смесителя 8 через ключ 10 на вход счетчика 1. В течение следующих 1 тактов на выходе второго триггера

20 сохраняется сигнал единичного уро« вня и производится измерение частоты выходного сигнала смесителя 8 с удвоенной точностью путем заполнения счет чика 11. На (1 + 2)-м такте единичный сигнал формируется на третьем выходе дешифратора 18 и устанавливает второй триггер 20 в нулевое состояние, размыкая тем самым ключ 10 и прекра- щая заполнение счетчика П. Далее за время этого такта производится сравнение кода, накопленного к моменту окончания счета счетчика 11, с кодом на выходе кодозадающего блока 2. После окончания (1 t 2)-го такта перепад сигнала из 1 в О на третьем выходе дешифратора 18 поступает на тактовый вход дополнительного триггера 25 и устанавливает на его выходе состоя- ние, равное входному, т.е. нулевое, так как первый триггер 15 установлен в нулевое состояние при переходе от первого этапа к второму. Нулевой сигнал на выходе дополнительного тригге- ра 25, поступая на элемент И 16, запрещает прохождение сигнала тактовой частоты f на вход дополнительного счетчика 17.

По результатам сравнения кодов на (1 + 2)-м такте второго этапа под-, стройки также возможны три варианта: М Nvnp; М Nynp ; М Nynp.

При М К v,np на первом выходе блока 12 формируется сигнал логической единицы, а на втором - нуль. Этот сигнал не изменяет состояния регистра 13 и через дополнительньй элемент ИЛИ 26 осуществляет блокировку коррекции состояния реверсивного счетчика 23, ко- торое в этом случае не изменяется.

При М Nvnp сигнал логической единицы формируется на втором выходе на первом - нуль блока 12. Под действием этого сигнала, поступающего на информационный вход реверсивного счетчика 2.3, в тактовьй момент времени, определяемый перепадом из 1 в О сигнала на третьем выходе дешифратора 18, производится коррекция кода ревер сивного счетчика 23 на единицу младшего разряда в сторону уменьшения.

При М N ч(Пр на обоих выходах блбг ка 12 формируются сигналы нулевого уровня.. Под действием нулевого сигна- ла на втором выходе блока 12 в момент перехода сигнала на. третьем выходе де- дешифратора 18 из 1 в О произвол- дитея коррекция кода реверсивного

счетчика 3 на единицу младшего раз-ряда в сторону увеличения.

Процесс подстройки на этом заканчивается.

Таким образом, максимальное время поиска кодовой комбинации, соответствующей заданной частоте перестраиваемого генератора 7 с ошибкой,не превышающей заданного значения df, равно

t (га + 2)(1 + 2)/2 f .

О

Быстродействие известного устройства равно

t m (I + 2)/f 0.

Таким образом, быстродействие предлагаемого устройства при m 3 в (2 m/m + 2) раза выше, чем у известного устройства при одинаковой точ- ;ности подстройки. Это достигается благодаря работе с удвоенной тактовой частотой 2 f0 , а требуемая точность подстройки обеспечивается дополнительным циклом подстройки с удвоенной точностью (тактовая частота равна Ј0) и последующей коррекцией кода управления .

Формула изобретения

Устройство автоматической подг-. стройки частоты по авт. св. № 1298915 отличающееся тем, что, с целью повышения быстродействия, так тактовьй вход итерационного, вычислительного блока соединен с выходом опорного генератора через введение последовательно соединенные удвоитель частоты и коммутатор, второй вход которого подключен к выходу опорного генератора, выход итерационного вычислительного блока соединен с входом преобразователя код - напряжение че4- рез .введенный реверсивный счетчик, при этом входами реверсивного счетчика являются входы начальной установки, а выходами - разрядные выходы реверсивного счетчика, выход счетчика соединен с входом блока сравнения кодов через блок сдвига кода, а в итерационном вычислительном блоке выход первого триггера соединен с вторым входом элемента И через введенный дополнительньй триггер, входом которого является информационный вход, кроме того, между первым выходом блока сравнения кодов и входом разрешения

111539999 2

счета реверсивного счетчика введендополнительного триггера, вход уста- дополнительный элемент ИЛИ, второйновки которого подключен к выходу вход которого подключен к управляющимформирователя импульсов, вход разре- входам блока сдвига кода и коммутато- gшения записи реверсивного счетчика ра, а также к выходу первого тригге-соединен с первым выходом дешифратора, причем вход синхронизации ревер-Ра а информационный вход реверсив- сивного счетчика соединен с третьимного счетчика - с вторым выходом бло- выходом дешифратора и тактовым входомка сравнения кодов.

| Устройство автоматической подстройки частоты | 1985 |

|

SU1298915A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-01-30—Публикация

1987-07-15—Подача