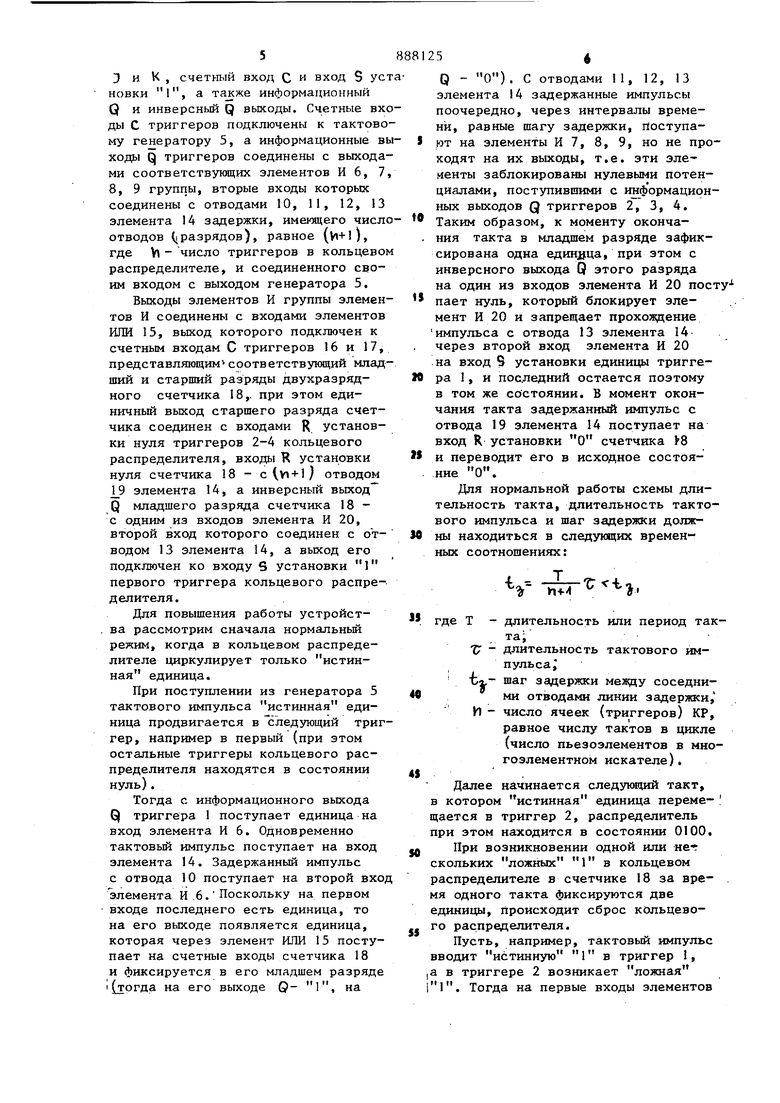

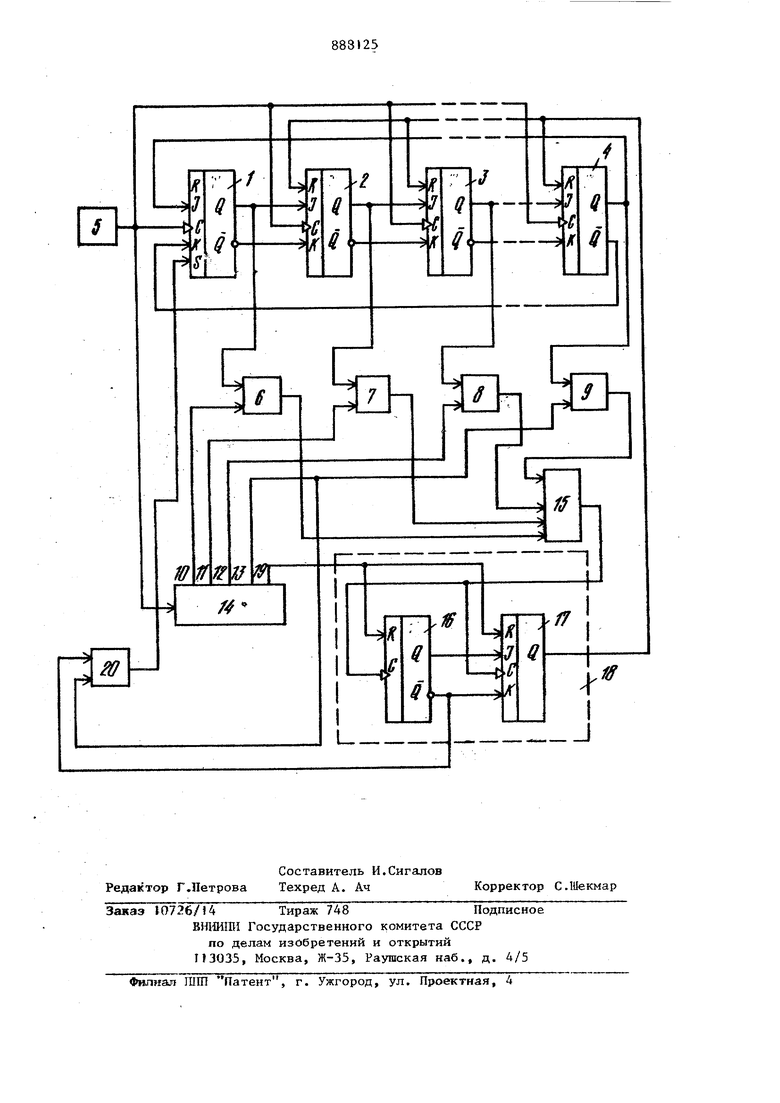

Изобретение относится к устройст|Вам, применяемым в системах контроля автоматике и информационно-измерительной технике и может быть использовано в различных отраслях машиностроения и вычислительной технике, в системах с последовательным опросом контролируемых объектов. Использование кольцевых распределителей в качестве элементов, обес печивающих последовательность опроса, решает задачу согласования многоэлементного искателя с одним измерительным каналом, т.е. появляется возможность использовать информацию от h элементов искателя при наличии одного измерительного канала. Для выполнения указанной функции в кольцевом распределителе должна циркулировать одна истинная 1, т.е. в каждый момент времени на кон троль вьшодится один объект. Вследствие возмущающих воздействий в кольцевом распределителе, воз никают ложные 1, что приводит к одновременному включению в канал измерения нескольких объектов, а также возможно исчезновение истинной 1. Надежность и помехозащищенность кольцевого распределителя может быть повышена за счет обеспечения коррекции известных. Так, например, известно устройство для подавления помех в бесконтактных кольцевых распределителях, содержащее логические элементы ИЛИ, И, ячейки антисовпадений, генератор запуска и ключ Ll Однако йто устройство требует установки дополнительного блока, разрывающего линию связи в системе в течение цикла подавления помех. Известно также устройство для коррекции сбойных кодов, содержащее блок фиксации помех и триггер 2. Недостатком этих устройств являгтся низкое быстродействие, которое обусловлено тем, что ложная единица исключается из кольцевого распределителя путем последовательной передачи ее из предьщущегЬ ячейки в последующую, пока она не будет передана в последнюю ячейку, в то время как передача единиды из послед ней ячейки в первую запрещена. Время исключения ложной единиды может составлять до двух циклов. Наиболее близким решением по технической сущности и достигаемому результату является бесконтактный кольцевой распределитель с подавлением помех, содержащий И триггеров, счетными вхо дами соединенных с вькодом генератора тактовых импульсов, элемент И, выход которого подключен к входу установки 1 триггера младшего из И разряда, элемент ИЛИ, входы которо го подсоединены к инверсным выходам И -1 триггеров младших разрядов, вто .рой элемент И, вторую схему ИЛИ и элемент НЕ. Первый вход второго элемента ШШ соединен с выходом первого элемента И, второй - с шиной синхронизации, а выход - с входами уставов ки нуля h триггеров. Первый вход второго элемента И подключен к генератору тактовых импульсов, второй к инверсному выходу триггера старшего разряда, а третий - к выходу первого элемента ИЛИ через элемент НЕ p Недостатком предлагаемого устройства является то, что оно не обеспечивает высокого быстродействия в подавлении помех, так как ложная единица исключается из кольцевого распределителя путем последовательной передачи единицы из предыдущей ячейки в последующую, пока либо истинная единица, либо ложная единица не достигнет ячейки старшего разряда. Время исключения ложной единицы может составить до 1 цикла, в течение тактов, при условии, что цикл состоит из У тактов (например, если истинная единица и ложная единица находятся в первых двух ячейках младших разрядов). Цель изобретения - разработка устройства для подавления помех в кольцевых распределителях, позволяющего повысить быстродействие. Поставленная цель достигается тем что в устройство для коррекции/сбой ных кодов в кольцевом распределителе, содержащее VI-разрядный кольцевой триггерный регистр сдвига, тактовый генератор, элемент И и элемент ИЛИ, причем вькод тактового генератора соединен с тактовым входом h разрядного кольцевого триггерного регистра сдвига, единичный и нулевой выходы каждого -i -го триггера кольцевого У -разрядного триггерного регистра сдвига соединены соответственно с входами и и К (f+1)-го триггера, а выходы п-го триггера соединены с входами первого триггера И-разрядного кольцевого триг-гарного регистра сдвига, выход элемента И соединен с единичным установочньм входом триггера первого разряда У -разрядного кольцевого триггерного разряда сдвига., в него введена группа элементов И, двухразрядный счетчик и элемент задержки, причем единичный выход каждого триггера VI -разрядного кольцевого триггерного регистра сдвига соединен с первым входом соответствующего элемента И группы, выход каждого элемента И группы соединен с соответствующим входом элемента ИЛИ, выход которого соединен со счетным входом двухразрядного счетчика, первый,вы-, ход двухразрядного счетчика соединен с нулевым установочным входом всех триггеров, кроме первого И-разрядного кольцевого триггерного регистра сдвига, выход тактового генератора соединен с входом элемента задержки, h-выходов которого соединены с вторыми входами соответствующих элементов И группы, ( и + 1)-й выход элемента задержки соединен с усягановочньм входом нуля двухразрядного счетчика, второй выход двухраз- рядного счетчика соединен с первым входом элемента И, второй вход которого соединен с И-м выходом элемента задержки, первый и второй триггеры, причем единичный и нулевой выходы первого триггера соединены соответственно с входом 3 и К второго триггера, единичный выход которого является первым выходом счетчика, нулевой выход первого триггера является вторым выходом счетчика, входы С первого и второго триггеров объединены и являются счетным входом счетчика, входы R первого и второго триггеров объединены и являются установочным входом нуля счетчика. На чертеже изображена блок-схема редлагаеМого устройства. Устройство содержит триггеры 1-4, ри этом каждый триггер имеет вход R установки нуля, управляющие входы 5 Э и К , счетный вход С и вход S ус новки 1, а информационный G} и инверсный Q выходы. Счетные вх ды С триггеров подключены к тактово му генератору 5, а информационные в ходы Gj триггеров соединены с выхода ми соответствующих элементов И 6, 7 8, 9 группы, вторые входы которых соединены с отводами 10, И, 12, 13 элемента 14 задержки, имеющего числ отводов (Разрядов), равное (и+О, где Vi - число триггеров в кольцево распределителе, и соединенного своим входом с выходом генератора 5. Выходы элементов И группы элемен тов И соединены с входами элементов ИЛИ 15, выход которого подключен к счетным входам С триггеров 16 и 17, представляющим соответствующий млад ший и старший разряды двухразрядкого счетчика 18,. при этом единичный выход старшего разряда счетчика соединен с входами R установки нуля триггеров 2-4 кольцевого распределителя, входы R установки нуля счетчика 18 - c(vi + l) отводом 9 элемента 14, а инверсный выход Q младшего разряда счетчика 18 с одним из входов элемента И 20, второй вход которого соединен с отводом 13 элемента 14, а выход его подключен ко входу в установки 1 первого триггера кольцевого распределителя. Для повышения работы устройст. ва рассмотрим сначала нормальньй режим, когда в кольцевом распределителе циркулирует только истинная единица. При поступлении из генератора 5 тактового импульса истинная единица продвигается в следующий триг гер, например в первый (при этом остальные триггеры кольцевого распределителя находятся в состоянии нуль). Тогда с информационного выхода G) триггера 1 поступает единица на вход элемента И 6. Одновременно тактовый импульс поступает на вход элемента 14. Задержанный импульс с отвода 10 поступает на второй вхо Ълемента И .6. Поскольку на первом входе последнего есть единица, то на его выходе появляется единица, которая через элемент ИЛИ 15 поступает на счетные входы счетчика 18 и фиксируется в его младшем разряде (тогда на его выходе Q- 1, на 5« Q О). С отводами II, 12, 13 элемента I4 задержанные импульсы поочередно, через интервалы времени, равные шагу задержки, поступают на элементы И 7, 8, 9, но не проходят на их выходы, т.е. эти элементы заблокированы нулевыми потенциалами, поступивпшми с информационных выходов Q триггеров 2, 3, 4. Таким образом, к моменту окончания такта в младшем разряде зафиксирована одна , при этом с инверсного выхода Q этого разряда на один из входов элемента И 20 поступает нуль, который блокирует элемент И 20 и запрещает прохояздение импульса с отвода 13 элемента 14 через второй вход элемента И 20 на вход 8 установки единицы триггера 1 , и последний остается поэтому в том же состоянии. В момент окончания такта задержанный импульс с отвода 19 элемента 14 поступает на вход R установки О счетчика t8 и переводит его в исходное состояние О. Для нормальной работы схемы длительность такта, длительность тактового импульса и шаг задержки должны находиться в следующих времен ных соотношениях: . где Т - длительность или период такта i tr - длительность тактового импульса|,- шаг задержки между соседними отводами линии задержки, И- число ячеек (триггеров) КР, равное числу тактов в цикле (число пьезоэлементов в многоэлементном искателе). Далее начинается следующий такт, котором кстинна;я единица переме- I ается в триггер 2, распределитель ри этом находится в состоянии 0100, При возникновении одной или нег кольких ложных 1 в кольцевом аспределителе в счетчике 18 за врея одного такта фиксируются две диницы, происходит сброс кольцевоо распределителя. Пусть, например, тактовый импульс водит истинную 1 в триггер 1, в триггере 2 возникает ложная 1. Тогда на первые входы элементов 7 И 6 и 8 будут поданы 1 с информационных выходов Q триггеров 1 и 3. Одновременно тактовый импульс посту пает на вход элемента 14 и после небольшой задержки с вывода 10 поступает на второй вход элемента И 6, далее с выхода последнего в виде 1 через элемент ИЛИ.15 посту пает на счетный вход счетчика I8 и фиксируется в младшем разряде тригг ера 16. В следукиций момент времени задержанный импульс с отвода 12 эле мента 14 появляется на втором входе элемента И 8 и с выхода его в виде 1 через элемент ИЛИ 15 поступает на счетный вход счетчика 18 и фикси руется уже в старшем разряде триггера 17, триггер которого переключа ется при этом в состояние 1, а тр гер 16 - в состояние 0. С выхода триггера 16 1 поступает на входы установки нуля триггеров 2-4 кольце вого распределителя и устанавливает их в нулевое состояние. Одновременно с инверсного выхода Q триггеpa 16 поступает 1 на вход элемент И 20, а на второй его вход поступает задержанный импульс с выхода 13 элемента 14. С выхода элемента И 20 поступает на вход 5 установки 1 триггера 1 и вводят истинную единицу в кольцевой распределитель. В момент окончания такта с вывода 19 элемента 14 задержанньй импульс поступает на вход- 1 установки нуля счетчика 18 и устанавливает его в исходное состояние 00). Далее работа кольцевого распределителя идет в нормальном режиме. На выходе элемента ИЛИ 15 в течение такта невозможно появление более двух импульсов при любом коли честве ложных единиц в кольцевом распределителе по той причине, что при записи второго импульса в старшем разряде &четчика 18, происходит обнуление триггеров 2-4, нулевые по тенциалы с информационных выходов которых заблокируют элементы И 7-9, что исключает появление третьего и т.д. импульсов. Таким образом, при наличии любого количества ложных единиц в кольцевом распределителе, счетчик 18 устанавливается в состояние 10, .и поэтому произойдет начальная установка в единицу триггера 1. При отсутствии помех в счетчик. 18 поступаетОДИН импульс, который 5. В переводит его в состояние О и в конце такта происходит установка счетчика в состояние 00 импульсом с вывода 19 элемента 14. При исчезновении (сбое) истинной единицы в любой момент времени в конце такта происходит установка счетчика 18 в состояние 00 импульсом с вывода 19 элемента I4. При этом с инверсного выхода ф триггера 16 счетчика 18 будет подана I на вход элемента И 20 и в конце следующего такта импульс с вывода 13 элемента 14, пройдя элемент 20, произведет начальную установку триггера 1 в единицу и дальнейшая работа происходит так, как описано вьше. Такое выполнение устройства, когда с каждым из триггеров кольцевого распределителя связан соответствующий элемент И, выходы которых поданы на элемент ИЛИ, при наличии связи последней с двухразрядным счетчиком, а также в соответствии с описанными связями между элементами устройства, обеспечивает подавление помех за время, меньшее или равное длительности одного такта, в то время как максимальное время подавления помех с помощью известного устройства (прототипа) равно длительности одного цикла, состоящее из У тактов, т.е. быстродействие повышено в h раз. Формула изобретения Устройство для коррекщ1и сбойных кодов в кольцевом распределителе, содержащее У -разрядный кольцевой триггерный регистр сдвига, тактовый генератор, элемент И и элемент ИЛИ, . причем выход тактового генератора соединен с тактовым входом У1-разрядного кольцевого триггерного регистра сдвига, единичный и нулевой выходы каждого 1-го триггера кольцевого Vi-разрядного триггерного регистра соединены соответственно со входами Э и К (.1 + 1)-го триггера, а выходы триггера соединены с входами первого триггера Vi-разрядного кольцевого триггерного регистра сдвига, выход элемента И соединен с единичным входом триггера первого разряда п-го разрядного кольцевого триггерного регистра сдвига, отличающееся тем, что, с целью повышения быстродействия, в него введены группы элементов И, двухразрядный счетчик и элемент задержки, причем единичный выход каждого триггера И-разрядного кольцевого триггерного регистра сдвга соединен с первым входом соответствующего элемента И группы, выход каждого элемента И группы соединен с соответствующим входом элемента ИЛИ, выход которого соединен со счетным входом двухразрядного счетчика, первый выход двухразрядного счетчика соединен с нулевым устано вочным входом всех триггеров, кроме первого h-разрчдного кольцевого триггерного регистра сдвига, выход тактового генератора соединен с входом элемента задержки, У -выходов которого соединены.с вторамк входами соответствующих элементов И группы, ()-й выход элемента задержки соединен с установочным входом нуля двухразрддного счетчика, второй выход двухразрадного счетчика соединен с первая входом элемента И, втор

вход которого соединен с Ц-м выходом элемента задержки.

2. Устройство по,п. 1, отличающееся тем, что двухразрядный счетчик содержит первый и второй триггеры, причем единичный и нулевой выходы первого триггера соединены соответственно с входами J и К второго триггера| единичный выход которого является перв1 м выходом счетчика, нулевой выход первого триггера является вторым выходов счетчика, входы С первого и второго триггеров объединены и являются счетным входом счетчика, входы R первого и второго триггеров объединены и являются установочньм входом нуля счетчика.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 208354, кл. G 06 F 11/00, 1969.

2.Авторское свидетельство СССР № 269614, кл. G 06 F 11/00, 1971.

3.Авторское свидетельство СССР № 653615, кл. G 06 F 11/00, 1979 (прототип).

k/

Ыг

а

J

Q

tk

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции сбоя в @ -разрядном кольцевом регистре сдвига | 1984 |

|

SU1176331A1 |

| Распределитель импульсов | 1982 |

|

SU1053288A2 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| "Генератор чисел в кодах "золотой" пропорции" | 1989 |

|

SU1711143A1 |

| Преобразователь кода Грея в параллельный двоичный код | 1990 |

|

SU1784963A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ С ПЕРФОЖЕТОНА | 1992 |

|

RU2037202C1 |

| Устройство цикловой синхронизации воспроизведения цифровой информации с носителя магнитной записи | 1989 |

|

SU1599895A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

Fа

ff

ю

/

W

Г

I

Сп

г

1

./г

LS

г

,7

- I

Авторы

Даты

1981-12-07—Публикация

1979-03-24—Подача