Изобретение относится к вычислительной технике и может применяться в информационно-измерительных системах Д.ПЯ сокращения объема накапливаемой и обрабатываемой информации.

Целью изобретения является повышение информативности устройства.

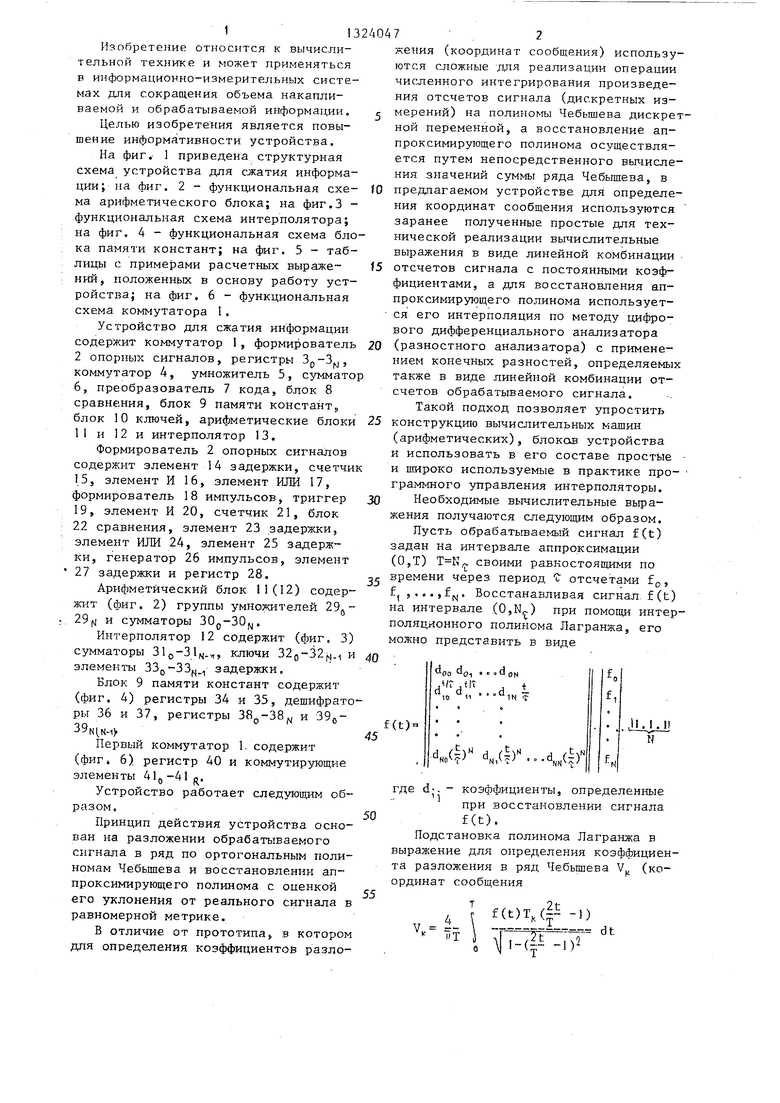

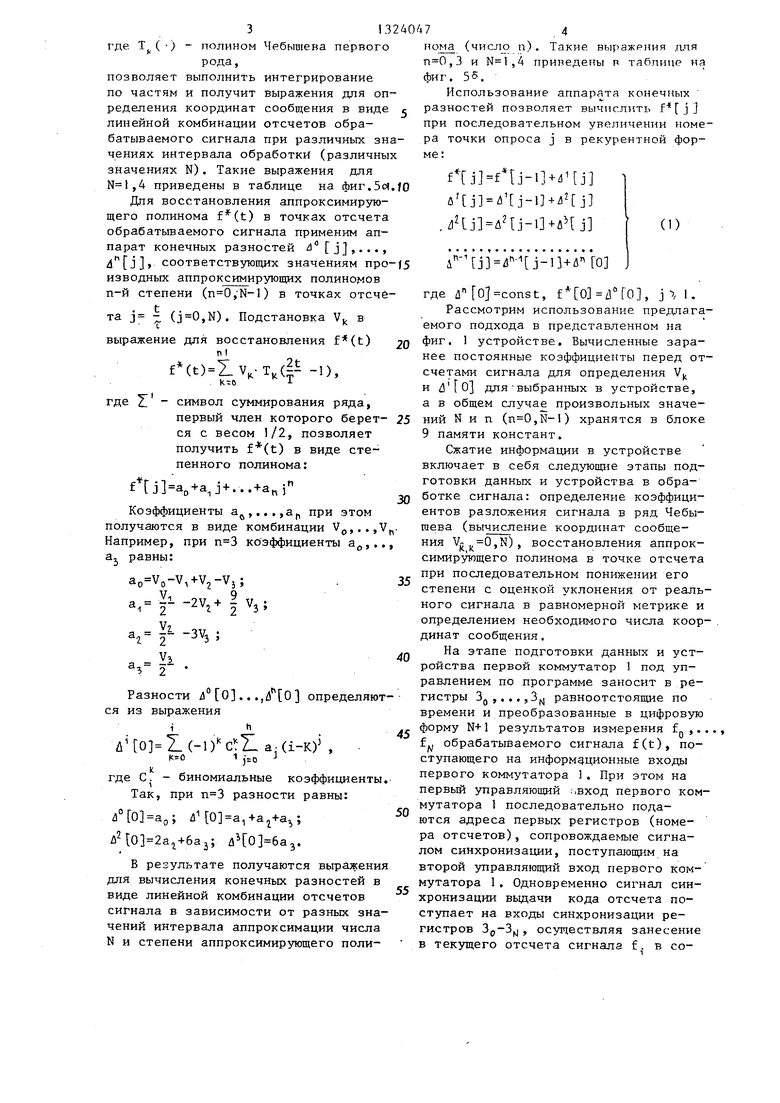

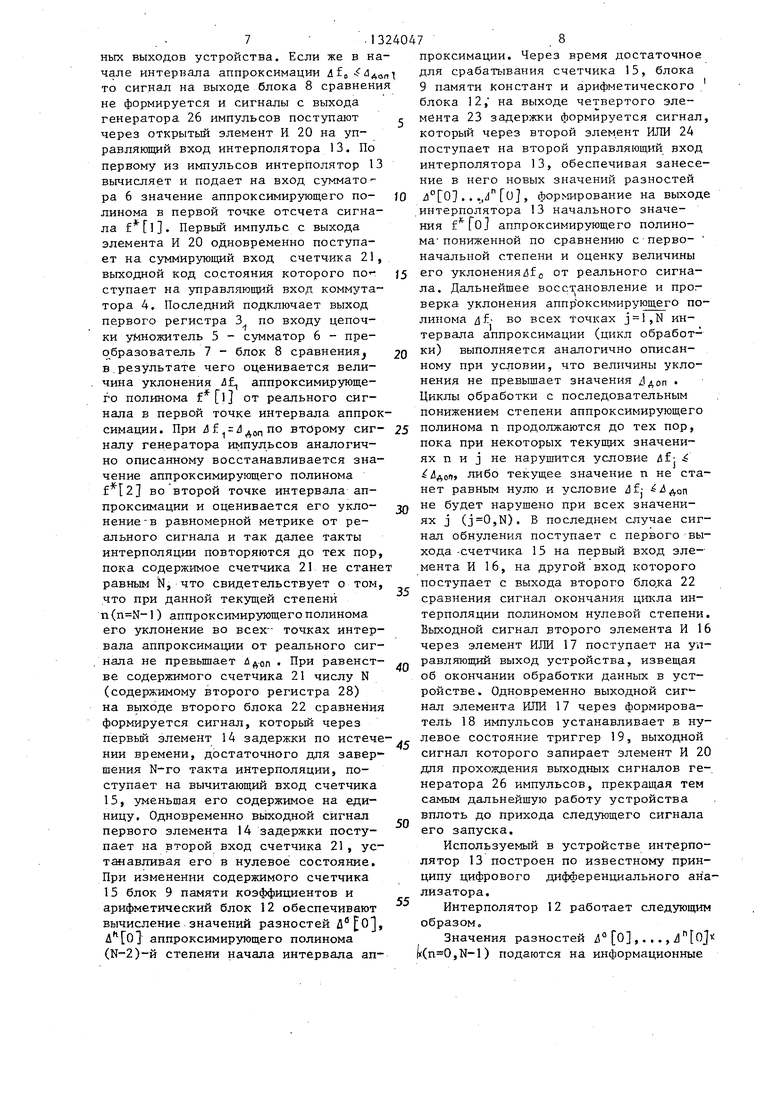

На фиг,- 1 приведена структурная схема устройства для с-жатия информации; на фиг. 2 - функциональная схема арифметического блока; на фиг.З - функциональная схема интерполятора; на фиг. 4 - функциональная схема блока памяти констант; на фиг, 5 - таблицы с примерами расчетных выражений, положенных в основу работу устройства; на фиг. 6 - функциональная схема коммутатора 1.

Устройство для сжатия информации содержит коммутатор 1, формирователь 2 опорных сигналов, регистры , коммутатор А, умножитель 5, сумматор 6, преобразователь 7 кода, блок 8 сравнения,

жения (координат сообщения) использу ются сложные датя реализации операции численного интегрирования произведения отсчетов сигнала (дискретных иэ- г мерений) на полиномы Чебышева дискре ной переменной, а восстановление аппроксимирующего полинома осуществляется путем непосредственного вычисл ния значений суммы ряда Чебышева, в

fO предлагаемом устройстве для определ ния координат сообщения используются заранее полученные простые для технической реализации вычислительные выражения в виде линейной комбинации

f5 отсчетов сигнала с постоянными коэффициентами, а для восстановления аппроксимирующего полинома использует- ся его интерполяция по методу цифро вого дифференциального анализатора

20 (разностного анализатора) с применением конечных разностей, определяемы также в виде линейной комбинации от счетов обрабатываемого сигнала.

Такой подход позволяет упростить

блок 9 памяти констант,, блок 10 ключей, арифметические блоки 25 конструкцию вычислительных машин II и 12 и интерполятор 13.(арифметических), блoкoJB устройства

Формирователь 2 опорных сигналов содержит элемент 14 задержки, счетчик 15, элемент И 16, элемент ШШ 17,

30

формирователь 18 импульсов, триггер 19, элемент И 20, счетчик 21, блок 22 сравнения, элемент 23 задержки, элемент ИЛИ 24, элемент 25 задержки, генератор 26 импульсов, элемент 27 задержки и регистр 28.

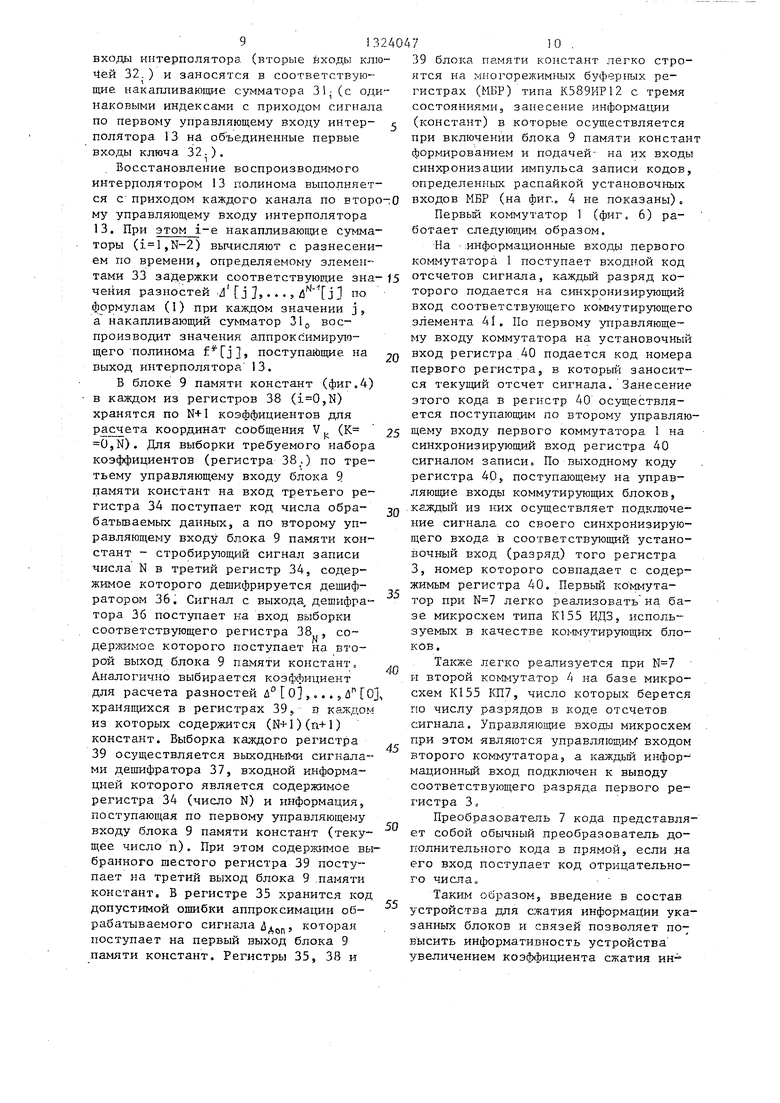

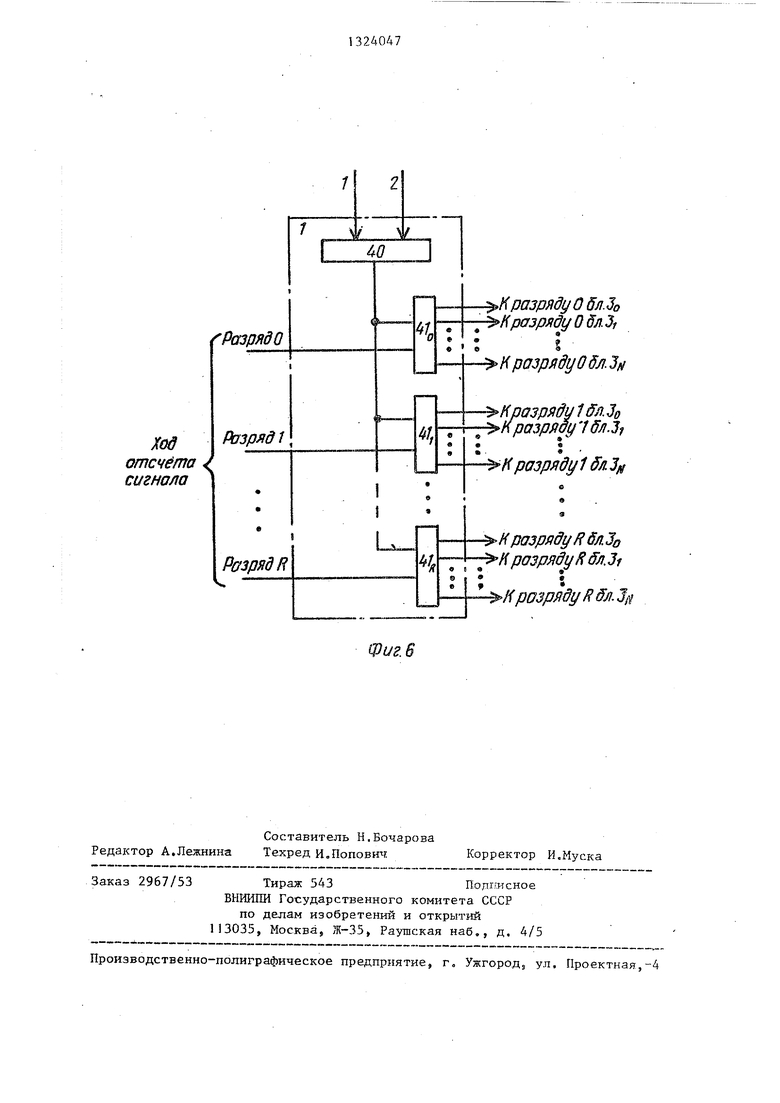

Арифметический блок 11(12) содер- жа-1т (фиг. 2) группы умножителей ; 29|vj и сумматоры ,.

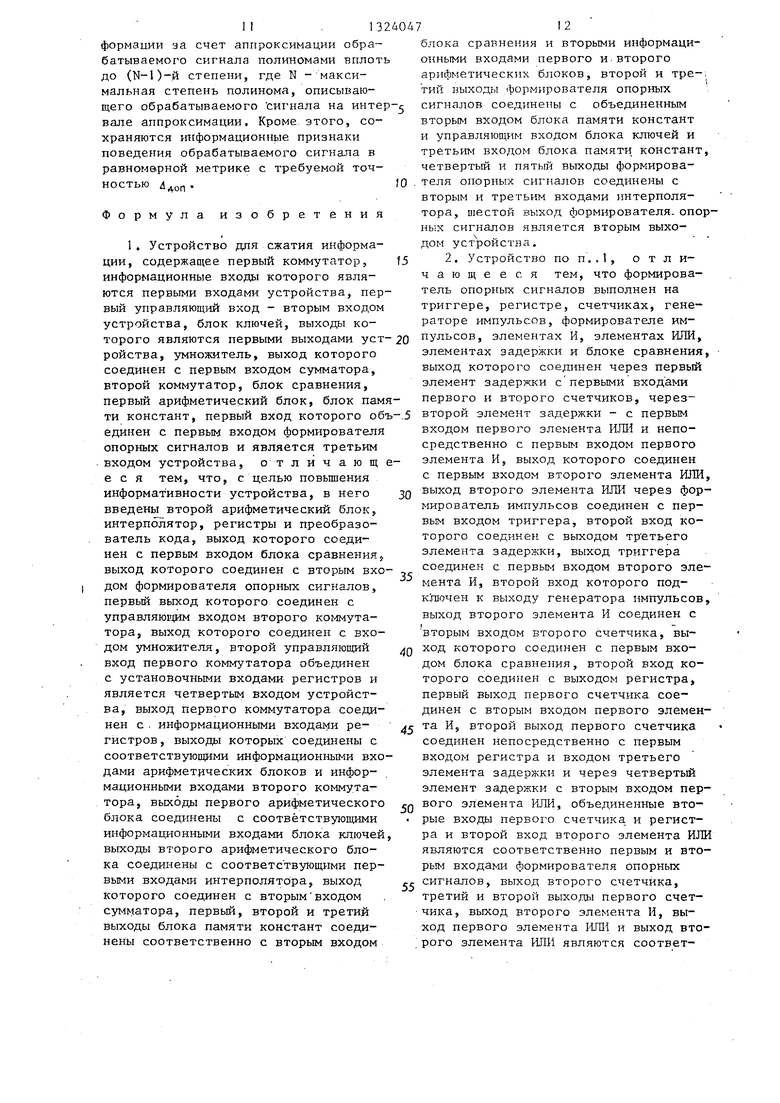

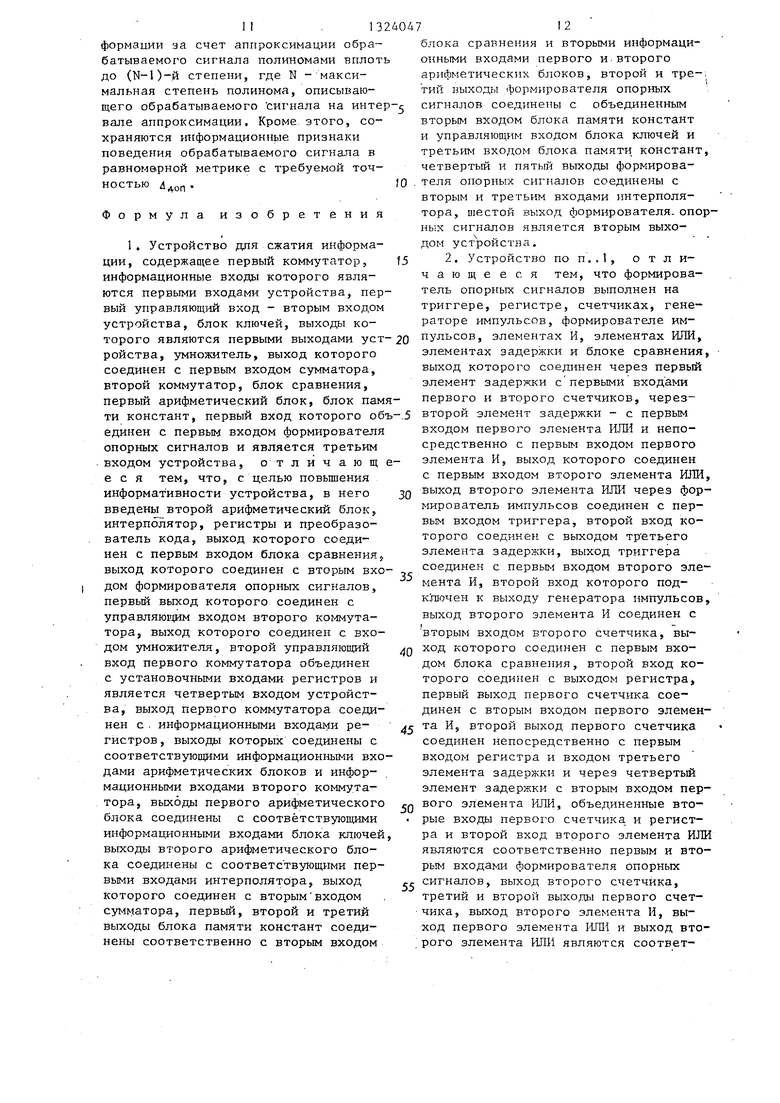

Интерполятор 12 содержит (фиг. 3) сумматоры 31,-31ц-ч ключи ,. и элементы ЗЗр-33. задержки.

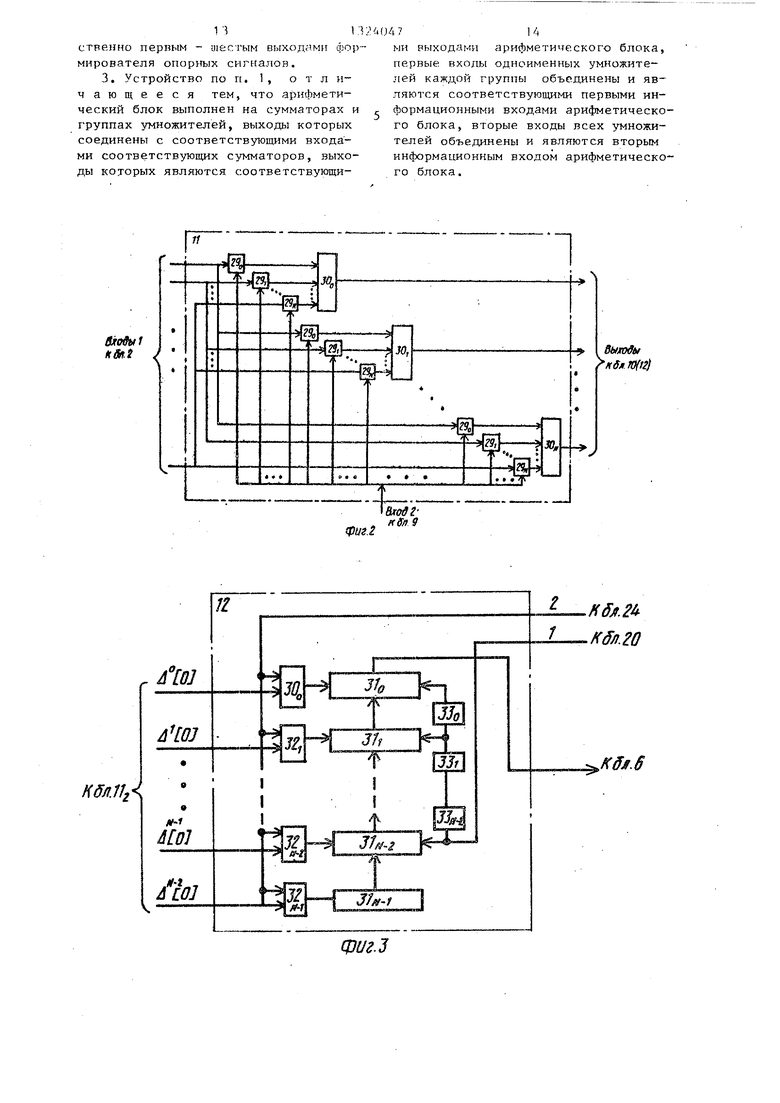

Блок 9 памяти констант содержит (фиг. 4) регистры 34 и 35, дешифраторы 36 и 37, регистры 38.,-38 и

и использовать в его составе просты и широко используемые в практике пр граммного управления интерполяторы.

Необходимые вычислительные вьфа- жения получаются следующим образом.

Пусть обрабатываемый сигнал f(t) задан на интервале аппроксимации (О,Т) своими равностоящими по времени через период С отсчетами f f| ,...,f. Восстанавливая сигнал. f( на интервале (0,U) при помощи инт поляционного полинома Лагранжа, его можно представить в виде

40

39к(ц-1

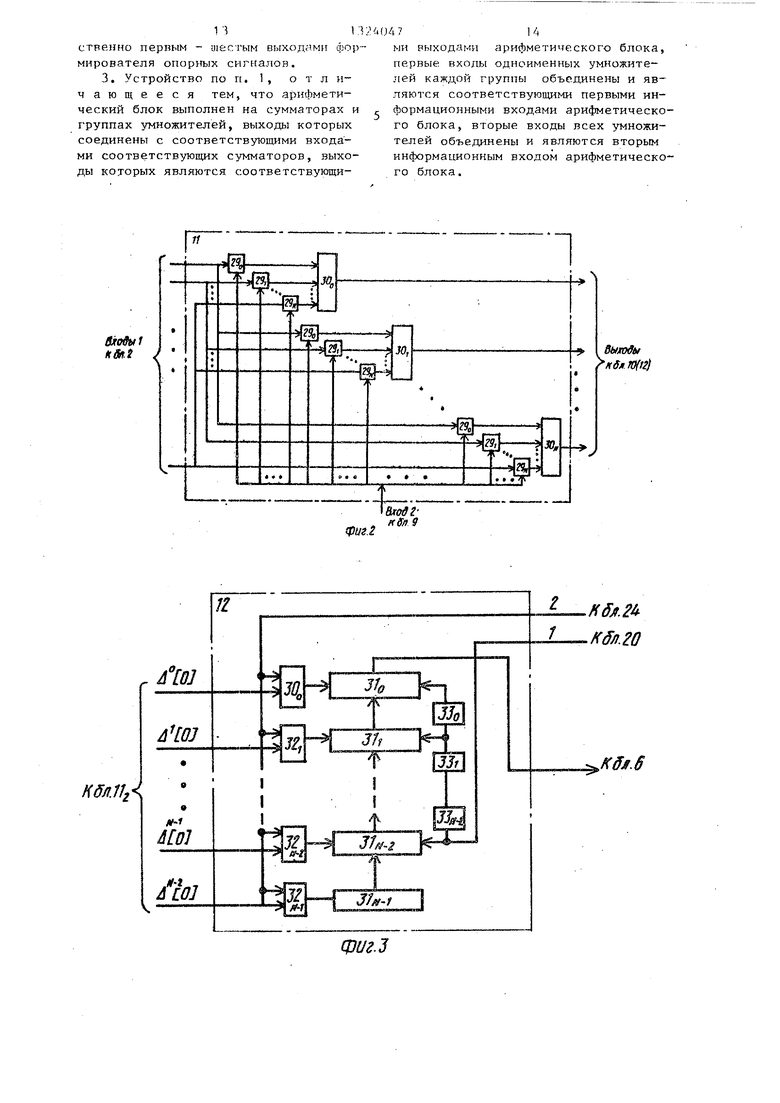

Первый коммутатор 1. содержит (фиг 4 6) регистр 40 и коммутирующие элементы 41,5 -41 .

Устройство работает следующим образом.

Принцип действия устройства основан на разложении обрабатываемого сигнала в ряд по ортогональным полиномам Чебьш:ева и восстановлении аппроксимирующего полинома с оценкой его уклонения от реального сигнала в равномерной метрике.

В отличие от прототипа, в котором для определения коэффициентов разло45

f(t)

N

50

55

где d-. - коэффициенты, определенные при восстановлении сигнала f(t).

Подстановка полинома Лагранжа в выражение для определения коэффицие та разложения в ряд Чебьщзева V (ко ординат сообщения

V : f Т)

f(t)T,( -О

fi-7p -1)2

-- dt

жения (координат сообщения) используются сложные датя реализации операции численного интегрирования произведения отсчетов сигнала (дискретных иэ- мерений) на полиномы Чебышева дискретной переменной, а восстановление аппроксимирующего полинома осуществляется путем непосредственного вычисления значений суммы ряда Чебышева, в

предлагаемом устройстве для определения координат сообщения используются заранее полученные простые для технической реализации вычислительные выражения в виде линейной комбинации отсчетов сигнала с постоянными коэффициентами, а для восстановления аппроксимирующего полинома использует- ся его интерполяция по методу цифрового дифференциального анализатора

(разностного анализатора) с применением конечных разностей, определяемых также в виде линейной комбинации отсчетов обрабатываемого сигнала.

Такой подход позволяет упростить

конструкцию вычислительных машин (арифметических), блoкoJB устройства

0

5

и использовать в его составе простые и широко используемые в практике про- граммного управления интерполяторы.

Необходимые вычислительные вьфа- жения получаются следующим образом.

Пусть обрабатываемый сигнал f(t) задан на интервале аппроксимации (О,Т) своими равностоящими по времени через период С отсчетами f , f| ,...,f. Восстанавливая сигнал. f(t) на интервале (0,U) при помощи интерполяционного полинома Лагранжа, его можно представить в виде

45

f(t)

N

где d-. - коэффициенты, определенные при восстановлении сигнала f(t).

Подстановка полинома Лагранжа в выражение для определения коэффициента разложения в ряд Чебьщзева V (координат сообщения

V : f Т)

f(t)T,( -О

fi-7p -1)2

-- dt

где. Т(-) - полином Чебышева первого

рода,

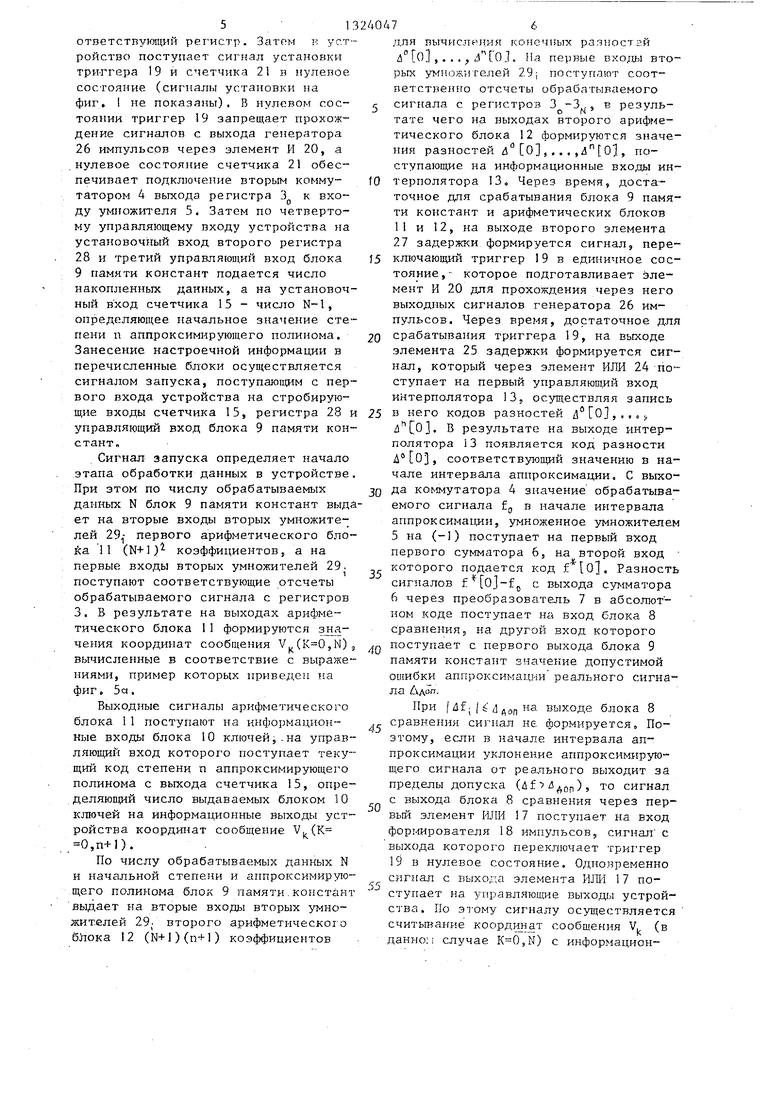

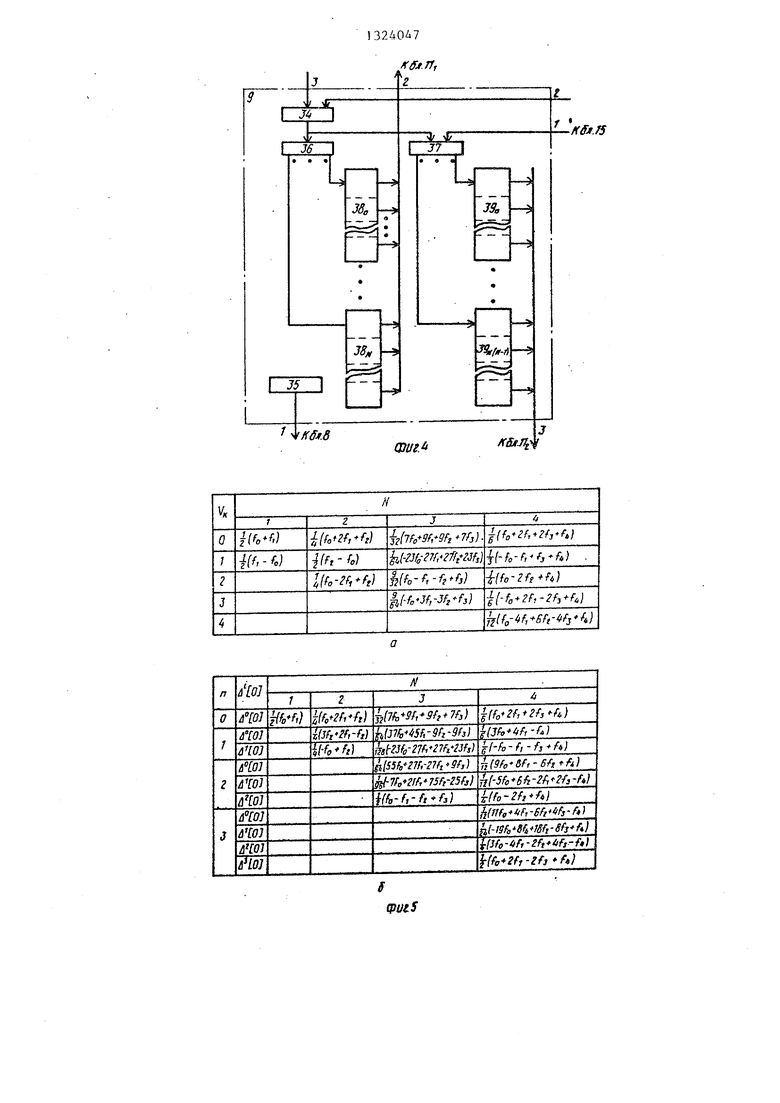

позволяет выполнить интегрирование по частям и получит выражения для определения координат сообщения в виде линейной комбинации отсчетов обрабатываемого сигнала при различных значениях интервала обработки (различных значениях N). Такие выражения для ,4 приведены в таблице на фиг.5с(

Для восстановления аппроксимирующего полинома f(t) в точках отсчета обрабатьшаемого сигнала применим аппарат конечных разностей й° j,..., соответствующих значениям производньгх аппроксимирующих полиномов п-й степени (, N-l) в точках отсчёта j - (,N). Подстановка Vj, в

выражение для восстановления f(t)

ni

f(t) ( -1), k:o где Z символ суммирования ряда,

первый член которого берет- ся с весом 1/2, позволяет получить f(t) в виде степенного полинома:

,+aJ + ...

Коэффициенты a,,,.,a при этом получаются в виде комбинации V(|,..,V Например, при коэффициенты а,., а, равны:

,+V,,-V3;

I 3;

а, 1 -3V3 ;

а Yi 3 2

Разности /5° о .. ., определяются из выражения

V (-l) а(1-кУ , .

К О

1 г-о

где С. - биномиальные коэффициенты. Так, при разности равны:

,; лЧо 2а +6аз; .

В результате получаются выражения для вычисления конечньгх разностей в виде линейной комбинации отсчетов сигнала в зависимости от разных значений интервала аппроксимации числа N и степени аппроксимирующего полиHOMia ( п). Такие выражения для ,3 и ,4 принедены в таблице на фи г. 5 5.

Использование аппарата конечных разностей позволяет вычислить f jJ при последовательном увеличении номера точки опроса j в рекурентной форме:

.d4j u4j-i +uHj

(1)

A 4j d -4J-n+dno

5

0

5

0

5

0

5

0

5

где d f0j const, , j -, 1.

Рассмотрим использование предлагаемого подхода в представленном на фиг, 1 устройстве. Вычисленные заранее постоянные коэффициенты перед отсчетами сигнала для определения V, и ZS lO для выбранных в устройстве, а в общем случае произвольных значений Кип (,N-l) хранятся в блоке 9 памяти констант.

Сжатие информации в устройстве включает в себя следующие этапы подготовки данных и устройства в обработке сигнала: определение коэффициентов разложения сигнала в ряд Чебы- шева (вычисление координат сообщения Vjjj,0,N), восстановления аппроксимирующего полинома в точке отсчета при последовательном понижении его степени с оценкой уклонения от реального сигнала в равномерной метрике и определением необходимого числа коор- . динат сообщения.

На этапе подготовки данных и устройства первой коммутатор 1 под управлением по программе заносит в регистры 3jj,..,,3| равноотстоящие по времени и преобразованные в цифровую форму N+1 результатов измерения f. ,..., f.j обрабатываемого сигнала f(t), поступающего на информационные входы первого коммутатора 1 . Прз этом на первый управляющий :.вход первого коммутатора 1 последовательно подаются адреса первых регистров (номера отсчетов), сопровождаемые сигналом синхронизации, поступающим на второй управляющий вход первого коммутатора 1. Одновременно сигнал синхронизации выдачи кода отсчета поступает на входы синхронизации регистров 3p-3nj , осуществляя занесение в текущего отсчета сигнала f. в соответствующий регистр. ( в устройство поступает сигнал установки триггера 19 и счетчика 21 в иулепое состояиие (сигналы установки на фиг. 1 не показаны). В нулевом состоянии триггер 19 запрещает прохожение сигналов с выхода генератора 26 импульсов через элемент И 20, а нулевое состояние счетчика 21 обеспечивает подключение вторым коммутатором 4 выхода регистра 3 к входу умножителя 5. Затем по четвертоу управляющему входу устройства на установочный вход второго регистра 28 и третий управляющий вход блока 9 памяти констант подается число накопленных данных, а на установочный вход счетчика 15 - число N-1, определяющее начальное значение степени 11 аппроксимирующего полинома. Занесение настроечной информации в перечисленные блоки осуществляется сигналом запуска, поступакицим с первого входа устройства на стробирую- щие входы счетчика 15, регистра 28 и управляющий вход блока 9 памяти констант

Сигнал запуска определяет начало этапа обработки данных в устройстве, При этом по числу обрабатываемых анных N блок 9 памяти констант выдает на вторые входы вторых умножителей первого арифметического бло- 11 (N+1) коэффициентов, а на первые входы вторых умножителей 29. поступают соответствующие отсчеты обрабатываемого сигнала с регистров 3, В результате на выходах арифметического блока 11 формируются зна- чения координат сообщения V|()5 В 1численные в соответствие с выражениями, пример которых приведен на фиг. За.

Выходные сигналы арифметического блока 11 поступают на информационные входы блока 10 ключей,-на управ- ляющин вход которого поступает текущий код степени п аппроксимирующего полинома с выхода счетчика 15, опре- деляюп(ий число выдаваемых блоком 10 ключей на информационные выходы устройства координат сообщение V|..(K 0,п+1).

По числу обрабатываемых данных N и начальной степени и аппроксимируюего полинома блок 9 памяти.констант вьщает на вторые вход|э1 вторых умноителей 29; второго арифметического блока 12 (N+l)(n+l) коэффициентов

для вычисле1 ия гсонечиых разностгй 5° о , , . . .1. На первые входа вторых у тиожителей 29j поступают соот- петствен го отсчеты обрабатываемого

сигнала с регистров 3 -3, в результате чего на выходах второго арифметического блока 12 формируются значения разностей d О ,.., ,л 01., поступающие на информационные входы интерполятора 13, Через время, достаточное для срабатывания блока 9 памяти констант и арифметических блоков 1 и 12, на выходе гзторого элемента 27 задержки формируется сигнал, переключающий триггер 19 в единичное состояние,- которое подготавливает :эле- мент И 20 для прохождения через него выходных сигналов генератора 26 импульсов. Через время, достаточное для

срабатывания триггера 19, на выходе элемента 25 задержки формируется сит- нал, который через элемент ИЛИ 24 поступает на первый управляюпц й вход интерполятора 13. осуществляя запись

в него кодов разностей ,,,.,,

, В результате на выходе интерполятора 13 появляется код разности , соответствующий значению в начале интервала аппроксимации, С выхода коммутатора 4 значение обрабатываемого сигнала у в начале интервала аппроксимапд и, умноженное умножителем

5на (-1) поступает на первый вход первого сумматора 6, на второй вход

которого подается код . Разность сигналов с выхода сумматора

6через преобразователь 7 в абсолютном коде поступает на вход блока 8 сравнения, на другой вход которого

поступает с первого выхода блока 9 памяти констант значение допустимой ошибки аппроксимации реального сигнала АЛОППри (df; ( ( д на выходе блока 8

сравнения сигнал не формируется. Поэтому, если в начале интерзала аппроксимации уклонение аппроксимирующего сигнала от реального выходит за пределы допуска (), то сигнал с выхода блока 8 сравнения через первый элемент Ш1И 17 поступает на вход формирователя 18 импульсов, сигнал с выхода которого переключает триггер 19 в нулевое состояние. Одновременно сигнал с выхода элемента ИШ I7 поступает на управляю11 ие выходы устройства. По этому сигналу осуществляется считьгоание коорди нат сообщения V (в данном случае ,N) с информацион

ных выходов устройства. Если же в начале интервала аппроксимации то сигнал на выходе блока 8 сравнения не формируется и сигналы с выхода генератора 26 импульсов поступают через открытый элемент И 20 на управляющий вход интерполятора 13. По первому из импульсов интерполятор 13 вычисляет и подает на вход - ра 6 значение аппроксимирующего полинома в первой точке отсчета сигнала . Первый импульс с выхода элемента И 20 одновременно поступает на суммирующий вход счетчика 21, выходной код состояния которого nof ступает на зшравляющий вход коммута- тора 4. Последний подключает выход первого регистра 3 по входу цепочки умножитель 5 - сумматор 6 - пре2Q ки) выполняется аналогично описанобразователь 7 - блок 8 сравнения в.результате чего оценивается вели- . чина уклонения 4f аппроксимирующего полинома от реального сигнала в первой точке интервала аппроксимации. При 4 /ЗдопПО второму сиг- 25 полинома п продолжаются до тех пор, налу генератор-а импульсов аналогич- пока при некоторых текущих значениному при условии, что величины укло нения не превышает значения /1доп Циклы обработки с последовательным понижением степени аппроксимирующег

но описанному восстанавливается значение аппроксимирующего полинома во второй точке интервала аппроксимации и оценивается его уклонение -в равномерной метрике от реального сигнала и так далее такты интерполяции повторяются до тех пор, пока содержимое счетчика 21 не станет равным N, что свидетельствует о том, что при данной текущей степени n() аппроксимирздащегополинома его уклонение во всех- точках интервала аппроксимации от реального сиг- нала не превьш1ает Дд-оп При равенстве содержимого счетчика 21 числу N (содержимому второго регистра 28) на выходе второго блока 22 сравнения формируется сигнал, которьш через первьй элемент 14 задержки по истечении времени, достаточного для завершения N-ro такта интерполяции, поступает на вычитающий вход счетчика 15, уменьшая его содержимое на единицу. Одновременно выходной сигнал первого элемента 14 задержки поступает на второй вход счетчика 21, устанавливая его в нулевое состояние. При изменении содержимого счетчика 15 блок 9 памяти коэффициентов и арифметический блок 12 обеспечивают вычисление значений разностей 0, аппроксимирующего полинома (N-2)-и степени начала интервала аппроксимации. Через время достаточное для срабатывания счетчика 15, блока 9 памяти констант и арифметического / блока 12, на выходе четвертого эле- мента 23 задержки формируется сигнал, который через второй элемент ИЛИ 24 поступает на второй управляющий вход интерполятора 13, обеспечивая занесение в него новых значений разностей

.. .,Л о, формирование на выходе интерполятора 13 начального значения аппроксимирующего полинома пониженной по сравнению с перво- начальной степени и оценку величины

его уклоненияdfо от реального сигнала. Дальнейшее восстановление и прог верка уклонения аппр оксимирующего полинома во всех точках j l,N интервала аппроксимации (цикл обработки) выполняется аналогично описанполинома п продолжаются до тех пор, пока при некоторых текущих значениполинома п продолжаются до тех пор, пока при некоторых текущих значениному при условии, что величины уклонения не превышает значения /1доп Циклы обработки с последовательным понижением степени аппроксимирующего

0

5

0

5

0

5

ях п и j не нарушится условие df- . Лдо либо текущее значение п не станет равным нулю и условие f- 4доп не будет нарушено при всех значениях j (,N). В последнем случае сигнал обнуления поступает с первого-выхода -счетчика 15 на первый вход элемента И 16, на другой вход которого поступает с выхода второго бло,ка 22 сравнения сигнал окончания цикла интерполяции полиномом нулевой степени. Выходной сигнал второго элемента И 16 через элемент ИЛИ 17 поступает на управляющий выход устройства, извещая об окончании обработки данных в устройстве. Одновременно выходной сигнал элемента ИЛИ 17 через формирователь 18 импульсов устанавливает в нулевое состояние триггер 19, выходной сигнал которого запирает элемент И 20 для прохождения выходных сигналов ге-. нератора 26 импульсов, прекращая тем самым дальнейшую работу устройства вплоть до прихода следующего сигнала его запуска.

Используемый в устройстве интерполятор 13 построен по известному принципу цифрового дифференциального ан а- лизатора.

Интерполятор 12 работает следующим образом

Значения разностей 4° О ,. .., t(,N-l) подаются на информационные

входы интерполятора (вторые входы ей 32.) и заносятся в соответствующие накапливающие сумматора 31-(с одинаковыми индексами с приходом сигнала по первому управляющему входу интер- полятора 13 на объединенные первые входы ключа 32.).

Восстановление воспроизводимого интерцолятором 13 полинома выполняется С приходом каждого канала по второ му управляющему входу интерполятора 13, При этом i-e накапливающие Сумматоры (,N-2) вычисляют с разнесением по времени, определяемому элементами 33 задержки соответствующие зна- чения разностей Л J J j j по формулам (1) при каж.цом значении j , а накапливающий сумматор 31 воспроизводит значения аппроксимирующего полинома , поступающие на выход интерполятора 13.

Б блоке 9 памяти констант (фиг„4) в каждом из регистров 38 (,N) хранятся по N+1 коэффициентов для координат сообщения V (К 0,N). Для выборки требуемого набора коэффициентов (регистра 38;) по третьему управляющему входу блока 9 памяти констант на вход третьего регистра 34 поступает код числа обра- батываемых данных, а по второму управляющему входу блока 9 памяти констант - стробирующий сигнал записи числа N в третий регистр 34, содержимое которого дешифрируется дешиф

ратором 36. Сигнал с выхода, дешифратора 36 поступает на вход выборки соответствующего регистра 38, содержимое которого поступает на второй выход блока 9 памяти констант. Аналогично выбирается коэфс1шциент для расчета разностей д t 0 ,..., d O хранящихся в регистрах 39, в кэ-ждом из которых содержится (№-l)(ri+l) констант. Выборка каждого регистра 39 осуществляется выходными сигналами дещифратора 37, входной информацией которого является содержимое регистра 34 (число N) и информация, поступающая по первому управляющему входу блока 9 памяти констант (текущее число п). При этом содержимое выбранного шестого регистра 39 поступает на третий выход блока 9 .памяти констант, В регистре 35 хранится код допустимой ошибки аппроксимации об- раба1ъшаемого сигнала , которая поступает на первый выход блока 9 констант. Регистры 35, 38 и

5 д

5

0

5

0

5

39 блока памяти констант легко строятся на многорежимных буферных регистрах (МБР) типа К589ИР12 с тремя состояниями, занесение информации (констант) в которые ocya ecтвляeтcя при включении блока 9 памяти констант формированием и подачей- на их входы синхронизации импульса записи кодов, определенных распайкой установочных входов МБР (на фиг.„ 4 не показаны),

Первьм коммутатор 1 (фиг, 6) работает следующим образом.

На .информационные входы первого коммутатора 1 поступает входной код отсчетов сигнала, каждый разряд которого подается на синхронизир ующий вход соответств ующего ком1-1утирующего элемента 41, По первому управляющему входу коммутатора на установочный вход регистра 40 подается код номера первого регистра, в которьш заносится текущий отсчет сигнала. Занесение этого кода в регистр 40 осуществляется поступающим по второму управляющему входу первого коммутатора 1 на синхронизир ующий вход регистра 40 сигналом записи. По выходному коду регистра 40, поступающему на управляющие входы коммутир ующих блоков, .каждый из них осуществляет подключение сигнала, со своего синхронизирующего входа в соответствующий установочный вход (разряд) того регистра 3, номер которого совпадает с содержимым регистра 40. Первый коммутатор при легко реализовать на базе микросхем типа К155 РЩЗ, используемых в качестве ко1-1мутирующих блоков.

Также легко реализуется при и второй коммутатор 4 на базе микросхем К155 КП7, число которых берется по числу разрядов в коде отсчетов сигнала. Управляющие входы микросхем при этом являются управляющим входом второго комнутатора, а каждый информационный вход подключен к выводу соответствующего разряда первого регистра За

Преобразователь 7 кода представляет собой обычный преобразователь дополнительного кода в прямой, если на его вход поступает код отрицательного числа.

Таким образом, введение в состав устройства для сжатия информации указанных блоков и связей позволяет повысить информативность устройства увеличением коэффициента сжатия ин-°

II . 1324047 формации за счет аппроксимации обрабатываемого сигнала полиномами вплоть до (N-l)-fl степени, где N - максимальная степень полинома, описывающего обрабатываемого сигнала на интер- вале аппроксимации. Кроме этого, сохраняются информационные признаки поведения обрабатываемого сигнала в равномерной метрике с требуемой точностью 4доп

Формула изобретения

1. Устройство для сжатия информации, содержащее первый коммутатор, 15 информационные входы которого являются первыми входами устройства, первый управляющий вход - вторым входом устройства, блок ключей, выходы которого являются первыми выходами уст- 20 ройства, умножитель, выход которого соединен с первым входом сумматора, второй коммутатор, блок сравнения, первый арифметический блок, блок памяти констант, первый вход которого объ-.5 единен с первым входом формирователя опорных сигналов и является третьим . входом устройства, отличающееся тем, что, с целью повьшения информативности устройства, в него ЗО введены второй арифметический блок, интерполятор, регистры и преобразователь кода, выход которого соединен с первым входом блока сравненияj выход которого соединен с вторым вхо- дом формирователя опорных сигналов, первый выход которого соединен с управляющим входом второго ког-1мута- тора, выход которого соединен с входом умножителя, второй управляющий р вход первого коммутатора объед1 нен с установочными входами регистров и является четвертым входом устройст

ва, выход первого коммутатора соединен с . информационными входами регистров , выходы которых соединены с соответствующими информационными входами арифметических блоков и информационными входами второго коммутатора, выходы первого арифметического блока соединены с соответствующими информационными входами блока ключей выходы второго арифметического блока соединены с соответствующими первыми вxoдa ш интерполятора, выход которого соединен с вторым входом сумматора, первый, второй и третий выходы блока памяти констант соединены соответственно с вторым входом

- р

5

Q

5

блока сравнения и вторыми информационными входами первого и.второго арифметических блоков, второй и тре-: тий выходы формирователя опорных сигналов соединены с объединенным вторым входом блока памяти констант и управляющим входом блока ключей и третьим входом блока памяти, констант, четвертый и пятый выходы формирователя опорных сигналов соединены с вторым и третьим входами интерполятора, шестой выход формирователя, опорных сигналов является вторым выходом устройства.

2. Устройство по п,.1, отличающееся тем, что формирователь опорных сигналов выполнен на триггере, регистре, счетчиках, генераторе импульсов, формирователе импульсов, элементах И, элементах ИЛИ, элементах задержки и блоке сравнения, выход которого соединен через первый элемент задержки с первыми вход аьт первого и второго счетчиков, через- второй элемент задержки - с первым входом первого элемента ИЛИ и непосредственно с первьм входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход второго элемента ИЛИ через формирователь импульсов соединен с первым входом триггера, второй вход которого соединен с выходом тр-етьего элемента задержки, выход триггера соединен с первым входом второго элемента И, второй вход которого подключен к выходу генератора импульсов, выход второго элемента И соединен с

вторым входом второго счетчика, выход которого соединен с первым входом блока сравнения, второй вход которого соединен с выходом регистра, первый выход первого счетчика соединен с вторым входом первого элемента И, второй выход первого счетчика соединен непосредственно с первым входом регистра и входом третьего элемента задержки и через четвертый элемент задержки с вторым входом первого элемента ИЛИ, объединенные вторые входы первого счетчика и регистра и второй вход второго элемента ИЛИ являются соответственно первым и вто- рьм входами формирователя опорных сигналов, выход второго счетчика, третий и второй выходы первого счетчика, выход второго И, выход первого элемента ИЛИ и выход второго элемента ИЛИ являются соответ1 - 1.1

етвенно первым - шестым выходами формирователя onopifbix сигналов.

3. Устройство по п. 1, о т л н- чающееся тем, что арифметический блок выполнен на сумматорах и группах умножителей, выходы которых соединены с соответствующими входами соответствующих сумматоров, выходы которых являются соответствующи} бл.11,

фиг.З

t{J4714

ми выходами арифметического блока, первые входы одноименных умножителей каждой группы объединены и являются соответствующими первыми информационными входами арифметического блока, вторые входы всех умножителей объединены и являются вторым информационным входом арифметического блока.

Кб/tM .20

Кбл.б

т

отсчёта / сигнала

Составитель Н.Бочарова Редактор А.Лежнина Техред И.Попович Корректор И.Муска

Заказ 2967/53 Тираж 543Подписное

БНШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная,-4

- разряду О бл.Зо - Кразряду О бл. 3f

I К разряду О бл Jy

К разряду 15лЭ

и разряду .3о

разряду / бл. 3f

Je I

Нразряду R и. J/y

Фи2.В

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство передачи данных с временным уплотнением каналов | 1978 |

|

SU758540A1 |

| Адаптивный цифровой декоррелятор | 1984 |

|

SU1234989A1 |

| Процессор аппроксимационной обработки информации | 1988 |

|

SU1501089A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И УСТРАНЕНИЯ АНОМАЛЬНЫХ ИЗМЕРЕНИЙ | 2005 |

|

RU2301445C1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И УСТРАНЕНИЯ АНОМАЛЬНЫХ ИЗМЕРЕНИЙ ПРИ ФИКСИРОВАННОМ ЗНАЧЕНИИ ВЕРОЯТНОСТИ ЛОЖНОЙ ТРЕВОГИ | 2007 |

|

RU2361268C1 |

| Устройство для контроля системы автоматической стабилизации параметров | 1986 |

|

SU1374248A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И УСТРАНЕНИЯ АНОМАЛЬНЫХ ИЗМЕРЕНИЙ | 2016 |

|

RU2616568C1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU942034A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1981 |

|

SU955164A1 |

Изобретение относится к области вычислительной техники и может применяться в информационно-измерительных системах для сокращения объема накапливаемой информации. Цель изобретения - повышение информативности . устройства путем увеличения коэффициента сжатия - достигается за счет аппроксимац1ш обрабатываемого сигнала полиномами вплоть до (К-1)-й степени , где N - максимальная степень полинома, описывающего поведение обрабатываемого сигнала на интервале аппроксимации. Устройство содержит коммутаторы 1, 4, регистр 28, формирователь 2 опорных сигналов, ариф- мет1-гческие блоки 11, 12, блок 10 ключей, интерполятор 13, множитель 5, сумматор 6, преобразователь 7, кода, блок 8 сравнения. 2 з.п, ф-лы. 6 ил. (Л оо ю 4 О 4i Фаг I

| Устройство для сжатия информации | 1978 |

|

SU780019A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Авторское свидетельство СССР № 1146708, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1987-07-15—Публикация

1986-01-20—Подача