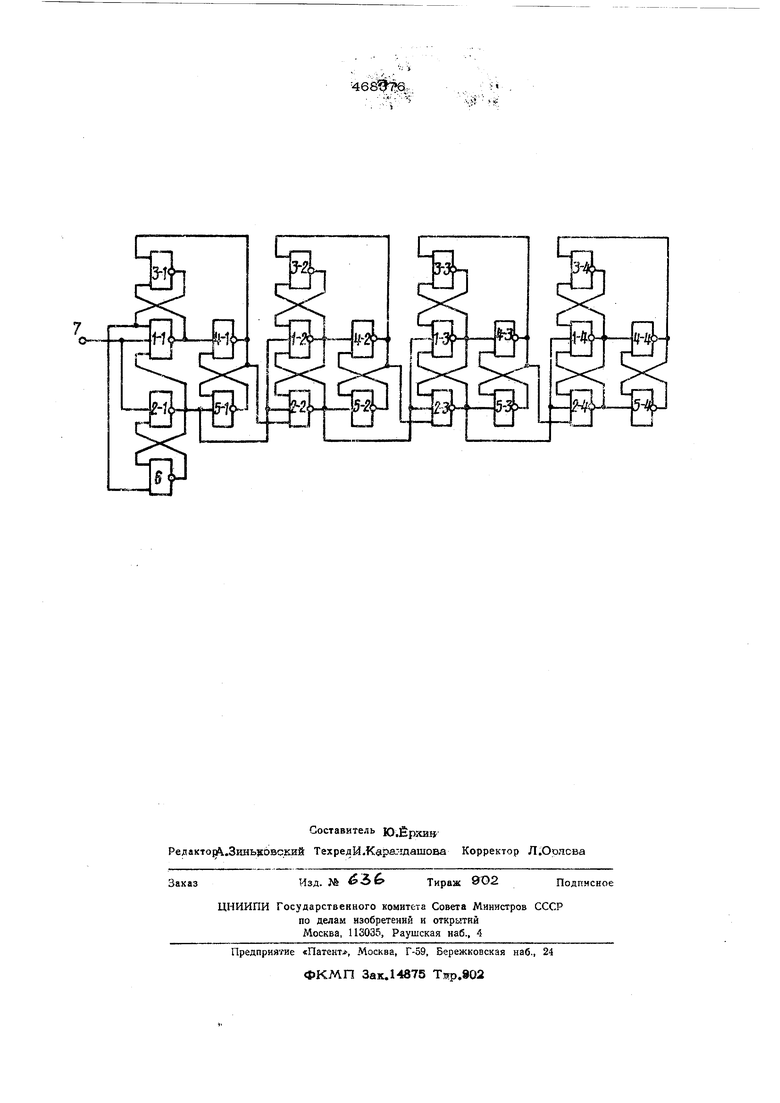

(54) ДВОИЧНЫЙ ДЕЛИТЕЛЬ ИМПУЛЬССВ двухтактноыф.-триггере с перекрывающимися тактами, состоящем из асинхронного информационного триггера на элементах 4-2 - 4-4, 5-2 - 5-4 и трех элементов И - НЕ 1-2 - 1-4, 2-2 - 2-4 и 3-2 3-4, объединенных триггерными связями соответственно. ; Вход 7 является входом устройства. Двоичный делитель импульсов работает следующим образом. Допустим, что перед началом подачи положительных импульсов на вход 7 все четы ре разряда делителя находились в одном из произвольных состояний с высоким потенциалом на выходах элементов 1-1, 2-1, 3-1, 5-1, 1-2, 4-2, 1-3, 3-3, 5-3, 2-4, 3-4, 5-4, низким потенциалом на выходах элементов 4-1, 6, 3-2. 5-2, 2-3, 4-3, 4-4. При приходе на вход 7 положительного импульса на выходе элемента 1-1 появится отрицательный импульс, который перебросит информационный триггер на элементах 4-1 и 5-1 в состояние с высоким потенциалом :на выходе элемента 4-1 и низким на выходе элемента 5-1. Кроме того, этот же отри цательный импульс поддерживает положительный потенциал на выходе элемента 3-1 во время действия положительного импульса а входе 7. При окончании положительного импульса на входе 7 на выходе элементов 1-1 и 2-1 будут высокие потенциалы, которые не влияют на состояние информационного триггера первого разряда. В то же время на все входы элемента 3-1 поступают положительные потенциалы и на его выходе появится отрицательный потенциал, который поступает на вход элемента 6, на выходе которого появляется положительный потенциал. При приходе второго положительного импульса на вход 7 на всех входах элемента 2-1 будут положительные потенциалы, поэтому на его выходе появится отрицатель ный потенциал, что переключает информационный триггер первого разряда в противоположное состО5Шие с высоким потенциалом на выходе элемента 4-1. Отрицательный потенциал с выхода элемента 4-1 поступает на вход элемента 3-1 и переключает его в состояние с высоким потенциалом на выходе. По окончании второго импульса на входе 7 на выходах элементов 2-1 и 3-1 будут положительные потенциалы, что прнве-i аеу- к появлению на выходе элемента 6 отрицательного потенциала. При приходе третьего и четвертого импульса на вход 7 порядок переключения элементов аналогичен тому, который был при приходе первого и второго импульсов соответственно. Таким образом, на выходе элемента 4-1 в первом разряде будут появляться положительные импульсы, сдвин -гые относительно положительных импульсов на выходеэлемента 2-1. Эти положительные импульсы будут поступать на входы элементов 2-1 и 2-2 второго разряда, который будет переключаться с частотой, в два раза меньщей, чем частота переключения первого раз;ряда. i На выходе элемента 2-2 появится низкий потенциал, который переключит триггер второго разряда в противоположное состояние с высоким потенциалом на выходе элемента 5-2 и низким потенциалом на выходе элемента 4-2. I На выходе элемента 2-1 первого разряда в этот момент появляется положительный (потенциал, который вызовет на выходе 1-2 второго разряда отрицательный |потенциал, так как на всех входах элемен- та 1-2 в данный момент действуют положительные потенциалы. Низкий потенциал на вькоде элемента ,1-2 переключит информационный триггер iBTOporo разряда в противоположное состояние с высоким потенциалом на выходе simмента 4-2 и низким потенциалом на выхо де элемента 5-2. Далее,на выходе элемента 2-1 появляет ся следующий положительный потенциал, не : i переключения элемента 1-2 от него не проИзойдет, так как на его входе действует отрицательный потенциал с выхода элемента 3-2. Далее пО5Шляется положительный потенциал на выходе элемента 4-1, который поступает на вход элемента 2-2. На всех : входах элемента 2-1 в этот момент деиствуют положительные потенциалы, и на его выходе появляется отрицательный потенциал, который переключит информационный триггер BTqpcro разряда в положение с высоким потенциалом на выходе элемента 5-2 и низким потенциалом элемента 4-2. Дальнейшие положительные импульсы, которые будут появляться на выходах элементов 2-1 и 4-1, будут аналогичным образом переключать информационный триггер второго разряда на элементах 4-2 и 5-2.

На выходах элементов 2-2 и 4-2 второго разряда при работе делителя также действуют положительные импульсы, причем импульсы на выходе элемента 2-2 опережают им11ульсы на выходе элемента 4-2.

Положителы ые импульсы с вькодов элементов 2-2 и 4-2 второго разряда делителя подаются на входы элементов 1-3 и 2-3 третьего разряда дегштеля. Условие переключения результирующего положительн ого потенциала на всех выходах элемен- та 1-3 lio сравнению с потенциалами, прихо-дяидами на вход элемента 2-3, выполняется. Поэтому третий разряд также будет переключаться, но с частотой в два раза меньшей чем частота импульсов на его входах, т.е, в два раза меньше частоты переключения триггера второго разряда.

С увеличением числа разрядов делителя скважность импульсов стремится к единице.

Предмет изобретения

1. Двоичный делитель импульсов на потенциальных J. логических элементах И-НЕ ( НЕ), первый разряд которого представляет собой Т-триггер на однотактном -триггере, вьшолненном на трех асинхронных,-g(-триггерах а одном информационном и двух установочных, отличающийся тем, что, с целью упрощения, каждый разряд, начиная со второго, вьшолнен в виде Т-триггера на основе двухтактнго Д-триггера с перекрьтающимися тактами, состоящего из асинхронного/,- информааи онного триггера и трех элементов И - НЕ. (или НЕ), объединенных триггерными связями, выход первого из которых подключен к входу S . а выход второго к входу ft своего информационного

f,- -триггера, один из входов первого и второго элементов каждого разряда соединен с выходом второго элемента предыдущего разряда;а второй вход второго элемента соединен с выходом информационного триггера предыдущего разряда.

2. Делитель поп.1, отличающийся тем, что, с целью получения импульсов со скважностью, близкой к единице, к входам первого и второго элементов каждого разряда, начиная со второго, :подключен нулевой выход информационного триггера предыдущего разряда, а к второму входу второго элемента подключен выход третьего элемента предыдущего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный делитель числа импульсов | 1974 |

|

SU526080A1 |

| Многофазный двоичный делитель | 1971 |

|

SU493032A1 |

| Двоичный делитель импульсов | 1974 |

|

SU657616A1 |

| Устройство для измерения абсолютного отклонения частоты | 1982 |

|

SU1205050A1 |

| @ -Разрядный счетчик с контролем | 1983 |

|

SU1138944A1 |

| Распределитель импульсов | 1977 |

|

SU705683A2 |

| Устройство для контроля работы @ -разрядного счетчика | 1982 |

|

SU1167727A1 |

| ДВОИЧНЫЙ СЧЕТЧИК | 1972 |

|

SU336815A1 |

| Счетчик | 1976 |

|

SU657617A1 |

| Регистр сдвига | 1975 |

|

SU631992A1 |

Авторы

Даты

1975-04-25—Публикация

1972-04-28—Подача