Изобретепне относитея к области вычи4 т11тельно и дискретной те.х,ники и может быть непользовано при построенни ЦВМ и нриборов, требующих дискретного деления частоты и подсчета числа импульсов.

Известен двоичный счетчик на потвициальпых логических элементах «Р1-НЕ/ИЛИ-НЕ, аЖдьп нечетный разряд которого представляет Г-тр.иггер на аднотактном D-триггере, иыполненном на трех .асинхронных / -5-Т-рИггерах (одном информационном и двух установочных).

Однако в известном устройстве большое число элементов (не менее.шести на один разряд счетчика), что усложняет счетчик, понижая надежность его работы.

Цель «зобретен ия - упрощение счетчика.

Достигается это тем, что каждый четный разряд счетчика выполнен .в в,иде Г-тритгера на ДБухта:Ктном Л-триггере с перекрываюЩИШ1СЯ тактами, состо-ящем из асинхронного информационного триггера -и трех элементов «И-НЕ/ИЛИ-НЕ, объединенных триггер.ными связями, выход первого из которых под; лючен ко входу S своего информационного / -5-триггера, к одному его .входу подключен нулевой выход Г-триггера нечетного разряда, соединенного также со входом второго элемента «И-НЕ/ИЛИ.-НЕ, причем выход плеча установочного триггера, противоположного

плечу, связанному со входом S иифор.мационiioro Г-трИгге.ра (каждого нечетно по -разряда, соедннен с другим входом первого элемента «И-НЕ/ЦЛИ-НЕ Г-триггера следующего четного разря.да.

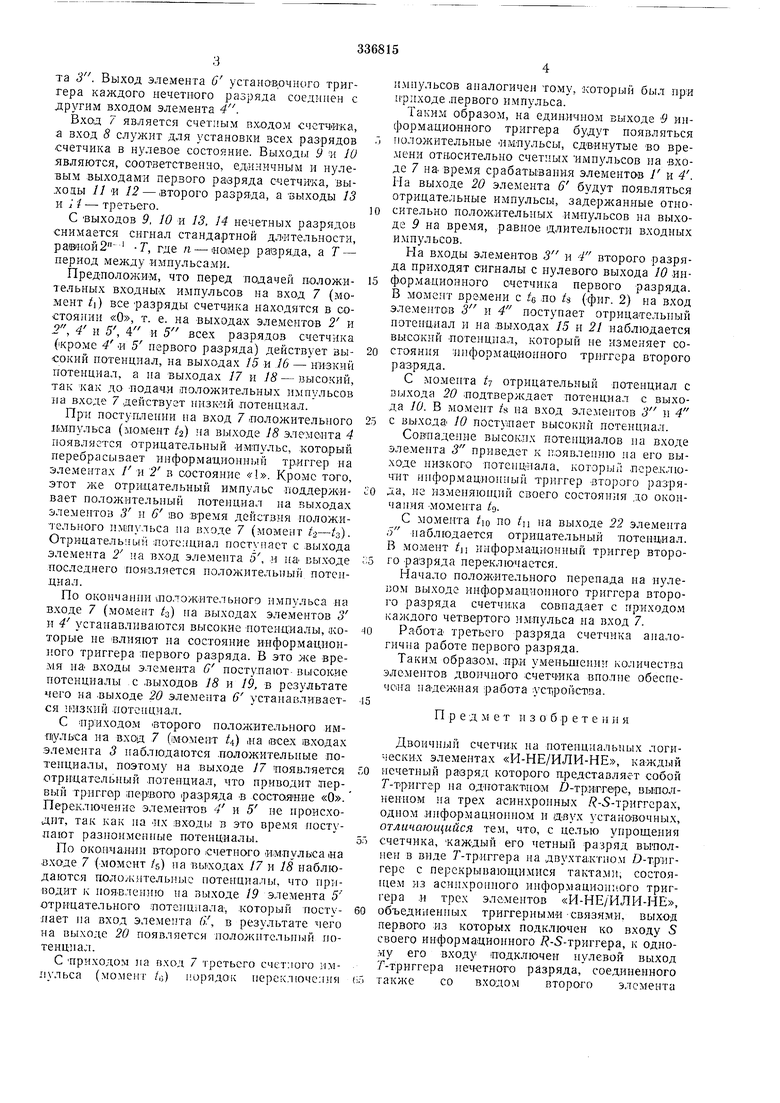

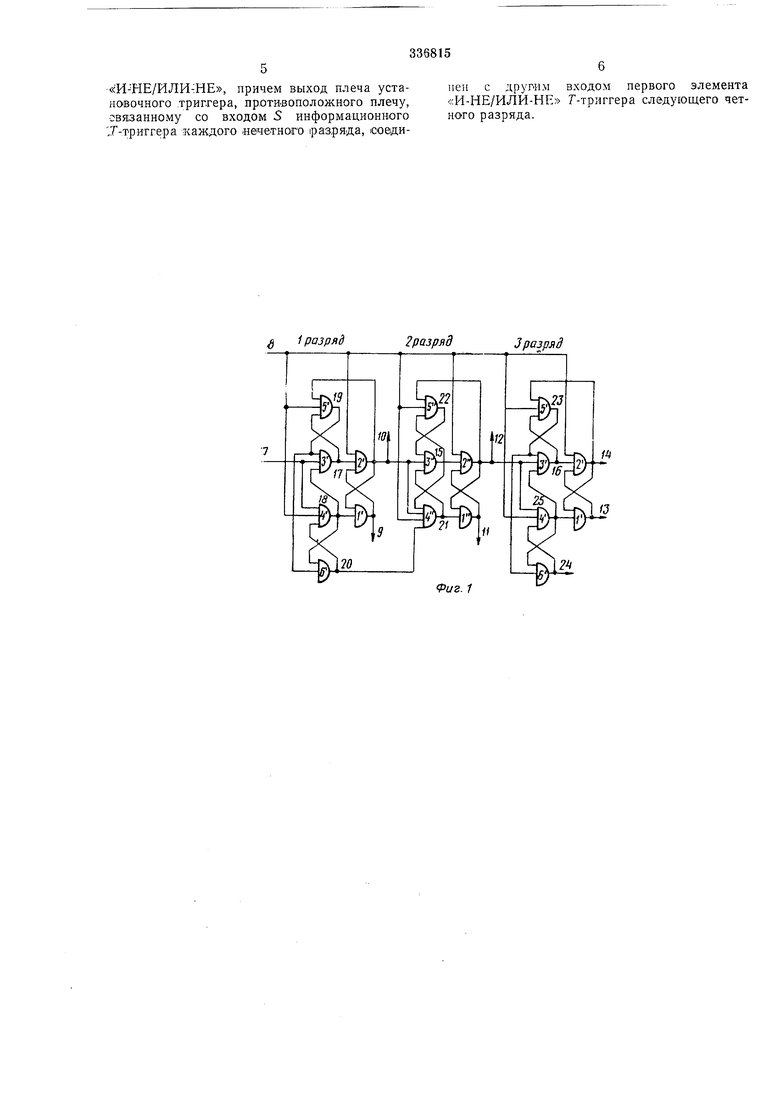

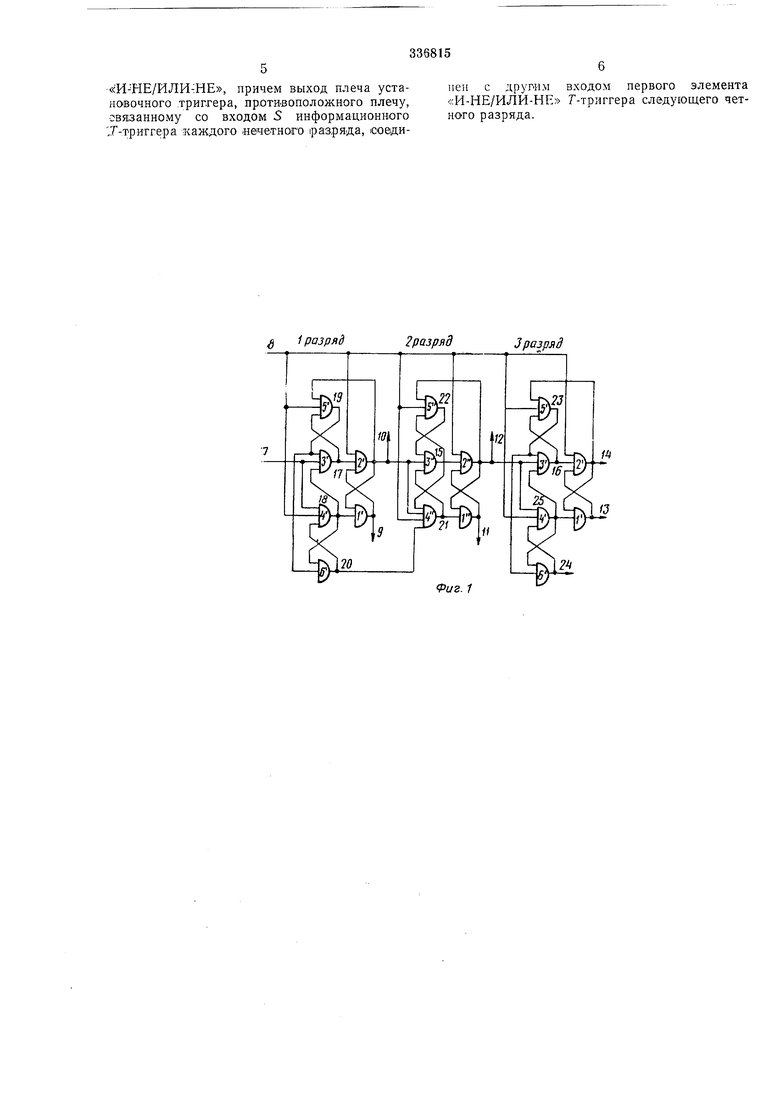

На фиг. 1 представлена при1щипиальная схема устройства, а на фиг. 2 - -- временная диаграмма работы схемы.

Устройство содержит нечетные раз-ряды на .нотенциальных логических элементах /-6 .И-НЕ (-можно «ИЛИ-НЕ), выполненные в виде Г-триггера (триггера со счетны.м входом) на однотактном D-трпггере (триггере с задерж-кой), выполненном на трех асинхронных / -5-триггерах (тр-игге-рах с установочными входами), один из. которых информац:ионный (на элемента1Х 1 и 2) и два установочн1)1Х (на эл-0ментах 3, 5 и 4, 6}.

Четные разряды счетч«ка (элементы 5) выполнены в виде Г-триггера на двухтактном D-триггере с перекрывающимися такта.1-и, Который содержит асинхронный информационный триггер ла элементах /, 2 и.элементы 3, 4 и 5, объединенные триггернымп связями. Выход элемента 4 подключен ко входу S ияфор.мацианиого тригг&ра иа элементах /. и 2, к одному его входу подключен нулевой выход информационного триггера предыдуп1его нечетного разряда (выход элемента 2, соединенного также со входом элемеита 3. Выход элемента 6 установочного триггера каждого нечетного разряда соединен с другим входом элемента 4.

Вход 7 является счетным входом счетчика, а вход 8 служит для установки всех разрядов счетчика в нулевое состояние. Выходы 9 --и 10 являются, соответственно, единичным и нулевым выходами первого разряда счетчика, вы.хояы // и 12 - (Второго разряда, а выходы 13 и It - третьего.

С ВЫХОДОВ 9, 10 и 13. 14 нечетных разрядов снимается сигнал стандартной длительности, рав1ной2 -Т, где л--иоме.р разряда, а Г - период между нмпульсами.

ПредположИМ, что перед подачей положи1ельных входных импульсов на вход 7 (момент t все разряды счетчйка находятся в состоя(ии «О, т. е. на выходах элементов 2 и 2, 4 и 5, 4 и 5 всех разрядов счетчика (|кроме 4« 5 первого разряда) действует высокий потенциал, на выходах 15 и .16 - низкий потенциал, а на выходах 17 и 18 - высокий, так как до Подачл положительных импульсов па входе 7 действует ннзКИй потенциал.

При поступлении па вход 7 .положительного импульса (момент /г) на выходе 18 элемента 4 появляется отрицательный имтульс, который перебрасывает информационный тр.иггер на элементах 1 и 2 в состояние . Кроме того, этот же отрицательный импульс поддерживает положительный потенциал на выходах элементов 3 и 6 iBo время действия положительного импульса па входе 7 (момент /з-4)Отрицатель ый лотсициал поступает с выхода элемента 2 на вход элемента 5, и на выходе последнего поя:зляется положительный потенциал.

По окончании Лоложнтельного импульса на входе 7 (момент 4) на выходах элементов 6 и 4 устанавливаются высокие нотенц:иалы, асоторые не влияют на состояние информационного триггера лервого разряда. В это же время на входы элемента С/ поступают- высокие потенциалы .с .выходов 18 и 19, в результате чего на -выходе 20 элемента 6 устанавливается НИзкий -потенциал.

С Нриходом Второго пололштельного имщуль-са на вход 7 (iMOMetiT /4) ,на всех 1входах элемента 5 наблюдаются л-оложительные потенциалы, поэтому на выходе 17 появляется отрицательный -потенциал, что приводит первый триггер inepiBono разряда в состаяние «О. Переключение элементов --/ и 5 не происходит, так как на ИХ входы в это время ноступают разноименные потенциалы.

По оконча-нии второго сч1етного и.мпульса «а -входе 7 (момент /s) вьгходах 17 и 18 наблюдаются поло/кнтельныс потенциалы, что приводит к появлению на выходе 19 элемента 5 отрицательного -потенциала, который постулает па вход элемента 6-, в результате чего на выходе 20 появляется ноложнтсльный потенциал.

импульсов аналогичен тому, асоторый был при нриходе .первого импульса.

Таким образом, на единичном выходе 9 информацио-нного триггера будут появляться положительные им/пульсы, сдвинутые во времени относительно счетных импзльсов на -входе 7 на время срабатывания элементав / и 4. На выходе 20 элемента 6 будут появляться отрицательные импульсы, задержанные относительно полож-ительных импульсов на выходе 9 на время, равное длительности входных импульсов.

На входы элементов 3 и 4 второго разряда приходят сигналы с нулевого выхода 10 инф-ормационного счетчика первого разряда. В момент вре-мени с 4 ло U (фиг. 2) на вход элементов 3 и 4 поступает отрицательный потенциал и на -выходах 15 н 21 наблюдается высокий Потенцнал, который не изменяет состояния -И1к1)ормаЦИонного триггера второго разряда.

С момента /у отрицательный потенциал с выхода 20 подтверждает потенциал с выхода 10. В момент /8 на вход элементов 3 и 4 с выхода 10 ноступает высокий потенциал.

Совпадение высоких потенциалов на входе элемента 3 приведет к появлению на его выходе низкого потенциала, которыЛ переключит информационный триггер -второго разряда, не нзменяюпхий своего состояния до окончания -момента /оС момента /ю но tn на выходе 22 элемента 5 наблюдается отрицательный потенциал. В момент t информационный триггер второго -разряда переключается.

Начало пололштельного нерепа-да на нулеJ) выход-г информационного триггера второго разряда счетчи.ка совпадает с нриходо.м каждого четвертого импульса на вход 7.

Работа третьего разряда счетчика аналогична работе первого разряда.

Таким образом, яри уменьшении количества элементов двоичного счетчИка вполне обеснсчспга надеж-ная работа устройства.

Пред м е т и з о б р е т е н н я

Двоичньп счетчи-к на потенциальных логических элементах «И-НЕ/ИЛИ-НЕ, каждый нечетный разряд которого представляет собой 7-триггер на однота/кт.нам 1)-тр:игт1ере, выполненном на трех асинхронных / -5-триггсрах, одном инфо-рмацио1П10м и /двух установочных, отличающийся тем, что, с целью упрощения счетчика, каждый его четный разряд выполнен в виде Г-триггера на .двухта;ктном О-триггере с перекрывающимися тактами, состояП1ем из асинхронного информационного триг1ера -И грех элементо-в «И-НЕ/ИЛИ-НЕ, объединенных триггерными -связями, выход первого из которых подключен ко входу 5 своего информационного / -5-триггера, к одному его входу подключен нулевой выход Г-триггера нететного разряда, соединенного также со входом второго элемента

И-Р1Е/ИЛИ-;НЕ, причем выход плеча установочного триггера, противоположного плечу, связанному со входом 5 информационного Т-триггера каждого «ечетного разряда, соедииен с другим входом первого элемента «И-НЕ/ИЛИ-НЕ Г-триггера следующего четного разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный делитель импульсов | 1974 |

|

SU657616A1 |

| Ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией | 1990 |

|

SU1786671A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Оптоэлектронный матричный индикатор напряжения | 1987 |

|

SU1594434A1 |

| Кодирующее устройство | 1987 |

|

SU1481899A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1989 |

|

SU1697583A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Устройство сопряжения интерфейсов разной разрядности | 1989 |

|

SU1689962A1 |

| Устройство для тренировки памяти обучаемого | 1989 |

|

SU1683050A1 |

| Устройство для контроля монотонности кодов | 1988 |

|

SU1575223A1 |

1 разряд

2разряд

Зразряд

Фиг. 1

Авторы

Даты

1972-01-01—Публикация