1

Изобретение относится к автоматике и вычислительной технике. Устройство может быть использовано для преобразования непрерывных сигналов в цифровой код, в информационно-измерительных системах, контролирующих и управляющих системах.

Известен аналого-цифровой преобразователь, который на основе преобразователя поразрядного уравновешивания и цифро-аналогового преобразователя осуществляет адаптивное по интервалу квантование. Известный преобразователь содержит также счетчик, реверсивный счетчик и логическое устройство.

Известный преобразователь осуществляет автоматическое квантование по амплитуде таким образом, что погрешность восстановления функции измеряемого сигнала не превышает заданной погрешности с определенной вероятностью.

Однако в известном преобразователе используются аналоговые узлы для целей адаптивного по времени квантования. Они включены непосредственно в измерительные цепи основного аналого-цифрового преобразователя, осуществляющего кодирование измеряемых сигналов. Следствием этого является увеличение погрещности не только в результате аналого-цифрового преобразования, но и в результате определяемого оптимального интервала квантования, т. е. снижается точность восстановления функции измеряемого сигнала. Известный преобразователь характеризуется также недостаточной надежностью применения значительного количества оборудования для устройств адаптации по сравнению с оборудованием собственно аналого-цифрового преобразователя. Кроме того, при отказе элементов в узлах адаптации происходит полный

отказ преобразователя аналог-код.

В известном устройстве преобразователь аналог-код поразрядного уравновешивания является единым целым со всем устройством. Это не позволяет использовать в таких устройствах преобразователи аналог-код с различными структурами, что сужает возможности применения как известного устройства, так и преобразователей. Целью изобретения является повышение

точности и осуществление адаптивного по времени квантования измеряемого сигнала.

Для этого в преобразователь введены цифровой компаратор, сумматор, регистр памяти кода измеряемого сигнала и регистр памяти

кода интервала квантования, причем выход аналого-цифрового преобразователя соединен с первым входом сумматора, а через регистр памяти кода измеряемого сигнала, сумматор и цифровой компаратор, второй вход которого

подключен к четвертому выходу управляющего устройства, а третий - к выходу устройства, хранящего код заданной погрещности восстановления измеряемого сигнала, к второму входу логического устройства, выход которого соединен с третьим входом сумматора, четвертый и пятый входы которого соединены с соответствующими выходами управляющего устройства, шестой выход которого соединен с вторым входом регистра памяти кода измеряемого сигнала, а седьмой выход - через регистр памяти кода интервала квантования и сумматор - с вторым входом регистра памяти кода интервала квантования.

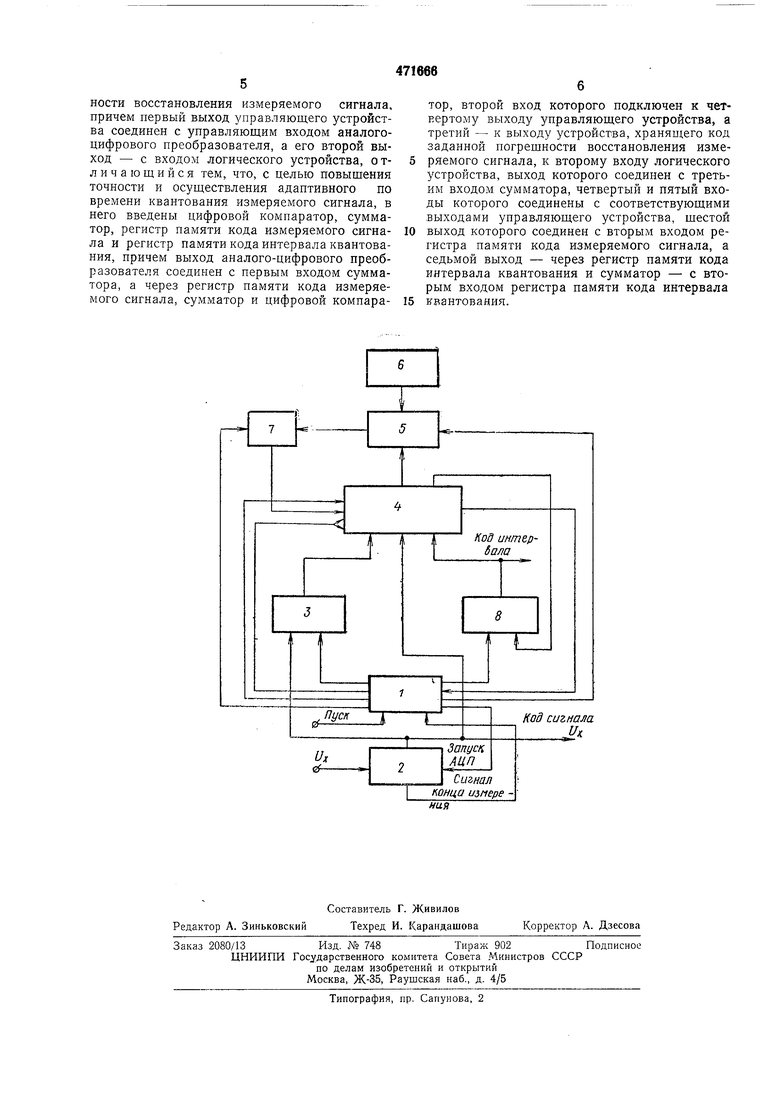

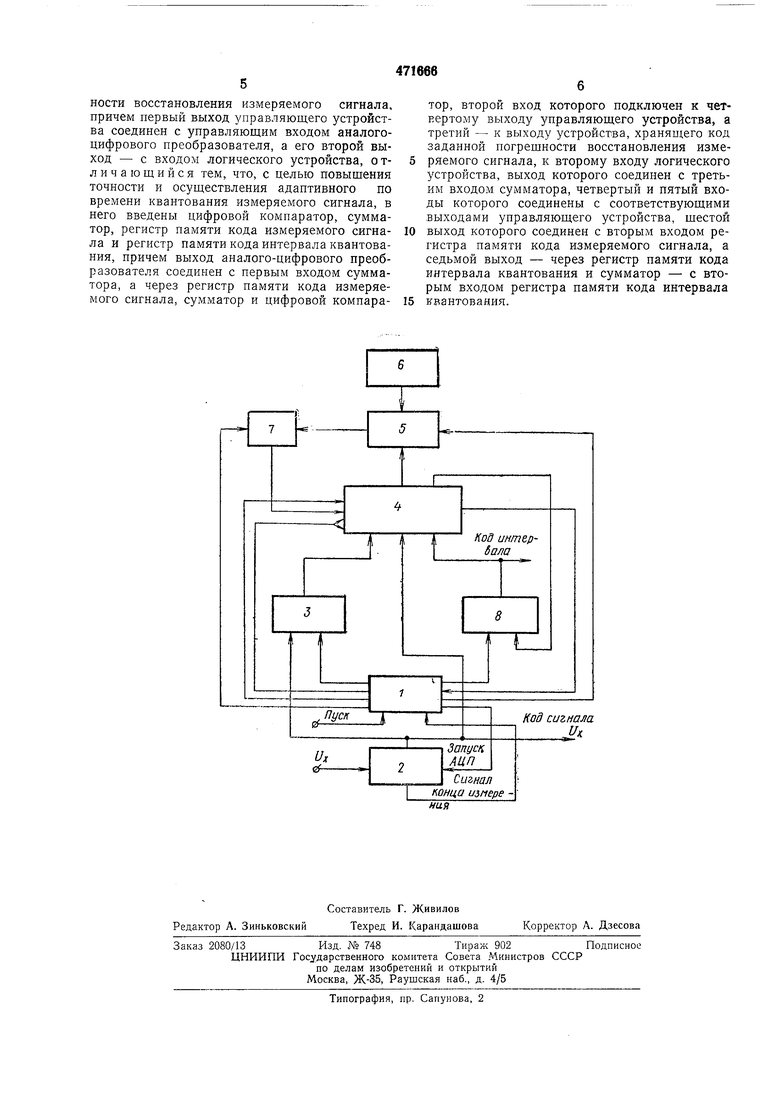

На чертеже приведена структурная схема преобразователя.

Аналого-цифровой преобразователь содержит управляющее устройство 1, которое координирует определенный порядок работы узлов и, в том числе, преобразователя аналог- код 2. Выходной код преобразователя аналог-код 2 подается на регистр памяти кода измеряемого сигнала 3 и сумматор 4. Выходной код сумматора 4 подается на цифровой компаратор 5, управляемый устройством 1. На другой вход цифрового компаратора 5 подается код из устройства 6, храпящего код заданной погрешности восстановления измеряемого сигнала. Результаты сравнения с цифрового компаратора 5 поступают на вход логического устройства 7. С сумматора 4 код интервала квантования в процессе работы преобразователя сначала переписывается в регистр памяти кода интервала квантования 8, а затем снова записывается в сумматор 4 для получения интервала времени в реальном масштабе.

Преобразователь работает следующим образом.

Под действием сигнала «пуск устройство 1 сбрасывает весь аналого-цифровой преобразователь и формирует сигнал «запуск АЦП на управляющий вход преобразователя аналог- код 2. Преобразователь аналог-код 2 измеряет входной сигнал Ux в результате на выходном регистре преобразователя аналог-код 2 устанавливается код измеряемого сигнала, а на управляющем выходе формируется сигнал «конец измерения.

По сигналу от устройства 1 из кода измеряемого сигнала с цифрового выхода преобразователя аналог-код 2 в сумматоре 4 вычитается с учетом знаков код регистра памяти 3. В регистр памяти кода измеряемого сигнала 3 записывается код предыдущего преобразования измеряемого сигнала. После пуска преобразователя код в этом регистре равен нулю, а затем он изменяется на протяжении работы преобразователя. С выхода сумматора 4 снимается модуль разности кодов предыдущего и текущего измерений, который подается на вход цифрового компаратора 5.

Прямой код с выхода сумматора 4, который подается на цифровой компаратор 5, получается в результате управляющего воздействия триггера знака сумматора 4 на устройство, считывающее код сумматора 4.

После окончания формирования кода на выходе сумматора 4 от устройства 1 следует сигнал на цифровой компаратор 5, по которому код, соответствующий изменению входного сигнала с выхода сумматора 4, сравнивается с кодом заданной погрешности восстановления, зафиксированной прямым кодом в

устройстве, хранящем код заданной погрешности восстановления входного сигнала 6.

Результат этого сравнения запоминается логическим устройством 7. Следующим сигналом устройства 1 код с

цифрового выхода преобразователя аналог- код 2 с учетом знака записывается в регистр памяти 3. Кроме того, прямой код интервала квантования с регистра памяти 8 записывается в сумматор 4.

Сигналом от устройства 1, поданным в логическое устройство 7, изменяется код интервала квантования в сумматоре 4 по следующему правилу. В случае, если разность предыдущего и текущего результатов измерений больше заданной погрешности восстановления измеряемого сигнала, интервал квантования уменьшается (код сумматора 4 увеличивается на единицу), если разность меньше - интервал квантования растет (код сумматора 4

уменьшается на единицу).

После изменения кода интервала квантования в сумматоре 4 сигналом от устройства 1 этот код записывается в регистр памяти кода интервала 8, и подается команда на переключение сумматора 4 в режим работы двоичного счетчика. Далее начинается определение интервала квантования путем подачи тактовой частоты от устройства 1 на счетный вход сумматора 4.

По управляющему сигналу с сумматора 4 «конец интервала устройство 1 формирует сигнал «запуск АПП на следующее измерение. При этом код предыдущего измерения сбрасывается, а изложенный порядок опера-.

ций сохраняется.

При первом измерении после сброса с регистра памяти 3 на вход сумматора 4 подается код, соответствующий нулевому значению. С этим кодом сравнивается результат первого

аналого-цифрового преобразования. Следовательно, после первого измерения интервал квантования должен увеличиваться.

В результате ряда измерений входного сигнала, в зависимости от заданной погрешности

восстановления, автоматически устанавливается оптимальный интервал квантования сигнала таким образом, чтобы погрешность восстановления сигнала не превыщала заданной с определенной вероятностью.

ГГА

Предмет изобретения

Аналого-цифровой преобразователь, содержащий преобразователь аналог-код, управляющее устройство, логическое устройство и устройство, хранящее код заданной погрещности восстановления измеряемого сигнала, причем первый выход управляющего устройства соединен с управляющим входом аналогоцифрового преобразователя, а его второй выход - с входом логического устройства, отличающийся тем, что, с целью повыщения точности и осуществления адаптивного по времени квантования измеряемого сигнала, в него введены цифровой компаратор, сумматор, регистр памяти кода измеряемого сигнала и регистр памяти кода интервала квантования, причем выход аналого-цифрового преобразователя соединен с первым входом сумматора, а через регистр памяти кода измеряемого сигнала, сумматор и цифровой компаратор, второй вход которого подключен к четвертому выходу управляющего устройства, а третий - к выходу устройства, хранящего код заданной погрещности восстановления измеряемого сигнала, к второму входу логического устройства, выход которого соединен с третьим входом сумматора, четвертый и пятый входы которого соединены с соответствующими .выходами управляющего устройства, щестой выход которого соединен с вторым входом регистра памяти кода измеряемого сигнала, а седьмой выход - через регистр памяти кода интервала квантования и сумматор - с вторым входом регистра памяти кода интервала квантования.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД | 1972 |

|

SU433634A1 |

| Аналого-цифровой преобразователь | 1973 |

|

SU482006A2 |

| Устройство аналого-цифрового преобразования | 1977 |

|

SU641646A1 |

| Адаптивный коррелометр | 1973 |

|

SU479116A1 |

| Адаптивный коммутатор системы телеизмерений | 1985 |

|

SU1309071A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU942257A1 |

| Устройство для квантования случайного процесса | 1974 |

|

SU516188A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство аналого-цифрового преобразования | 1981 |

|

SU1012435A1 |

| Адаптивный коррелометр | 1976 |

|

SU602952A1 |

ния

Авторы

Даты

1975-05-25—Публикация

1972-09-11—Подача