I

Изобретение относится к цифровой и электроизмерительной технике и может быть использовано в устройстбах аналого-цифрового преобразования, цифровых системах автоматического управления и контроля, информационно-измерительных системах, работающих в условиях аддитивных случайных помех.

С уменьшением уровня измеряемых сигналов все большее влияние на погрешность измерения оказывают помехи. Наиболее эффективным способом подавления помех является интегрирование (аналоговое и цифровое).

Известно устройство аналого-цифрового преобразователя, содержаш,ее преобразователь напряжение - код, динамический регистр, ждущий мультивибратор, счетчик и элементы логики, в котором, с целью повышения точности при работе в условиях помех, осуществляется цифровое интегрирование результатов преобразования 1.

Недостаток этого устройства - низкое быстродействие.

Известен аналого-цифровой преобразователь, содержащий прео(5разователь напряжения в код и устройство адаптации интервала и ошибки интегрирования, устройство .адаптации состоит из цифроаналогового преобразователя приращений, счетчика, реверсивного счетчика, дешифратора, логического элемента И, су лматора-осреднителя, реверсивного счетчика погрешности и включает сравнивающее устройство преобразователя напряжения в код, при этом входы логического элемента И связаны с соответствующими выходами распределителя, дешифратора и счетчика, а выходы - со

входами распределителя и цнфроаналогового преобразователя приращений, выходы последнего связаны со входами сумматора-осреднителя и входоул сравнивающего устройства, младшие разряды основного цифроаналогового преобразователя связаны с выходами сумматора-осреднителя, выход сумматора-осреднителя связан со входом реверсивного счетчика, а выход - с выходом реверсивного счетчика погрешности, входы которого связаны с выходами реверсивного счетчика 2.

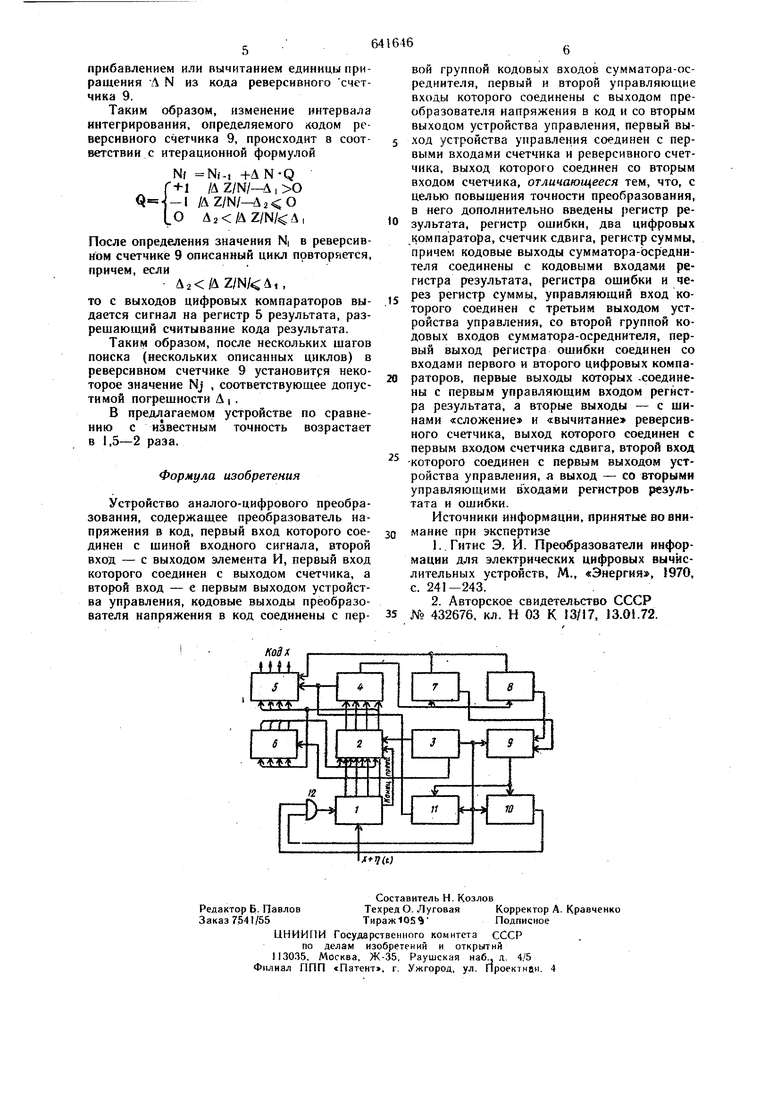

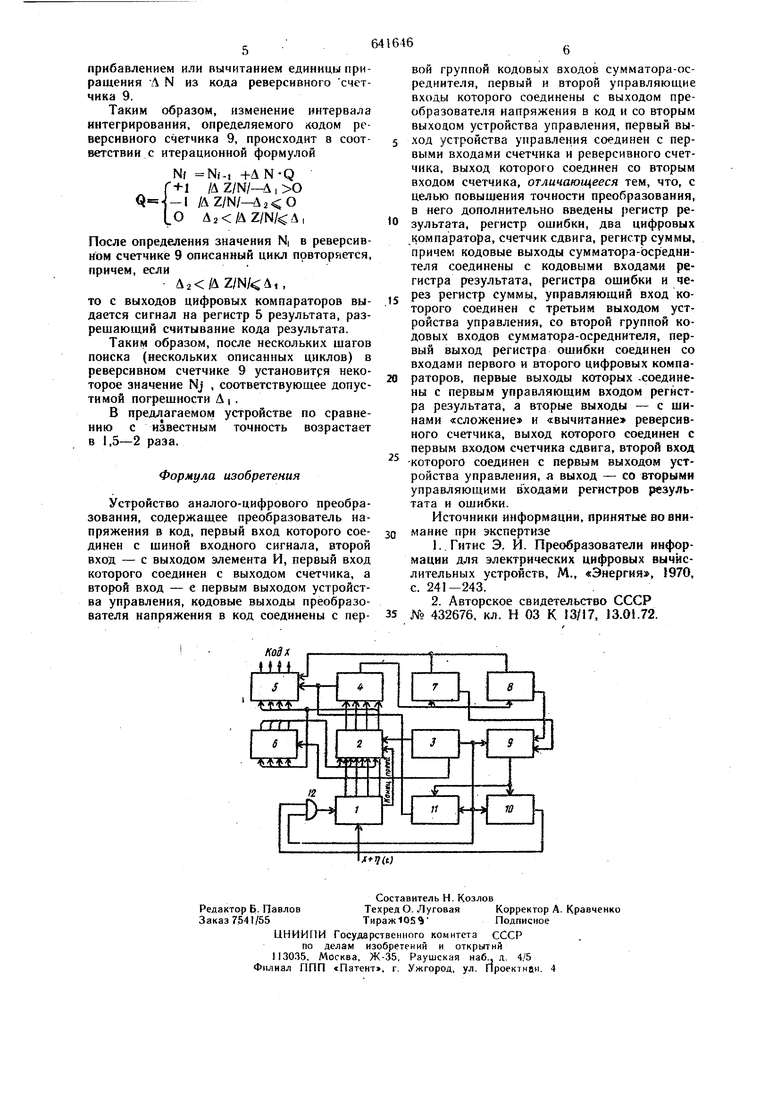

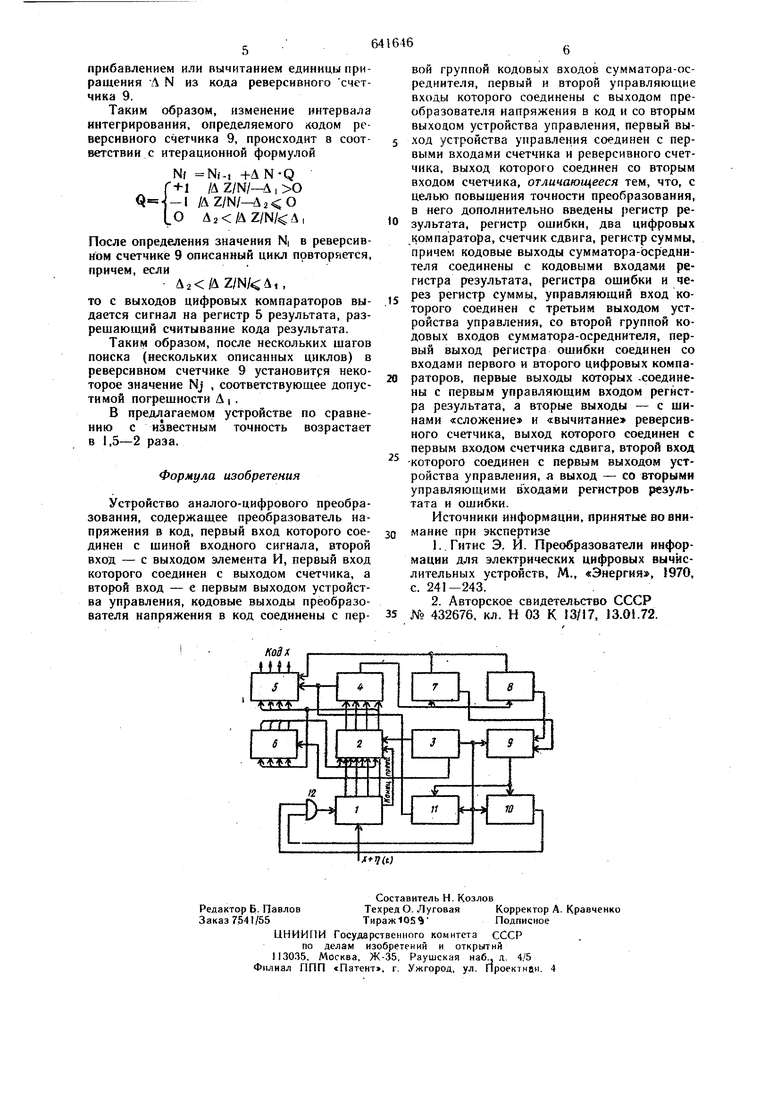

Устройство позволяет изменять интервал интегрирования в зависимости от дисперсии случайных помех по заданной допустимой погрешности, что соответствует п6вышеяию быстродействия и точности преобразования. Наличие в известном устройстве большого количества узлов аналогового типа снижает точность всего устройства в целом. Цель предлагаемого изобретения - повышение точности преобразования. Она достигается тем, что в устройство аналого-цифрового преобразования, содержащее преобразователь напряжения в код, первый вход которого соединен с шиной входного сигнала, второй вход - с выходом элемента И, первый вход которого соединен с выходом счетчика, а второй вход - с первым выходом устройства управления, кодовые выходы преобразователя напряж.ения в код соединены с первой группой кодовых входов сумматора-осреднителя, первый и второй управляющие входы которого соединены с выходом преобразователя напряжения в код и со вторым выходом устройства управления, первый выход устройства управления соединен с первыми вхо.адми счетчика и реверсивного счетчика, выход которого соединен со вторым входом счетчика, дополнительно введены регистр результата, регистр ошибки, два цифровых компаратора, счетчик сдвига, регистр суммы, причем кодовые выходы сумматора-осреднителя соединены с кодовыми входами регистра результата, регистра ошибки и через регистр суммы, управляющий вход которого соединен с третьим выходом устройства управления, со второй группой кодовых входов сумматора-осреднитедя, первый выход регистра ошибки соединен со входами первого и второго цифровых компараторов, первые выходы которых соединены с первым управляющим входом регистра результата, а вторые выходы - с шинами «сложение и «вычитание реверсивного счетчика, выход которого соединен с первым входом счетчика сдвига, второй вход которого соединен с первым выходом устройства управления, а выход - со вторыми управляющими входами регистров результата и ошибки. На чертеже представлена блок-схема предлагаемого устройства аналого-цифрового преобразования. Устройство содержит преобразователь 1 напряжения в код, сумматорОсреднитель.2, устройство 3 управления, регистр 4 ошибки, 5№гистр 5 результата, регистр 6 суммы, цифровые компараторы 7 и 8, реверсивный счетчик 9, счетчик 10, счетчик 11 сдвигов, элемент И 12. При этом выходы устройства 3 управления связаны с соответствующими входами сумматора-осреднителя 2, реверсивного счетчика 9, счетчика Ю, счетчика 11 сдвигов, через элемент И 12 с запускающим входом преобразователя 1 и с управлягощим входом регистра 6 суммы. Кодовые выходы преобразователя через сумматоросоеднитель 2 поступают на входы регистра 5 результата, регистра 6 суммы, а через регистр 4 ошибки на входь цифровых компараторов 7 и 8, выходы которых управляют сложением и вычитанием реверсивного счетчика 9, код которого поступает на счетчик 11 сдвигов и счетчик JO. Управляющий выход счетчика 10 связан со входом элемента И, а счетчик 11 сдвигов - с управляющими входами регистров 5 и 4, на другой управляющий вход регистра 5 поступает сигнал с выходов компараторов 7 и 8, выход регистра 6 связан со входом сумматора-осреднителя 2. Работа устройства осуществляется следующим образом. По сигналу «пуск устройство приводит все регистры в исходное состояние, при котором на реверсивном счетчике 9 записан код числа NO , соответствующий максимальному интервалу интегрирования. Затем по управляющему сигналу с устройства 3 код из реверсивного счетчика 9 переписывается Б счетчик 11 сдвига и счетчик 10, после чего производится NO -кратное преобразование входного сигнала йх+q(i) в преобразователе I по сигналам с устройства 3 управления через элемент И 12, на второй вход элемента И поступает разрешающий потенциал со счетчика 10, задающего число многократных преобразований. При этом может использоваться любой тип преобразователя. Полученные в результате преобразования в преобразователе 1 коды импульсом «конец преобразования переписываются в сумматор-осреднитель 2, где суммируются NO раз, и код суммы считывается в регистр 6 суммы 6 и регистр 5 результата 5. Сумматор 2 при этом освобождается. Затем производится новое NO-кратное преобразование в преоб разователе .1 и суммирование кодов в сумматоре 2, притом одновременно с запуском преобразователя 1 счетчик 11 сдвига осущест1 ляет сдвиг кода в регистре 5 результата, что соответствует делению на число NO и получению среднего результата преобразования. Новое значение суммы результатов преобразования записывается из сумматора- . осреднителя 2 в регистр 5 результата, причем код сумматора 2 сохраняется и из него по сигналу с устройства 3 управления вычитается код, записанный в регистре 6 суммы, разность кодов, равная {U. -f ,(t),-| jUx-f .i(t)l2, (1) переписывается в регистр 4 ошибки. Во время очередного Nj -кратного преобразования код разности Д Z и код результата в регистре 5 сдвигаются с помощью счетчика 11 на No .единиц и полученный осредненный результат из регистра 5 выдается на считывание, а из регистра 4 разность Д Z/NO сравнивается в цифровых компараторах с допустимыми уровнями погрешности от помех Д . В зависимости от положительного или отрицательного решения выходы цифровых компараторов управляют

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

| Устройство аналого-цифрового преобразования | 1989 |

|

SU1647894A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Устройство аналого-цифрового преобразования | 1981 |

|

SU1012435A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU432676A1 |

| Цифровой измеритель максимального давления сгорания в цилиндре двигателя | 1981 |

|

SU1000810A1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1977 |

|

SU660232A1 |

| Адаптивный аналого-цифровой преобразователь | 1974 |

|

SU493911A2 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| РЕВЕРСИВНЫЙ ЧИСЛО-ИМПУЛЬСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2429563C1 |

Авторы

Даты

1979-01-05—Публикация

1977-01-28—Подача