ровкц отключения накоиительлого элемента обеспечивает формированне сигнала смены опорных напряжений на входе интегратора и не нарушает процесс их интегрирования.

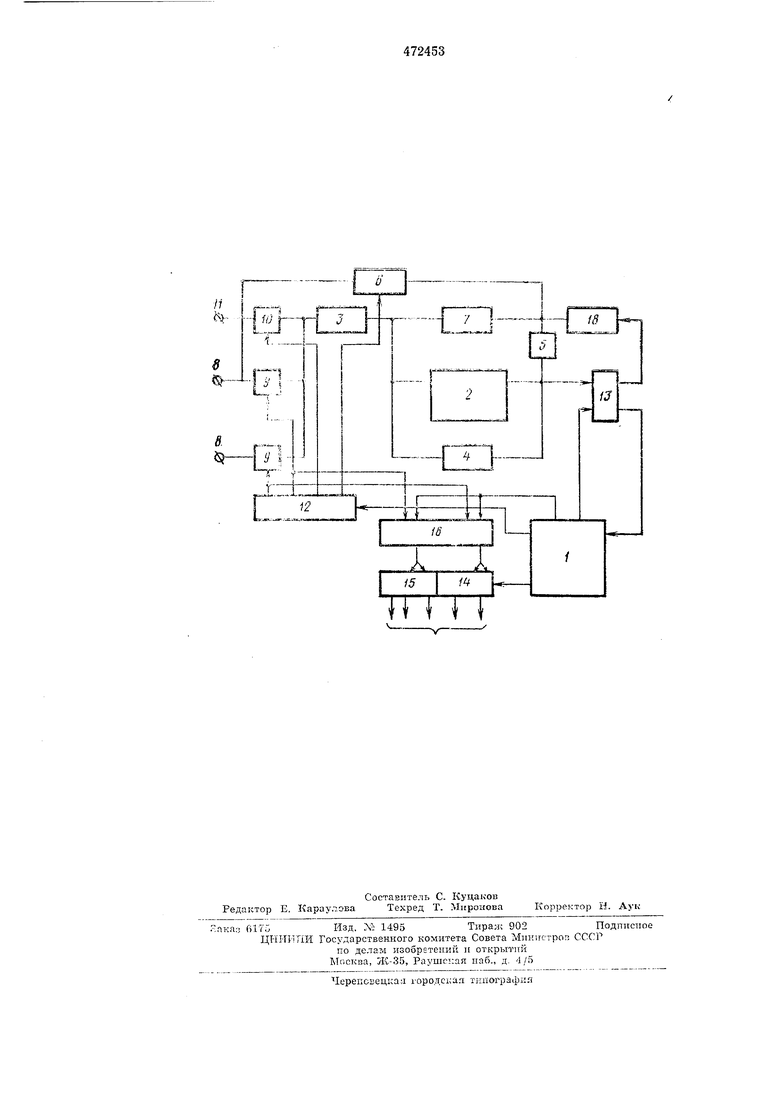

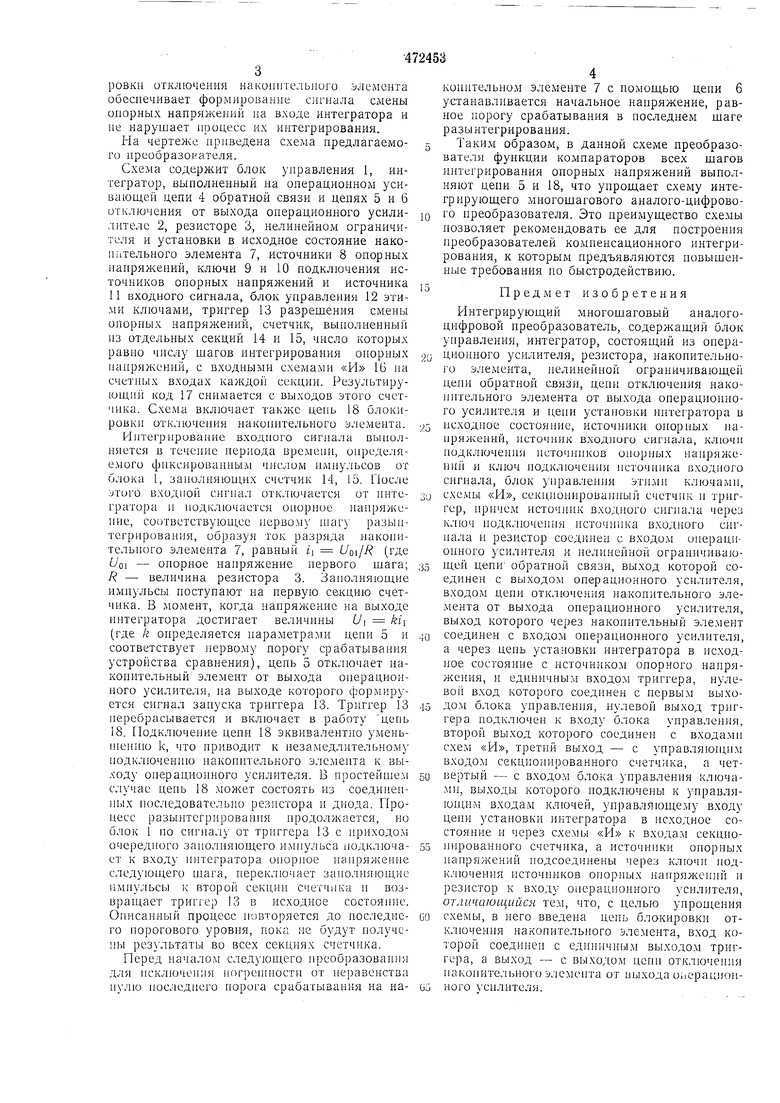

На чертеже приведена схема предлагаемого нреобразорателя.

Схема содерл1ит блок управления 1, интегратор, выполнеиный иа оиерацноином усиваюндей цепи 4 обратной связи и цеиях 5 и 6 отключения от выхода оиерационного усилилителе 2, резисторе 3, нелинейном ограничителя и установки в исходное состояние наконательного элемента 7, источники 8 опорных напряжений, ключи 9 и 10 подключения источников опорных напряжений и источника 11 входного сигнала, блок управления 12 этими ключами, триггер 13 разрешения смены опорных напряжений, счетчик, вынолиенный нз отдельных секций Ни 15, число которых равно числу шагов иптегрирования опорных напряжений, с входными схемами «И 16 на счетных входах каждой секции. Результируюш,нй код 17 снимается с выходов этого счетчпка. Схема включает также цень 18 блокировкн отключения наконительного элемента.

Интегрирование входного сигнала выиолняется в течение периода времени, определяемого фпксирован}1ым числом имнульсов от блока 1, заполияющих счетчик 14, 15. После это1о, входной сигнал отк.почается от ннтегратора II подключается опорное напряжение, соответствующее нерво.му шагу разынтегрировання, образуя ток разряда иаконительного элемента 7, равный /i (где t/oi - онорное напряжение первого шага; R - величина резистора 3. Заполняющие импульсы поступают па первую секцию счетчика. В момент, когда нанряженпе на выходе ннтегратора достигает величины U kii (где /е определяется нараметрами цепи 5 и соответствует первому порогу срабатывання устройства сравнения), цень 5 отключает иакопптельный элемент от выхода онерацнонного усилителя, на выходе которого формируется сигнал запуска триггера 13. Триггер 13 перебрасывается и включает в работу цепь 18. Подключение цепи 18 эквивалентно умень1пенню k, что нриводит к незамедлительно.му подключению пакопптельного элемента к ЕЫходу операционного усилителя. В простейшем случае цепь 18 может состоять пз соединенных носледовательио резистора н диода. Процесс разы}1тегрировапня продолжается, но блок 1 но сигналу от триггера 13 с нриходом очередного заполняющего импульса подключает к входу ннтегратора опорное напряжение следуюнгего шага, переключает заполняющие пмнульсы к второй секцнн счетчика н возвращает триггер 13 в исходное состоящее. Опнсанный процесс иовторяется до носледнего порогового уровня, пока не будут получены результаты во всех секциях счетчика.

Перед началом следующего преобразования для псключеиия иогрепиюсти от неравенства нулю носледпего порога срабатывания на наконительно.м элементе 7 с помощью цепи б устанавливается начальное напряжение, равное порогу срабатывания в последнем шаге разынтегрирования.

Таки.м образом, в данной схеме преобразователя функции компараторов всех шагов интегрирования опорных напряжений выполняют цепи 5 и 18, что упрощает схему интегрирующего многошагового аналого-цифрового преобразователя. Это преимущество схемы позволяет рекомендовать ее для построения нреобразователей компенсационного интегрирования, к которым предъявляются повышенные требования по быстродействию.

Предмет изобретения

Интегрирующий многошаговый аналогоцифровой преобразователь, содержащий блок управления, интегратор, состоящий из операционного усилителя, резистора, накопительного элемента, нелинейной ограничивающей цепи обратпой связи, цепи отключения наконительного элемента от выхода операционного усилителя и цеии устарювки интегратора в исходное состояние, источники опорных напряжений, источник входного сигнала, ключи подключения источинков опорных нанряженнй и ключ подключения нсточника входного сигнала, блок управления .ми ключами, с.кемы «И, сскцнонировапный счстчпк п трпггер, причем псточннк входного снгнала через ключ подключения источника входного сигнала н резистор соединен с входо.м онерацнонного усилителя и нелинейной огранпчнва ощей цепн обратпой связп, выход которой соединен с выходом операционного усилителя, входом цепи отклЕочення накопительного элемента от выхода онерациониого усилителя, выход которого через накопительный элемент соединен с входо.м онерационного усилителя, а через цень установки интегратора в исходное состояние с источником опорного напряжения, и единичным входом триггера, нулеBoii вход которого соединен с нервым выходом блока управленпя, нулевой выход триггера подключен к входу блока управления, второй выход которого соединен с входамн схем «И, третнй выход - с управляющпм входом секционированного счетчика, а четвертый - с входом блока управленпя ключами, выходы которого подключепы к управляющим входам ключей, управляющему входу цепи устаповки интегратора в исходное состояние и через схемы «И к входам секционированного счетчика, а источники опорпых напряжений подсоединены через ключи нодключеиия источников опорных 1анряжений п резистор к входу операцноиного усилителя, отличающийся тем, что, с Г1елью упрощения схе.мы, в него введена цепь блокировки отключения накопительного элемента, вход которой соединен с единичны.м выходом триггера, а выход - с выходом цепи отключения пакопительпого элемента от иыхода олсрацпопного усплптсля.

il I

{ -PL-J.. ... lt.-.--j,

/J

L--LO-- 1

ИТТТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь компенсационного интегрирования | 1974 |

|

SU764126A1 |

| СЧЕТЧИК ЭНЕРГИИ ПОСТОЯННОГО ТОКАВСЕСОЮЗНАЯПАТЕНТНО-][ХНГ:^"КАЯБИБЛИОТЕКА | 1970 |

|

SU283394A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Устройство преобразования сигналаМОСТОВОгО дАТчиКА B чАСТОТу | 1979 |

|

SU839049A1 |

| ДЫМОВОЙ ПОЖАРНЫЙ ИЗВЕЩАТЕЛЬ | 2004 |

|

RU2273886C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО СОГЛАСОВАНИЯ ГЕНЕРАТОРА С НАГРУЗКОЙ | 1996 |

|

RU2110139C1 |

| Цифровой измеритель температуры | 1984 |

|

SU1224609A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU432529A1 |

| Преобразователь напряжения в частоту | 1988 |

|

SU1522407A1 |

Авторы

Даты

1975-05-30—Публикация

1971-12-31—Подача