дополнительных считывающих элементов, вторые входы - соответственно к пятому и шестому выходам логического блока, третьи входы - к выходу первой схемы задержки, а выходы - через схему развязки - к второму входу компаратора.

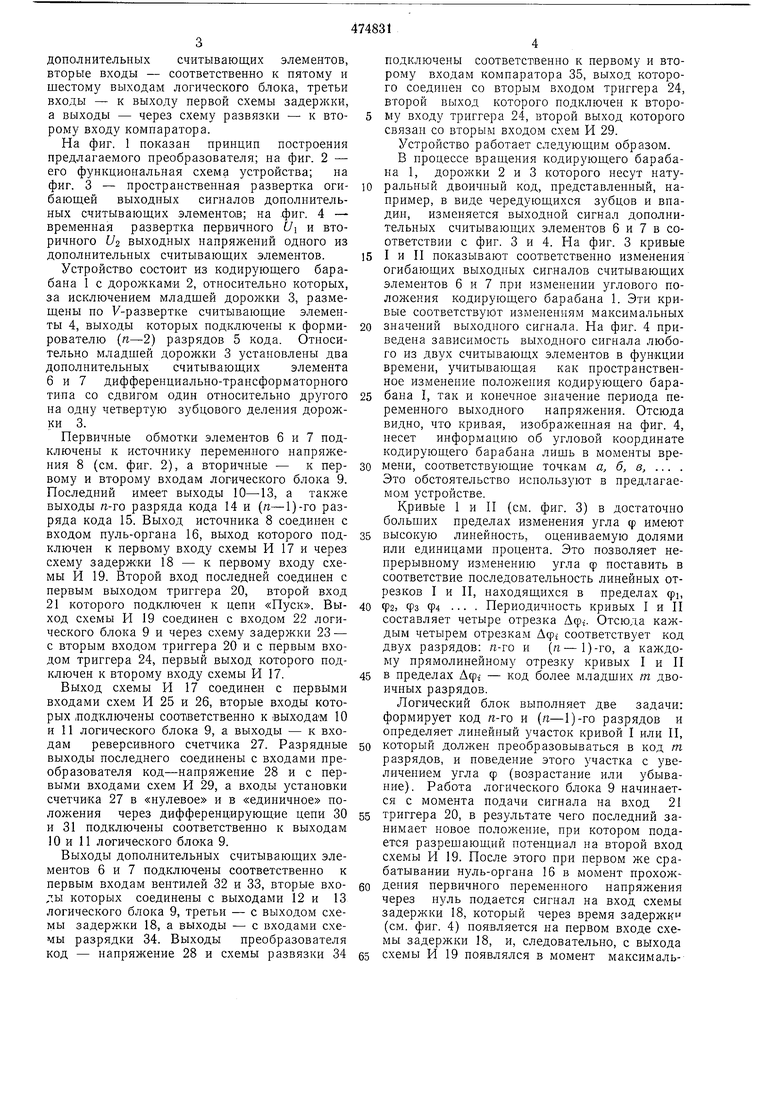

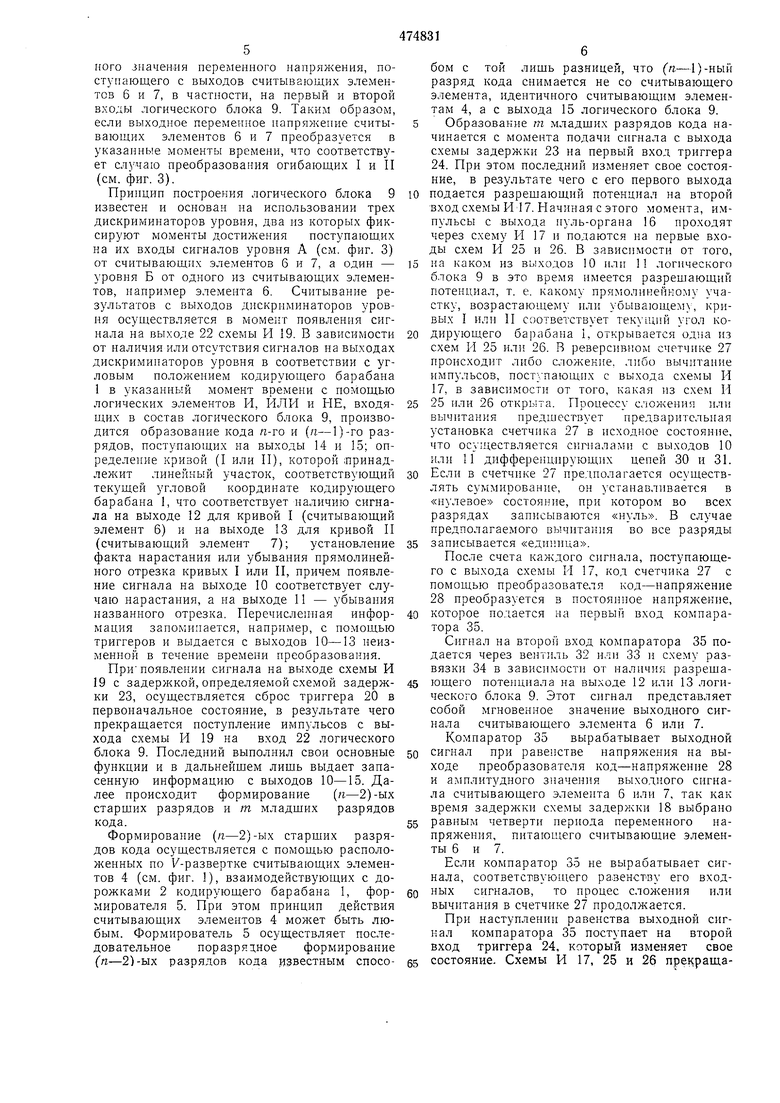

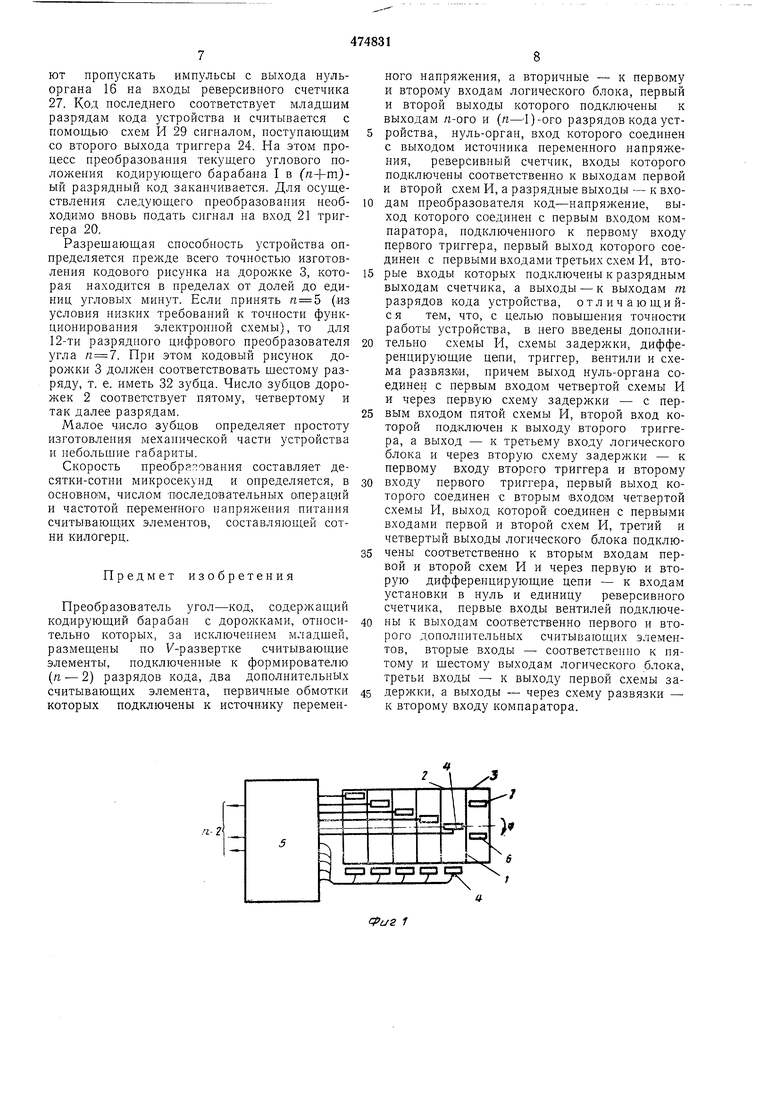

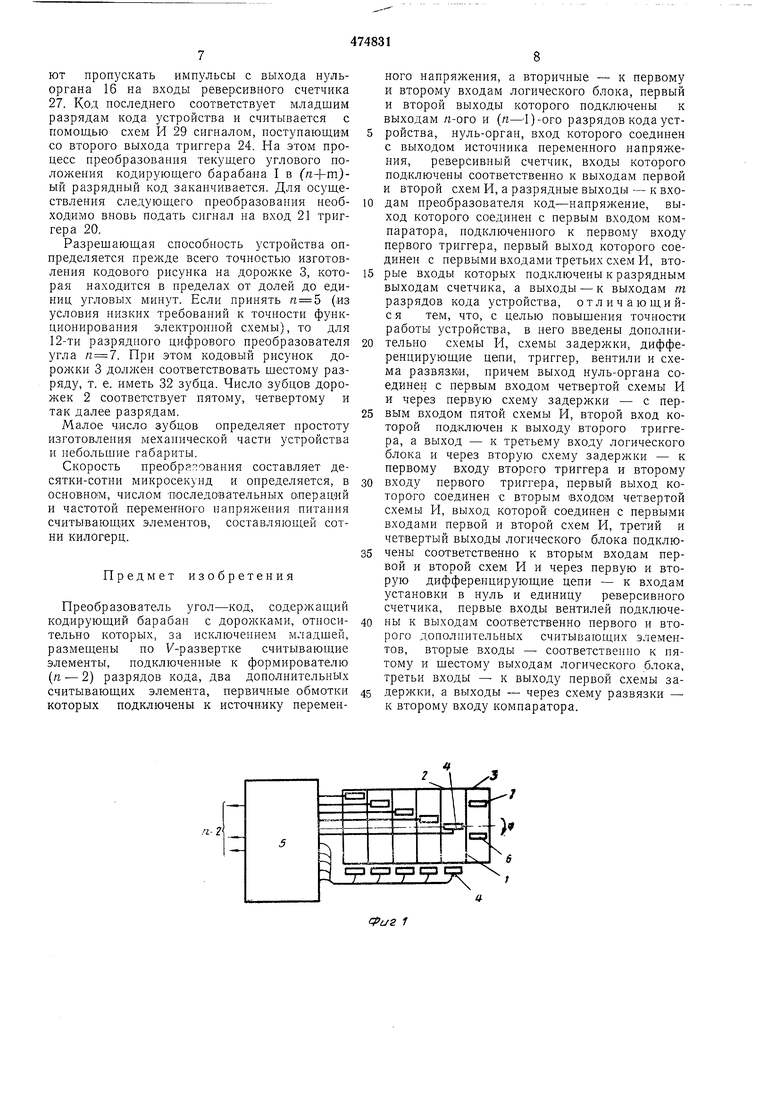

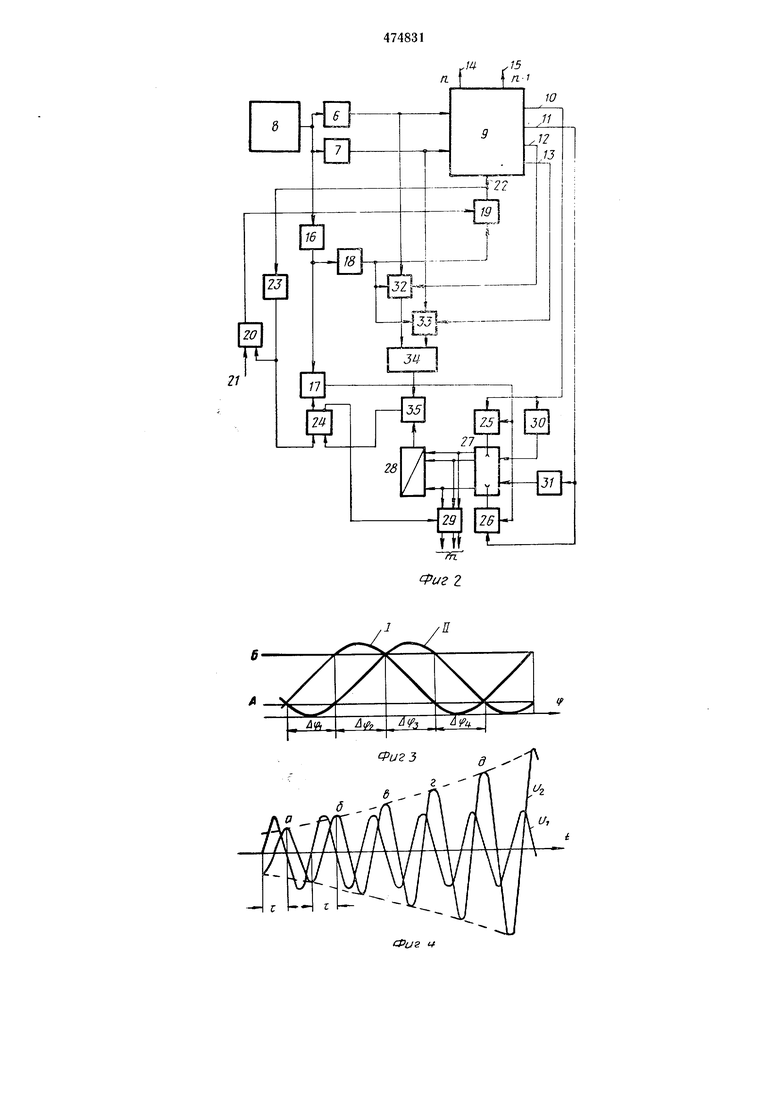

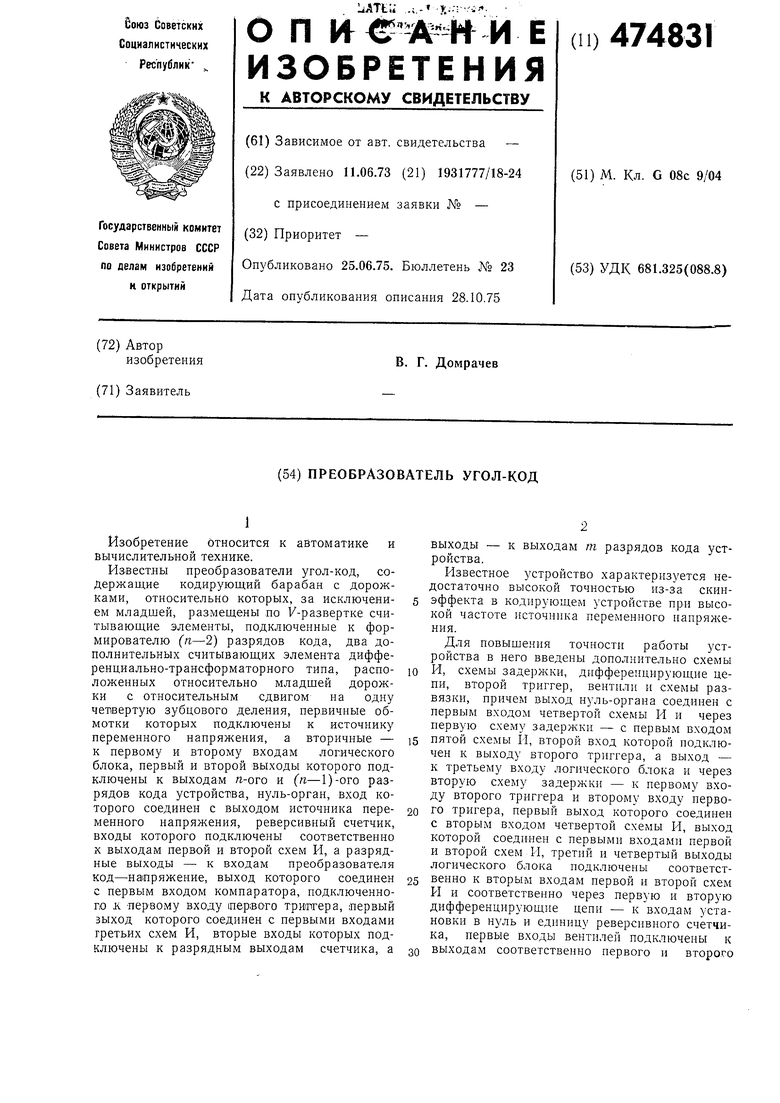

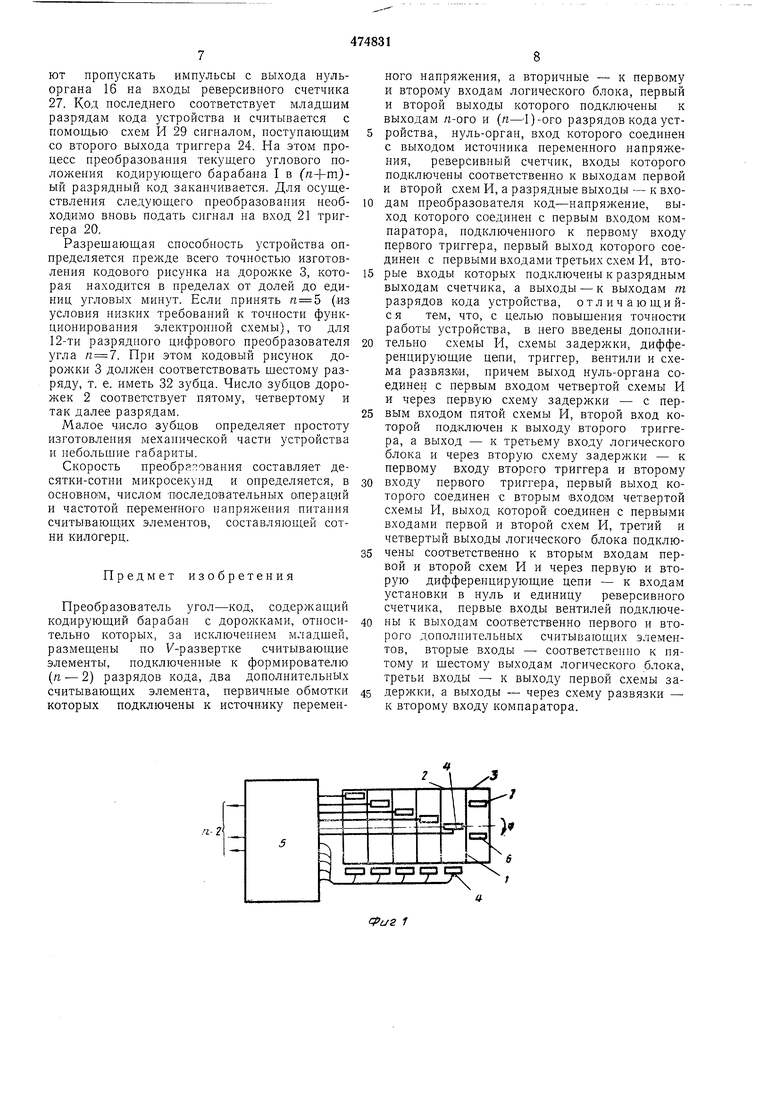

На фиг. 1 показан принцип построения предлагаемого преобразователя; на фиг. 2 - его функциональная схема устройства; на фиг. 3 - пространственная развертка огибающей выходных сигналов дополнительных считывающих элементов; на фиг. 4 - временная развертка первичного f/i и вторичного f/2 выходных напряжений одного из дополнительных считывающих элементов.

Устройство состоит из кодирующего барабана 1 с дорожками 2, относительно которых, за исключением младщей дорожки 3, размещены по У-развертке считывающие элементы 4, выходы которых подключены к формирователю (п-2) разрядов 5 кода. Относительно младшей дорожки 3 установлены два дополнительных считывающих элемента 6 и 7 дифференциально-трансформаторного типа со сдвигом один относительно другого на одну четвертую зубцового деления дорожки 3.

Первичные обмотки элементов 6 и 7 подключены к источнику переменного напряжения 8 (см. фиг. 2), а вторичные - к первому и второму входам логического блока 9. Последний имеет вы.ходы 10-13, а также выходы п-го разряда кода 14 и (п-1)-го разряда кода 15. Выход источника 8 соединен с входом пуль-органа 16, выход которого подключен к первому входу схемы И 17 и через схему задержки 18 - к первому входу схемы И 19. Второй вход последней соединен с первым выходом триггера 20, второй вход 21 которого подключен к цепи «Пуск. Выход схемы И 19 соединен с входом 22 логического блока 9 и через схему задержки 23 - с вторым входом триггера 20 и с первым входом триггера 24, первый выход которого подключен к второму входу схемы И 17.

Выход схемы И 17 соединен с первыми входами схем И 25 и 26, вторые входы которых .подключены соответственно к выходам 10 и 11 логического блока 9, а выходы - к входам реверсивного счетчика 27. Разрядные выходы последнего соединены с входами преобразователя код-напряжение 28 и с первыми входами схем И 29, а входы установки счетчика 27 в «нулевое и в «единичное положения через дифференцирующие цепи 30 и 31 подключены соответственно к выходам 10 и И логического блока 9.

Выходы дополнительных считывающих элементов 6 и 7 подключены соответственно к первым входам вентилей 32 и 33, вторые входы которых соединены с выходами 12 и 13 логического блока 9, третьи - с выходом схемы задержки 18, а выходы - с входами схемы разрядки 34. Выходы преобразователя код - напряжение 28 и схемы развязки 34

подключены соответственно к первому и второму входам компаратора 35, выход которого соединен со вторым входом триггера 24, второй выход которого подключен к второму входу триггера 24, второй выход которого связан со вторым входом схем И 29. Устройство работает следующим образом. В процессе вращения кодирующего барабана 1, дорожки 2 и 3 которого несут натуральный двоичный код, представленный, например, в вихП,е чередующихся зубцов и впадин, изменяется выходной сигнал дополнительных считывающих элементов 6 и 7 в соответствии с фиг. 3 и 4. На фиг. 3 кривые

I и II показывают соответственно изменения огибающих выходных сигналов считывающих элементов 6 и 7 при изменении углового положения кодирующего барабана 1. Эти кривые соответствуют изменениям максимальных

значений выходного сигнала. На фиг. 4 приведена зависимость выходного сигнала любого из двух считывающх элементов в функции времени, учитывающая как пространственное изменение положения кодирующего барабана I, так и конечное значение периода переменного выходного напряжения. Отсюда видно, что кривая, изображенная на фиг. 4, несет информацию об угловой координате кодирующего барабана лишь в моменты времени, соответствующие точкам а, б, в, ... . Это обстоятельство используют в предлагаемом устройстве.

Кривые 1 и II (см. фиг. 3) в достаточно больших пределах изменения угла ф имеют

высокую линейность, оцениваемую долями или единицами процента. Это позволяет непрерывному изменению угла ф поставить в соответствие последовательность линейных отрезков I и П, находящихся в пределах фь

ф2, Фз ф4 .... Периодичность кривых I и II составляет четыре отрезка Дф. Отсюда каждым четырем отрезкам Афг соответствует код двух разрядов: л-го и (п-1)-го, а каждому прямолинейному отрезку кривых I и II

в пределах Аф - код более младших т двоичных разрядов.

Логический блок выполняет две задачи: формирует код п-го и (п-1)-го разрядов и определяет линейный участок кривой I или II,

который должен преобразовываться в код т разрядов, и поведение этого участка с увеличением угла ф (возрастание или убывание). Работа логического блока 9 начинается с момента подачи сигнала на вход 21

триггера 20, в результате чего последний занимает новое положение, при котором подается разрешающий потенциал на второй вход схемы И 19. После этого при первом же срабатывании нуль-органа 16 в момент прохождения первичного переменного напряжения через нуль подается сигнал на вход схемы задержки 18, который через время задержки (см. фиг. 4) появляется на первом входе схемы задержки 18, и, следовательно, с выхода

схемы И 19 появлялся в момент максимального значения переменного напряжения, поступающего с выходов считывающих элементов 6 и 7, в частности, на первый и второй входы логического блока 9. Таким образом, если выходное переменное напряжение считывающих элементов 6 и 7 преобразуется в указанные моменты времени, что соответствует случаю преобразования огибающих I и П (см. фиг. 3).

Принцип построения логического блока 9 известен и основан на иснользовании трех дискримииаторов уровня, два из которых фиксируют моменты достижения поступающ,их на их входы сигналов уровня А (см. фиг. 3) от считывающих элементов 6 и 7, а один - уровня Б от одного из считывающих элементов, например элемента 6. Считыванне результатов с выходов дискрнминаторов уровня осуществляется в момент появления сигнала на выходе 22 схемы И 19. В зависимости от наличия или отсутствия сигналов на выходах дискриминаторов уровня в соответствии с угловым положением кодирующего барабана 1 в указанный момент времени с номощью логических элементов И, ИЛИ и НЕ, входящих в состав логического блока 9, производится образование кода п-то и (п-1)-го разрядов, поступающих на выходы 14 и 15; определение кривой (I или II), которой принадлежит линейный участок, соответствующий текущей угловой координате кодирующего барабана 1, что соответствует наличию сигнала на выходе 12 для кривой I (считывающий элемент 6) и на выходе 13 для кривой II (считывающий элемент 7); установление факта нарастания или убывания прямолинейного отрезка кривых I или II, причем появление сигнала на выходе 10 соответствует случаю нарастания, а на выходе 11 - убывания названного отрезка. Перечисленная информация запоминается, например, с номощью триггеров и выдается с выходов 10-13 неизменной в течение времени преобразования.

Припоявлении сигнала на выходе схемы И 19 с задержкой, определяемой схемой задержки 23, осуществляется сброс триггера 20 в первоначальное состояние, в результате чего прекращается ноступление имиульсов с выхода схемы И 19 на вход 22 логического блока 9. Последний выполнил свои основные функции и в дальнейшем лишь выдает запасенную информацию с выходов 10-15. Далее происходит формирование (п-2)-ых старших разрядов и т младших разрядов кода.

Формирование (п-2)-ых старших разрядов кода осуществляется с помощью расположенных по У-развертке считывающих элементов 4 (см. фиг. 1), взаимодействующих с дорожками 2 кодирующего барабана 1, формирователя 5. При этом принцип действия считывающих элементов 4 может быть любым. Формирователь 5 осуществляет последовательное поразрядное формирование (п-2)-ых разрядов кода известным способом с той лишь разницей, что (п-1)-ный разряд кода снимается не со считывающего элемента, идентичного считывающим элементам 4, а с выхода 15 логического блока 9. Образование т младших разрядов кода начинается с момента подачи сигнала с выхода схемы задержки 23 на первый вход триггера 24. При этом последний изменяет свое состояние, в результате чего с его первого выхода

подается разрещающий потенциал на второй вход схемы И 17. Пачинаясэтого момента, импульсы с выхода нуль-органа 16 проходят через схему PI 17 и подаются на первые входы схем П 25 и 26. В зависимости от того,

на каком из выходов 10 или 11 логического блока 9 в это время имеется разрещающий потенциал, т. е. какому прямолинейному участку, возрастающему или убывающему, кривых I или II соответствует текущий угол кодирующего барабана 1, открывается одна из схем И 25 или 26. В реверсивном счетчике 27 происходит либо сложение, либо вычитание импульсов, поступающих с выхода схемы И 17, в зависимости от того, какая из схем И

25 или 26 открыта. Процессу с.южени; или вычитания предшествует предварительная установка счетчика 27 в исходное состояние, что осуществляется сигналами с выходов 10 или 11 диффере1щирующих цепей 30 и 31.

Если в счетчике 27 предполагается осуществлять суммирование, он устанавливается в «нулевое состояние, при котором во всех разрядах записываются «нуль. В случае предполагаемого вычитания во все разряды

записывается «едишща.

После счета каждого сигнала, поступающего с выхода схемы И 17, код счетчика 27 с помощью преобразователя код-напряжение 28 преобразуется в постоянное напряжение,

которое подается на первый вход компаратора 35.

Сигнал на второй вход компаратора 35 иодается через вентиль 32 или 33 и схему развязки 34 в зависимости от наличия разрешающего поте1щиала на выходе 12 или 13 логического блока 9. Этот сигнал представляет собой мгновенное значение выходного сигнала считывающего элемента 6 или 7. Компаратор 35 вырабатывает выходной

сигнал при равенстве напряжения на выходе преобразователя код-напряжение 28 и амплитудного значения выходного сигнала считывающего элемента 6 или 7, так как время задержки схемы задержки 18 выбрано

равным четверти периода переменного напряжения, питающего считываюндие элементы 6 и 7.

Если компаратор 35 не вырабатывает сигнала, соответствующего равенству его входных сигналов, то процес сложения или вычитания в счетчике 27 продолл ается.

При наступлении равенства выходной сигнал компаратора 35 поступает на второй вход триггера 24, который изменяет свое

состояние. Схемы И 17, 25 и 26 прекращают пропускать импульсы с выхода нульоргана 16 на входы реверсивного счетчика 27. Код последнего соответствует младшим разрядам кода устройства и считывается с помощью схем И 29 сигналом, поступающим со второго выхода триггера 24. На этом процесс преобразования текущего углового положения кодирующего барабана I в (л+гп)ый разрядный код заканчивается. Для осуществления следующего преобразования необходимо вновь подать сигнал на вход 21 триггера 20.

Разрещающая способность устройства оипределяется прежде всего точностью изготовления кодового рисунка иа дорожке 3, которая находится в пределах от долей до единиц угловых минут. Если принять п 5 (из условия низких требований к точности функционирования электроипой схемы), то для 12-ти разрядного цифрового преобразователя угла . При этом кодовый рисунок дорожки 3 должен соответствовать щестому разряду, т. е. иметь 32 зубца. Число зубцов дорожек 2 соответствует пятому, четвертому и так далее разрядам.

Малое число зубцов определяет простоту изготовления механической части устройства и небольшие габариты.

Скорость преобря ования составляет десятки-сотни микросекунд и определяется, в основном, числом Последовательных операций и частотой переменного папряжепия питания считывающих элементов, составляющей сотни килогерц.

Предмет изобретения

Преобразователь угол-код, содержащий кодирующий барабан с дорожками, относительно которых, за исключением младщей, размещены ио У-развертке считывающие элементы, подключенные к формирователю (п - 2) разрядов кода, два дополнительных считывающих элемента, первичные обмотки которых подключены к источнику переменного напряжения, а вторичные - к первому и второму входам логического блока, первый и второй выходы которого подключены к выходам /г-ого и (я-1)-ого разрядов кода устройства, нуль-орган, вход которого соединен с выходом источника иеременного напряжения, реверсивный счетчик, входы которого подключены соответственно к выходам первой и второй схем И, а разрядные выходы - квходам преобразователя код-напряжение, выход которого соединен с первым входом компаратора, подключенного к первому входу первого триггера, первый выход которого соединен с первыми входами третьих схем И, вторые входы которых подключены к разрядным выходам счетчика, а выходы - к выходам т разрядов кода устройства, отличающийс я тем, что, с целью повышения точности работы устройства, в него введены дополнительно схемы И, схемы задержки, дифференцирующие цепи, триггер, вентили и схема развязки, причем выход нуль-органа соединен с первым входом четвертой схемы И и через первую схему задержки - с первым входом пятой схемы И, второй вход которой подключен к выходу второго триггера, а выход - к третьему входу логического блока и через вторую схему задержки - к первому входу второго триггера и второму

входу первого триггера, первый выход которого соединен с вторым входо1м четвертой схемы И, выход которой соединен с иервыми входами первой и второй схем И, третий и четвертый выходы логического блока подключены соответственно к вторым входам первой и второй схем И и через первую и вторую дифференцирующие цепи - к входам установки в нуль и единицу реверсивного счетчика, первые входы вентилей подключены к выходам соответствеино первого и второго дополнительных считывающих элементов, вторые входы - соответственно к пятому и шестому выходам логического блока, третьи входы - к выходу первой схемы задержки, а выходы - через схему развязки - к второму входу компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электромагнитный преобразователь угол-код | 1972 |

|

SU447738A1 |

| Преобразователь угол-код | 1973 |

|

SU447735A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГОЛ—КОД | 1971 |

|

SU423154A1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1228282A1 |

| Преобразователь угол-код | 1973 |

|

SU475648A1 |

| КОДОВОЕ УСТРОЙСТВО | 1992 |

|

RU2015282C1 |

| Устройство для счета предметов,переносимых конвейером | 1982 |

|

SU1072076A1 |

| Устройство для коррекции временных искажений | 1985 |

|

SU1270797A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

п-2

Авторы

Даты

1975-06-25—Публикация

1973-06-11—Подача