3 запоминающе-вычитающего блока 2 импульс, по которому в запоминающе-вычитающем блоке 2 запоминается начальное значение входного сигнала 5(0) и начинается вычитание из поступающего сигнала SCO значения 5(0); запирается выход запоминающе-вычитающего блока 2, и разность S(t}-5(0) не поступает на входы блоков суммирования 3, 4 и первый вход блока деления 7; со второго выхода на вход блока генератора 5 запускающий импульс, и генератор начинает генерировать напряжение UW; с четвертого выхода на второй вход блока выделения минимального значения сигнала 10 для запоминания его запоминающим устройством папряжение с третьего выхода на второй вход блока выделения максимального значения сигнала 9 для запоминания его запоминающим устройством напряжение U Через промежуток времени Дг после начала генерации генератором блока 5 напряжения lJ(t): с первого выхода блока генератора 5 посылается отпирающий импульс на третий вход запоминающе-вычитающего блока 2; со второго выхода блока генератора 5 на вторые входы блоков деления 6, 7 и 8 начинает поступать напряжение U(t); блок управления 13 перестает подавать с четвертого выхода на второй вход блока выделения минимального значения сигнала 10 напряжение f/b с третьего выхода на второй вход блока выделения максимального значения сигнала 9 папряжение U После отпирания запоминающе-вычитающего блока 2 разность S(t)-5(0) поступает на вход блока суммирования 3, где суммируется с отрицательной допустимой погрещностью. С выхода блока суммирования 3 S(t)-5(0)-Е поступает на первый вход блока деления 6. В блоке деления 6 S(t) - 5(0)-е делится на напряжение LJ(t) , подаваемое на второй вход блока деления 6 со второго выхода блока генератора -5. Затем преобразованный сигнал поступает с выхода блока деления 6 на первый вход блока выделения максимального значения 9, который представляет собой диодный элемент в прямом включении, запирающее напряжение которого равно напряжению запоминающего устройства блока 9. Если максимальное зна5(0-S(0)-e чение напряжения сигнала-:- равное sup Г3(0-5(0)больще напряжения ДГ(I ga( запирания, то диодный элемент отпирается и в запоминающее устройство блока 9 занози р 5(0-5(0)- соответственно Д/(1 ga( увеличивается и напряжение запирания, стаS(0-5(0)- г- . За неновясь равным

4 сенное в запоминающее устройство напряжение поступает с выхода блока выделения максимального значения сигнала 9 на второй вход блока сравнения 11; на первый вход блока деления 7, где S(t)-5(0) делится на напряжение U(t) /-е, подаваемое на второй вход блока лтеления 7 со второго выхода блока генератора 5, затем преобразованный сигнал поступает па первый вход блока сравпения // и на второй вход блока сравнения /2; на вход блока суммирования 4, где суммируется с положительной допустимой погрещностью. С выхода блока суммирования 4 S(()-5(0)-fe поступает на первый вход блока деления 8. В блоке деления 8 S(t)5(0)+е делится на напряжение U(t) , подаваемое на второй вход блока деления 8 со второго выхода блока генератора 5. Затем преобразованный сигнал ноступает с выхода блока деления 8 на первый вход блока выделения минимального значения 10, который представляет собой диодный элемент в обратном включении, занирающее напряжение которого равно напряжению запоминающего устройства блока W. Если минимальное зна5 (О - 5 (0) + чение напряжения сигнала inf 5(/)-5(0) + s меньше напряжения запирания, то диодный элемент отпирается и в запоминающее устройство блока inf fS(0-5(0)-bs iO заносится соответ1 - е ственно уменьшается и напряжепие запираinf Г5(0 -5(0) + ния, становясь равным JJ:. Занесенное в запоминающее устройство напряжение поступает с выхода блока выделения минимального значения сигнала 10 на первый вход блока сравнения 12. В блоке сравнения // из 5()- sup Д/ ;:ПI Л1 е поступающего с выхода блока выделения максимального значения сигнала 9, вычитает5(t)-5(0) ся сигнал ,, поступающий на первый вход блока сравнения 11с выхода блока деления 7. Начало выполнения неравенства ,, (f) - 5 (0) - S 5(0-5(0) О sup - 1 свидетельствует о том, что максимальная положительная погрещность равномерного приближения непрерывного входного сигнала S(t) функцией g(t)A{l-е ) стала равной или больше допустимой погрещности, т. е. SM е.

На выходе блока сравнения // в этом случае появляется плюсовое папряжение.

В блоке сравпения 12 из сигнала

S((Q} - епоступающего на второй вход блока сравнения 12 с выхода блока деления 7, вычитается

inf jSJO- + l

поступающее па перi/ / I-е- J вый вход блока сравпения 12 с выхода блока выделения минимального значения сигнала W. Начало выполнения перавепства:

0-S(OM-Si :4(-inf 1 -

1-еА :/

свидетельствует о том, что модуль максимальпой отрицательной погрещпости равномерного приближения непрерывного входного сигнала S(t) функцией q(t)A() стал равным или больще допустимой погрешности, т. е. i - SM I 8.

Нлюсовое папряжение с выхода или блока сравнения //, или блока сравпения 12 поступает

па первый вход блока выборки сигнала /, и на его выходе появляется выбранный отсчет дискретизируемого сигнале;

на вход блока управления 13 и с его второго выхода поступает на вход блока геператора 5 импульс, прекращающий генерацию напряжения U(t) -е и осуществляющий сброс этого напряжения на нуль.

Затем начинается новый цикл дискретизации и все операции повторяются в последовательности, рассмотренной для / 0. Выбор конкретного значения а производится получателем ипформации по априорным сведениям о демпфирующей системе. Напряжение, генерируемое генератором 5, должно соответствовать выбранному значению а.

Предмет изобретения

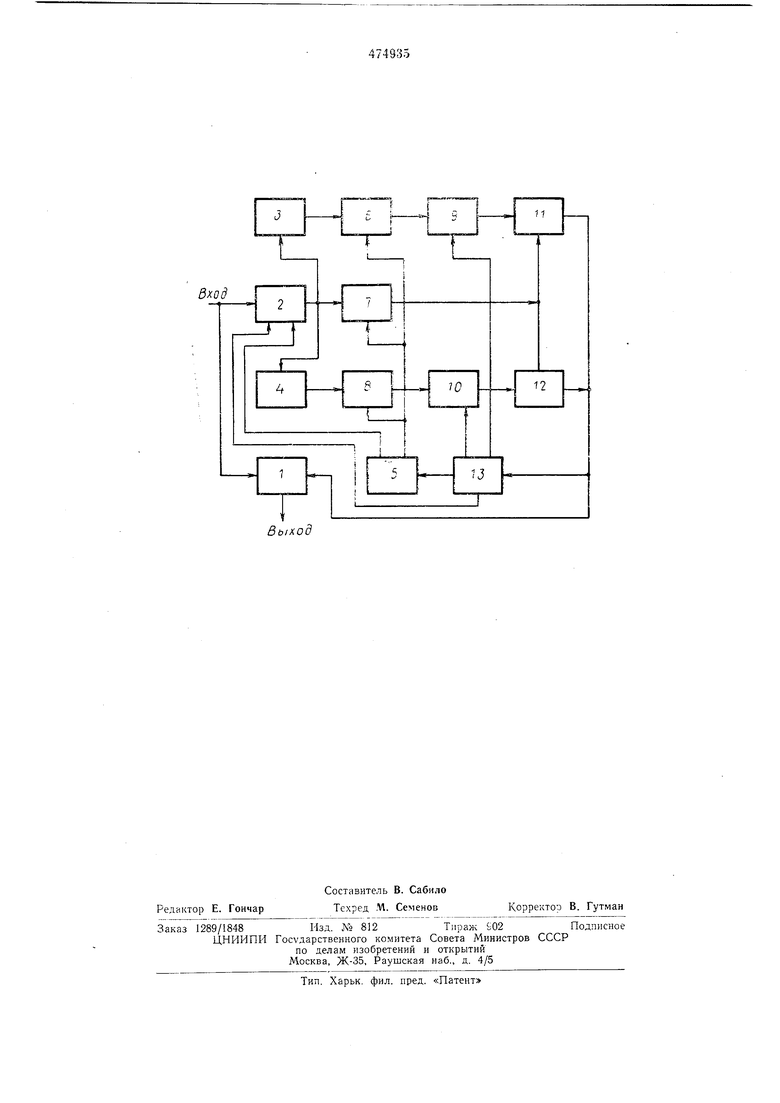

Адаптивный временной дискретизатор, содержащш блок сравнения, выход которого 5 соединен с входом блока управлеппя и с первым входом блока выборки сигнала, второй вход которого соединен с входом дискретизатора, а выход - с выходом дискретизатора, запомпнающе-вычитающий блок, первый вход

0 которого соединен с входом дискретизатора, а второй вход соединен с первым выходом блока управления, отличающийся тем, что, с целью повыщения точности работы адаптивного временного дискретизатора, он содержит

5 два блока суммирования, входы которых соединены с выходом запоминающе-вычитающего блока, генератор функционально-изменяющегося напряжепия, вход которого соединен со вторым выходом блока управления, а пер0 ьый выход соединен с третьим входом запоминающе-вычитающего блока, три блока деления, первый вход первого из которых соединеп с выходом первого блока суммирования, первый вход второго блока деления соединен с выходом запомипающе-вычитающего блока, а выход соединен с первым входом блока сравпения, первый вход третьего блока деления соединен с выходом второго блока суммирования, вторые входы блоков деления соединены со вторым выходом генератора, блок выделения максимального значения, первый вход которого соединен с выходом первого блока деления, второй вход соединен с третьим выходом блока управления, а выход соединен со вторым входом блока сравнения, блок выделения минимального значения, первый вход которого соединен с выходом третьего блока деления, а второй вход соединен с четвертым выходом блока управления,

дополнительный блок сравнения, первый вход которого соединен с выходом блока выделения минимального значения сигнала, второй вход соединен с выходом второго блока деления, а выход соединен с входом блока управления и первым входом блока выборки сигнала.

Вход

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный временной дискретизатор | 1976 |

|

SU577668A1 |

| Адаптивный временной дискретизатор | 1981 |

|

SU1005301A2 |

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 1969 |

|

SU245455A1 |

| Адаптивный временной дискретизатор | 1976 |

|

SU575770A1 |

| Адаптивный временной дискретизатор | 1979 |

|

SU805341A1 |

| Адаптивный временной дискретизатор | 1987 |

|

SU1522242A1 |

| Цифровой панорамный измеритель частоты | 1985 |

|

SU1296955A1 |

| Устройство для определения моментов времени квантования сигнала | 1975 |

|

SU714642A1 |

| Адаптивный временной дискретизатор | 1977 |

|

SU680015A1 |

| Способ измерения среднего значения периодических сигналов | 1985 |

|

SU1296953A1 |

Авторы

Даты

1975-06-25—Публикация

1973-06-11—Подача