I

Устройство относится к области информа ционно-измерительных систем и может быть

использовано во всех случаях, когда необходимо сокращение из1бьггочносги информации.

Из основного авт. свид- N° 456361 известно устройство, содержащее дифференцирующий блок, запоминающе-вычитающий блок состоящий из блока памяти и суммируняцего блока, интегратор и блок сравнения. С выхода дифференцирующего блока напряжение, пропорциональное первой производной входного сигнала подается на запоминающё-вычитающий блок, где происходит запоминание этой производной в точке отсчета и вычисление разности между упомненным значением первой производной и ее текущим значением. Эта разность интегрируется интегратором. Блок сравнения срабатьгеает, если сигнал на выходе интегратора достигает уровня допустимой погрещиостиСл. Овдовремекно с сигналом дискретизации с выхода блока сравнения подаются сигналы сброса на запоминающе-вычитающий блок и интегратор.

Недостатком устройства является малый коэффициент сжатия, так как в нем вычисляется

2

экстраполирующий полином в соответствии с остаточным членом экстраполяционного ряда Тейлора.

Целью изобретения является увеличение коэффициента сжатия информации.

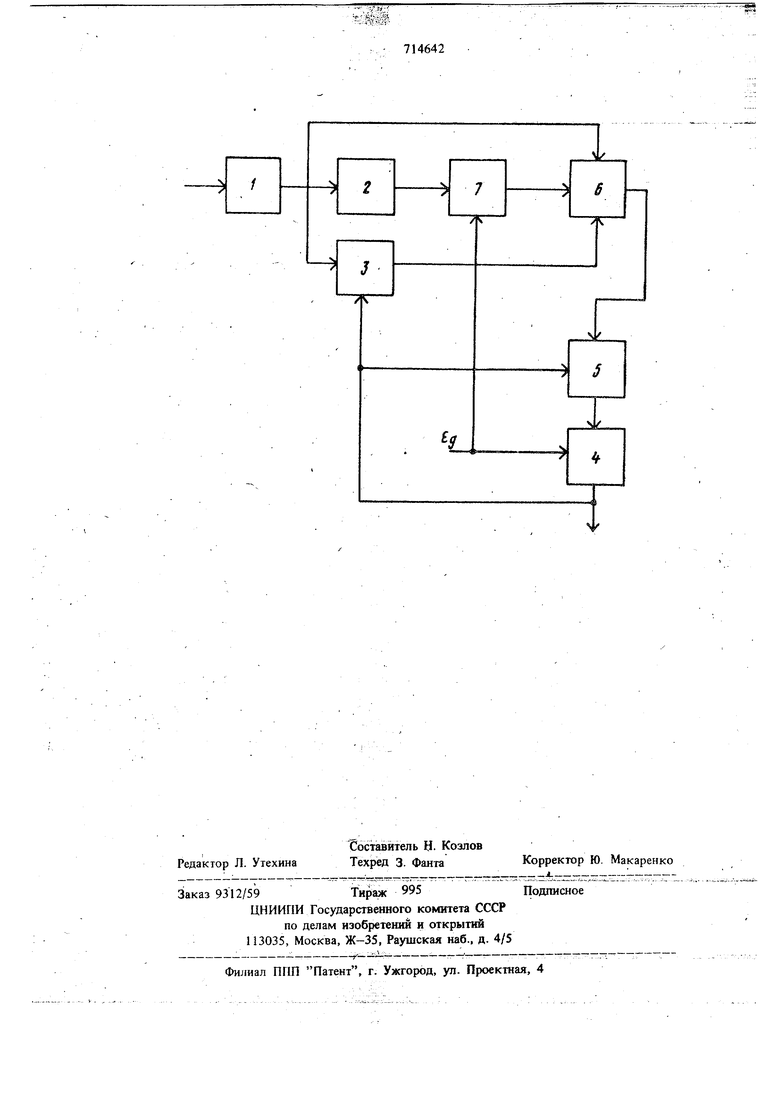

Поставленная цель достигается тем, что в устройство для определения моментов времени квантование сигнала, содержащее основной дифференцирующий блок, выход которого соединен с первыми входами блоков суммирования и запоминания, выход последнего соединенно вторым входом ,блока суммирования, выход которого соединен с первым входом интегратора, второй вход которого подключен ко второму входу блока запоминания и к выходу блока сравнения, вход которого соединен с выходом интегратора, второй вход блока сравнения подключен к щине задания допустимой погрещности аппроксимации, введены дополнительный дифференцирующий блок и функциональный преобразователь. Вход дополнительного дифференцирующего блока соединен с выходом основного дифференцирующего блока, а выход подключен к первому входу функиионального преобразователя, второй вход которого соединен с шиюи задания допусти мой погреишости аппроксимации, а выход - с третьим входом суммирующего лока. Структурная схема устройства приведена на чертеже. Устройство содержит последовательно соединенные основной 1 и дополнительный 2 дифференцирующие блоки, предназначенные для Твычйсления первой и второй производной вход ного сигнала, запоминающий блок 3,одщ вход которого связан с вьвсодом блока 1, а второй - с выходом блока сравнения 4. Блок 3 служит для сравнения выходного сигнала интегратора 5 и сигнала, соответствун)щего заданной погрешности аппроксимации а. и вьщачи сигнала дискретизации. Два входа суммирутоще го .блока 6 соединены со входом и выходом запоминающего блока 3, третий вход - с выхо дом функционального преобразователя 7. а выход - с одним из входов интегратора 5. Интегратор 5 служит для интегрирования напряжения на выходе блока 6, предназначеиного для суммирования сигналов первой производной (выход блока 1), значения первой производной в точке отсчета (выход блока 3) и выходного сигнала преобразователя 7, предназначенного для получения зависимости: . ифп-1,5где x(t) - вторая производная входного сигна ла, (вькод блока 2). Устройство фаботает следующим образом. В момент отсчета интегратор 5 обнуляется, а запоминающий блок $ запоминает значение первой производной )Ш)ЗШёгЬ ШйаЯ|1 йОйен отсчета. Разница между teKyuwM значением первой производной и запомненным значением поступает из суммирующего блока 6 На Интегратор 5 и представляет собой после интегрирования текушее значение погрешности линейной экстраполяции. Для того, чтобы повысить эффективность работы устройстаа,17ё.увеличить коэффициент сжатия, к двум сигналам на входе суммирующего блока 6 добавлен выходной сигнал преобразователя 7, оп рёдёляёмый мгнов енным значением второй производной входного сигнала. Эта добавка подбирается гак, чтобы на строго параболической форме входного сигнала погреишость аппроксимации в момент отсчета совпадала с погрешностью линейной интерполяции. Ра.счеты показьшают, что это произойдет, если функциональный преобразователь реализует приведенную выше зависимость.,Действительно, если входной сигнал имеет на интервале аппроксимации вид / .c{t) at +bt + c, то выходное напря5кение интегратора 5 определяется соотношением U(t) JfS(t)-:(o) + Uфпdt at-l,. Очередной отсчет производится при достиж нии сигналом значения So- При этом|а1р--S/ to С,откуда следуете -0 ..° с« з в ражение, связьгоающее максимальное значение по/грешности линейной интерполяции с величиной модуля - максимума второй производной сигнала (Л/2 2а) и длительностью интервала аппроксимации. Таким образом, устройство для гладких сигналов осуществляют адаптивную временную дискретизацию на основе линейной интерполяции, Что обеспечивает высокую эффективность его работы. Формула изобретения Устройство для определения моментов времени квантования сигнала по авт. свид. № 456361, отличающееся тем, что, с целью увеличения коэффициента сжатия информации, в него введены дополнительный дифференцирующий блок и функциональный преобразователь, причем вход дополнительного дифференцирующего блока соединен с выходом основного дифференцирующего блока, а выход подключен к первому входу функционального преобразователя, второй вход которого соединен с шиной задания допустимой погреишости аппроксимации, а выход - с третьим входом суммирующего блбка.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения моментов времени квантования сигнала | 1986 |

|

SU1325695A2 |

| Адаптивный временной дискретизатор | 1977 |

|

SU680015A1 |

| Устройство для определения моментов времени квантования сигнала | 1980 |

|

SU855991A2 |

| Устройство для определения моментов времени квантования сигналов | 1980 |

|

SU892701A1 |

| Устройство для определения моментов времени квантования сигнала | 1982 |

|

SU1069154A2 |

| Устройство для определения моментов времени квантования | 1976 |

|

SU588625A1 |

| Адаптивный временной дискретизатор | 1976 |

|

SU577668A1 |

| Устройство для определения моментов времени квантования сигнала | 1973 |

|

SU456361A1 |

| Устройство для определения моментов времени квантования сигналов | 1979 |

|

SU782146A1 |

| Адаптивный временной дискретизатор | 1981 |

|

SU1005301A2 |

Авторы

Даты

1980-02-05—Публикация

1975-05-11—Подача