1

Изобретение относится к вычислительной технике и может быть использовано в системах аналого-цифрового преобразования.

По основному авт. св. W 577668 известен адаптивный временной дискретизатор, содержащий первый блок сравнения, запоминаще-вымитающий блок, первый сумматор, блок вычитания, два делителя, блок выделения минимального значения сигнала, генератор пилообразного напряжения, пороговое устройство, блок управления и блок выборки сигнала, первый вход которого .соединен с первым входом запоминающе -вы читающего блока, выход которого соединен с выходом первого сумматора и входом блока вычитания, выход первого сумматора соедр|нен с первым входом первого делителя, выход которого подключен к первому входу блока выделения минимального значения СИ1- нала, выход блока вычитания соединен

с первым входом второго делителя, выход которого подключен к первому входу блока выделения максимального значения сигнала, второй вход которого соединен с выходом блока управления, вторым входом блока выделения, минимального значения сигнала, вторым входом запоминающе-вычитающего блока, первым входом порогового устройства и входом генератора пилооб10разного напряжения, выход блока выделения минимального значения сигнала соединен с первым входом первого блока сравнения, а вторые входы первого и второго делителей соединены

15 с выходом порогового устройства, второй вход которого подключен к выходу генератора пилообразного напряжения, выход блока выделения максимального значения соединен с вторым входом

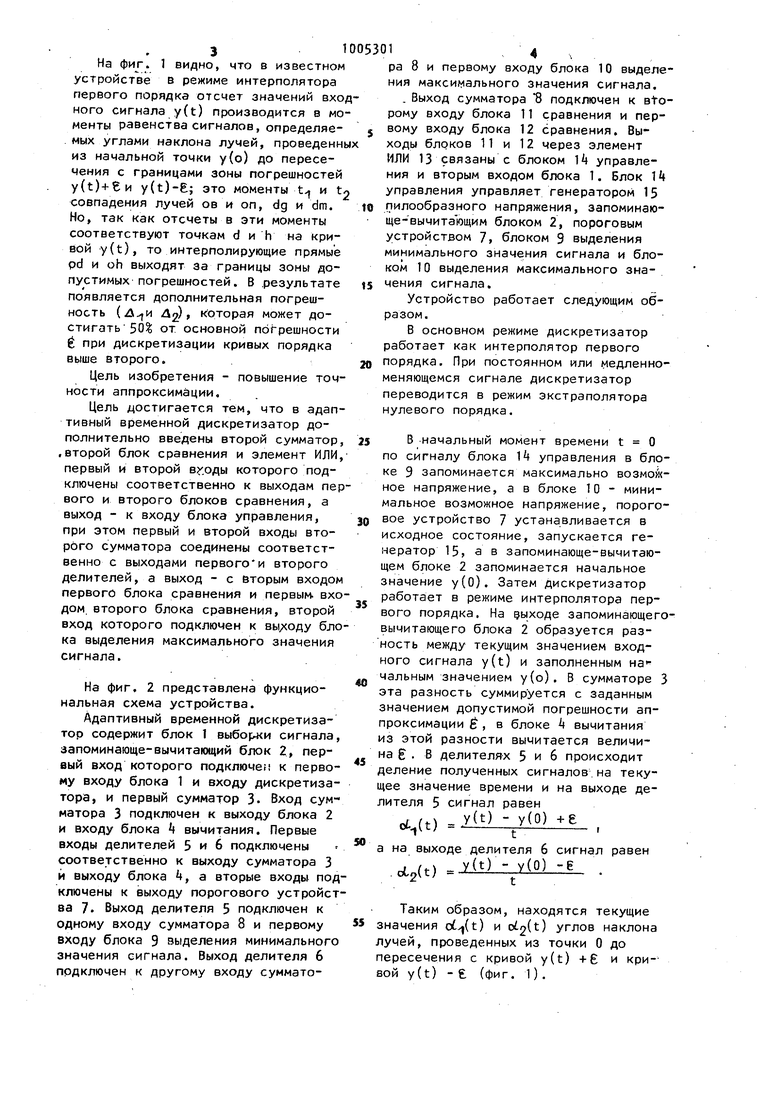

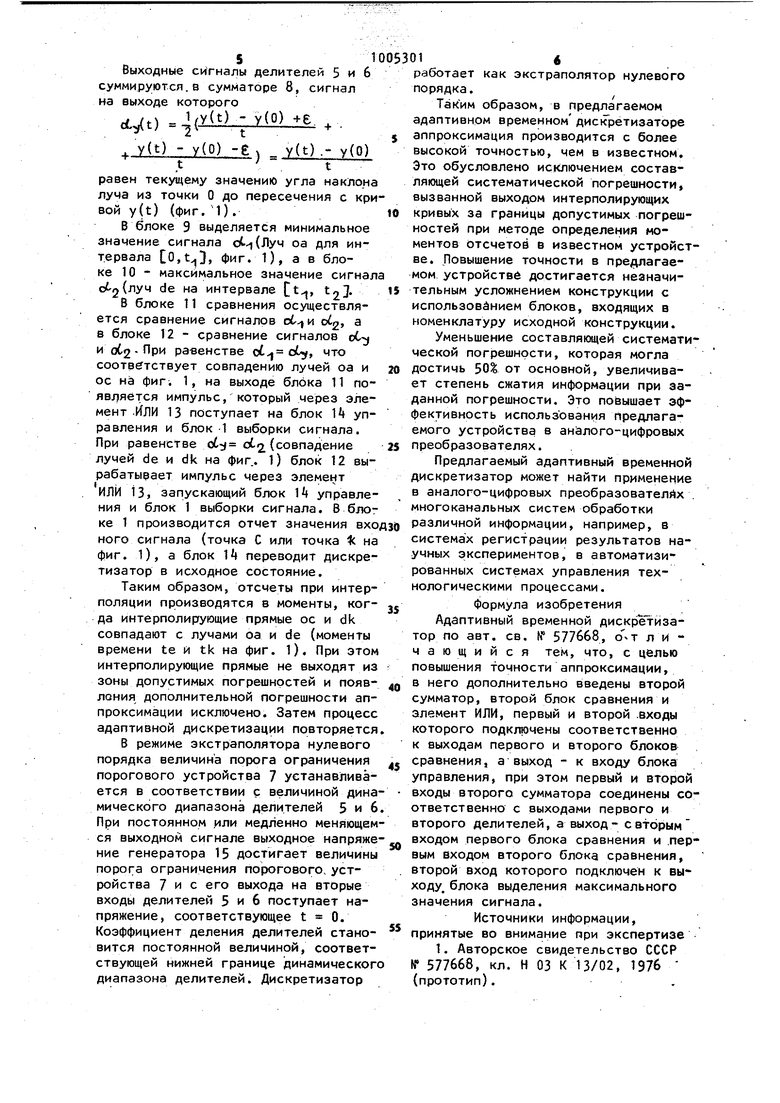

20 первого блока сравнения, выход которого соединен с входом блока управления и вторым входом блока выборки сигнала. О J. На фиг. 1 видно, что в известном устройстве в режиме интерполятора первого порядка отсчет значений вход ного сигнала у(t) производится в моменты равенства сигналов, определяемых углами наклона лучей, проведенны из начальной точки у(о) до пересечения с границами зоны погрешностей y(t)+Eи y(t)-E; это моменты и to совпадения лучей ов и оп, dg и dm. Но, так как отсчеты в эти моменты соответствуют точкам d и h на кривой y(t), то интерполирующие прямые pd и oh выходят за границы зоны допустимых погрешностей. В .результате появляется дополнительная погрешность ( Л , которая может достигать50% от основной погрешности ё при дискретизации кривых порядка выше второго. Цель изобретения - повышение точности аппроксимации. Цель достигается тем, что в адаптивный временной дискретизатор дополнительно введены второй сумматор, .второй блок сравнения и элемент ИЛИ/ первый и второй .оды которого подключены соответственно к выходам пер вого и второго блоков сравнения, а выход - к входу блока управления, при этом первый и второй входы второго сумматора соединены соответственно с выходами первого и второго делителей, а выход - с вторым входом первого блока сравнения и первым, вхо дом второго блока сравнения, второй вход которого подключен к вы/оду бло ка выделения максимального значения сигнала. На фиг, 2 представлена функциональная схема устройства. Адаптивный временной дискретизатор содержит блок 1 выборки сигнала, запоминающе-вычитающий блок 2, первый вход которого подключеп к первому входу блока 1 и входу дискретизатора, и первый сумматор 3. Вход сумматора 3 подключен к выходу блока 2 и входу блока вычитания. Первые входы делителей 5 и 6 подключены соответственно к выходу сумматора 3 и выходу блока t, а вторые входы под ключены к выходу порогового устройст ва 7. Выход делителя 5 подключен к одному входу сумматора 8 и первому входу блока 9 выделения минимального значения сигнала. Выход делителя 6 подключен к другому входу сумматора 8 и первому входу блока 10 выделения максимального значения сигнала. Выход сумматора 8 подключен к Btoрому входу блока 11 сравнения и первому входу блока 12 сравнения. Выходы блоков 11 и 12 через элемент ИЛИ 13 связаны с блоком 14 управления и вторым входом блока 1. Блок 1k управления управляет генератором 15 пилообразного напряжения, запоминающе-вычитаЪщим блоком 2, пороговым устройством 7, блоком 9 выделения минимального значения сигнала и блоком 10 выделения максимального значения сигнала. Устройство работает следующим образом. В основном режиме дискретизатор работает как интерполятор первого порядка. При постоянном или медленноменяющемся сигнале дискретизатор переводится в режим экстраполятора нулевого порядка. В начальный момент времени t О по сигналу блока k управления в блоке 9 запоминается максимально возможное напряжение, а в блоке 10 - минимальное возможное напряжение, пороговое устройство 7 устанавливается в исходное состояние, запускается генератор 15, а в запоминающе-вычитающем блоке 2 запоминается начальное значение у(0). Затем дискретизатор работает в режиме интерполятора первого порядка. На дыходе запоминающеговычитающего блока 2 образуется разность между текущим значением входного сигнала y(t) и заполненным на чальным значением у(о). В сумматоре 3 эта разность суммируется с заданным значением допустимой погрешности аппроксимации ё , в блоке вычитания из этой разности вычитается величина g. В делителях 5 и 6 происходит деление полученных сигналов.на текущее значение времени и на выходе делителя 5 сигнал равен еЦи) -У у(0) , а на выходе делителя 6 сигнал равен .. (О y(t) -У(0) -g . Таким образом, находятся текущие значения ot(t) и (1) углов наклона лучей, проведенных из точки О до пересечения с кривой y(t) +6 и кривой у(t) - (фиг. 1). Выходные сигналы делителей 5 и 6 суммируются.в сумматоре 8, сигнал на выходе которого ct.t) . y(t) - у(0) -. y(t). t t равен текущему значению угла наклона луча из точки О до пересечения с кри вой y(t) (фиг. ). В блоке 9 выделяется минимальное значение сигнала с)1--)(Луч оа для интервала СО,цЗ фиг. 1), а в блоке 10 - максимальное значение сигнал интервале t, tjj. В блоке 11 сравнения осуществляется сравнение сигналов сб., и , а в блоке 12 - сравнение сигналов оС-у и об2 - При равенстве Ы-| сЦ, что соответствует совпадению лучей оа и ос на фиг. 1, на выходе блока 11 появ;7яётся импульс, который через элемент .Или 13 поступает на блок k управления и блок 1 выборки сигнала. При равенстве о6: ci2 (совпадение лучей de и dk на фиг.. 1) блок 12 вырабатырает импульс через элемент ИЛИ 13, запускающий блок 1 управления и блок 1 выборки сигнала. В блоке 1 производится отчет значения вход ного сигнала (точка С или точка 4с на фиг. 1), а блок Ц переводит дискретизатор в исходное состояние. Таким образом, отсчеты при интерполяции производятся в моменты, когда интерполирующие прямые ос и dk совпадают с лучами оа и de (моменты времени te и tk на фиг. 1). При этом интерполирующие прямые не выходят из зоны допустимых погрешностей и появления дополнительной погрешности аппроксимации исключено. Затем процесс адаптивной дискретизации повторяется. В режиме экстраполятора нулевого порядка величина порога ограничения порогового устройства 7 устанавливается в соответствии с величиной динамического диапазона делителей 5 и 6 При постоянном или мед/teHHo меняющемся выходном сигнале выходное напряжение генератора 15 достигает величины порога ограничения порогового, устройства 7 и с его выхода на вторые входы делителей 5 и 6 поступает напряжение, соответствующее t 0. Коэффициент деления делителей становится постоянной величиной, соответствующей нижней границе динамического диапазона делителей. Дискретизатор 1 1 работает как экстраполятор нулевого порядка. Таким образом, в предлагаемом адаптивном временном дискретизаторе аппроксимация производится с более высокой точностью, чем в известном. Это обусловлено исключением составляющей систематической погрешности, вызванной выходом интерполирующих кривых за границы допустимых погрешностей при методе определения моментов отсчетов в известном устройстве. Повышение точности в предлагаемом устройстве достигается незначительным усложнением конструкции с использованием блоков, входящих в номенклатуру исходной конструкции. Уменьшение составляющей систематической погрешности, которая могла достичь 50 от основной, увеличивает степень сжатия информации при заданной погрешности. Это повышает эффективность использования предлагаемого устройства в анйлого-цифровых преобразователях. Предлагаемый адаптивный временной дискретизатор может найти применение в аналого-цифровых преобразователях . многоканальных систем обработки Различной информации, например, в системах регистрации результатов научных экспериментов, в автоматизированных системах управления технологическими процессами. Формула изобретения Адаптивный временной дискретйзатор по авт. св. К 577668, ли чающийся тем, что, с целью повышения точности аппроксимации, в него дополнительно введены второй сумматор, второй блок сравнения и элемент ИЛИ, первый и второй .входы которого подключены соответственно к выходам первого и второго блоков сравнения, а выход - к входу блока управления, при этом первый и второй входы второго сумматора соединены соответственно с выходами первого и второго делителей, а выход- с вторым входом первого блока сравнения и .пер вым входом второго блока сравнения, второй вход которого подключен к выходу, блока выделения максимального значения сигнала. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР К 577668, кл. Н 03 К 13/02, 1976 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный временной дискретизатор | 1976 |

|

SU577668A1 |

| Адаптивный временной дискретизатор | 1977 |

|

SU680015A1 |

| Адаптивный временной дискретизатор | 1976 |

|

SU575770A1 |

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 2015 |

|

RU2583707C1 |

| Адаптивный временной дискретизатор | 1978 |

|

SU721826A1 |

| Устройство для определения моментов времени квантования сигнала | 1980 |

|

SU855991A2 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Адаптивный временной дискретизатор | 1978 |

|

SU777657A1 |

| Адаптивный временной дискретизатор | 1979 |

|

SU805341A1 |

| Адаптивный временной дискретизатор | 1985 |

|

SU1267457A1 |

Авторы

Даты

1983-03-15—Публикация

1981-07-28—Подача