Изобретение .относится к автоматике и вычислительной технике и может быть использовано в информационноизмерительных системах для передачи сигналов малым количеством данных, необходимых для восстановления сигнала с максимально-допустимое относи тельной погрешностью. Известен адаптивный временной дис кретизатор, содержащий блок дифферен цирования, запоминающе-вычитающий блок, управляемый делитель напряжения , блок сравнения и счетчик l3 Известен также адаптивный временной дискретизатор, содержащий управляемый ключ, блок Пс1мяти, измеритель ный элемент блок сравнения и блок управления C2J. Недостатком известных устройств является низкая точность работы. Наиболее близким к предлагаем м У является адаптивный временной дйскре тиэатор, содержащий блок задания допустиьюй погрешности, управляемый ключ, сигнальный вход которого подключен к входной шине дискретизатора и к сигнальному входу запоминающего блока, а управляющий вход к управляющему входу запокшнающего блока и к входам Обнуления счетчика и интегратора, причем выходы разрядов счетчика, соединенного счетным входом с шиной тактовых импульсов, подключены к .управляющим входам управляемого генератора логарифмической функции и к управляющимвходам управляемого делителя напряжения, сигнальный вход которого соединен, с первым входом вычитающего блокад, а выход - с сигнальным входом интегратора, подключенного выходом к второму входу вычитающего блока, соединенного выходом с первым входом компаратора, причем, выход управляемого ключа является выходом дискретнзатора, а выход запоминающего блока, который дополнительно выполняет функции вычитания, подключен к сигнальному входу управляемого делителя напряжения, причем управляелшй генератор логарифмической функции соединен входом опорного сигнала с выходом блока задания допустимой погрешности, а выходсм - со вторым входом компаратора, подключенного выходом к управляющему входу управляемого, ключа З . Недостатком известного устройства является уменьшение длины гщаптивного временного интервала дискретизации при обеспечении заданной относительной погрешности восстановления .

Цель 1|зобретения - увеличение длины адаптивного временного интервала при обеспечении Зсщанной относительной погрешности.

С этой целью в ад1аптивный временной дискретизатор, содержащий блок задания допустимой погрешности, управляемый ключ, сигнальный вход которого подключен к входной шине дискретизатора и к сигнальному входу запоминающего блока, а управляющий вход к управляющему входу запоминающего блока и к входам обнуления счетчика и интегратора, причем выходы разрядо счетчика, соединенного счетным входо с шиной тактовых импульсов, подключены к управляющим входам управляемого генератора логарифмической функции и к управляющим входам первого управляемого делителя напряжения, сигнальный вход которого соединен с nepBfcJM входом вычитающего блока, а выход - с сигнальным бходом интегратора, подключенного- выходом к втоpoMVB-входу вычитающего блока, соединенного выходом с первым входом первого компаратора, причем выход управляемого ключа является выходом дискретизатора, дополнительно введены управляемый усилитель напряжения, второй управляемый делитель напряжения, элемент ИЛИ и второй компаратор подключенный первым входом к выходу вычитгиощего блока, причем элемент ИЛИ соединен выходом с управляемого входом управляемого ключа, а входами - с выходами первого и второго компараторов, подключенных вторыми входами соответственно к выходам второго управляемого делителя напряжения и управляемого усилителя напряжения, управляющие входы которых соединены с выходами блока задания допустимой погрешности, а сигнальные входы - с выходом управляемого генератора логарифмической функции, подключенного входом опориого сигнала к выходу запоминающего блока, причем сигнальный вход первого управляемого делителя напряжения сое.пинен с входной шиной дискретизатора .

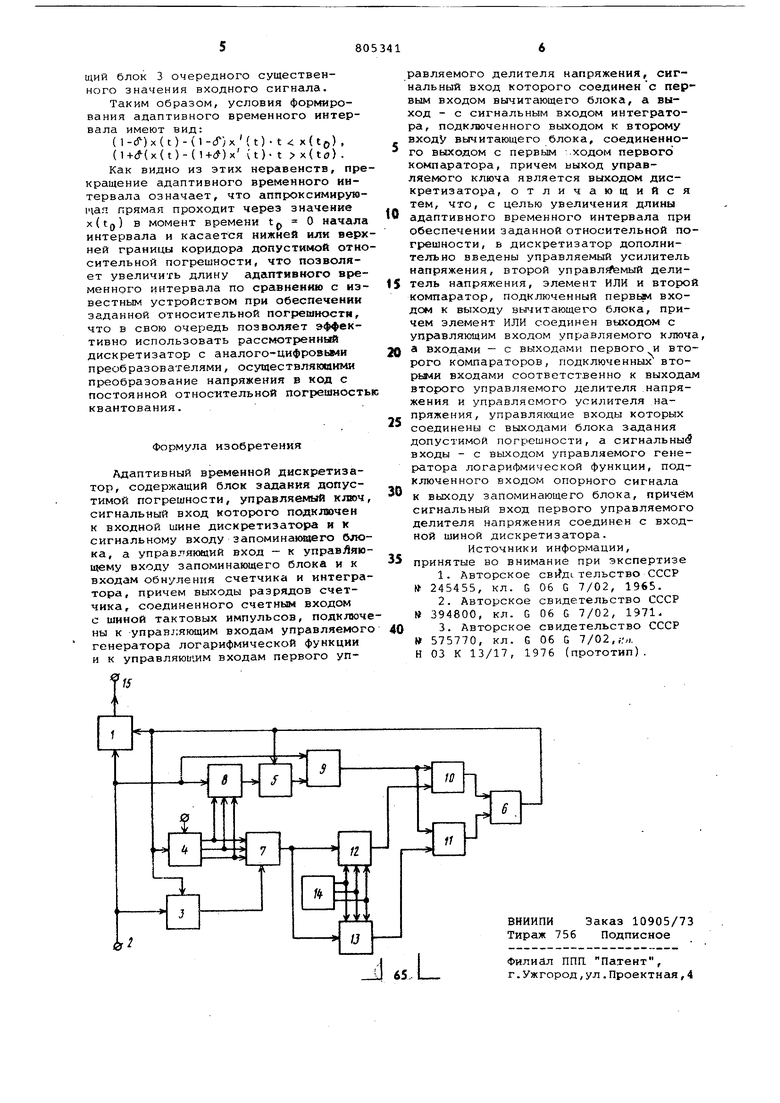

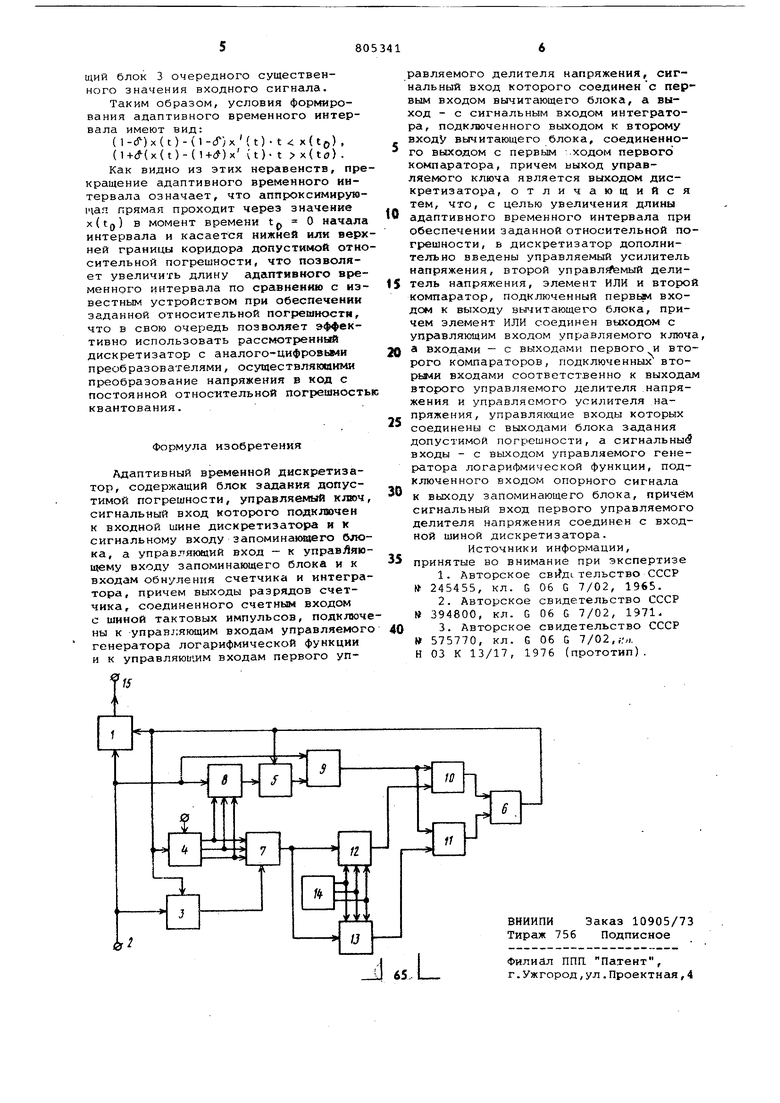

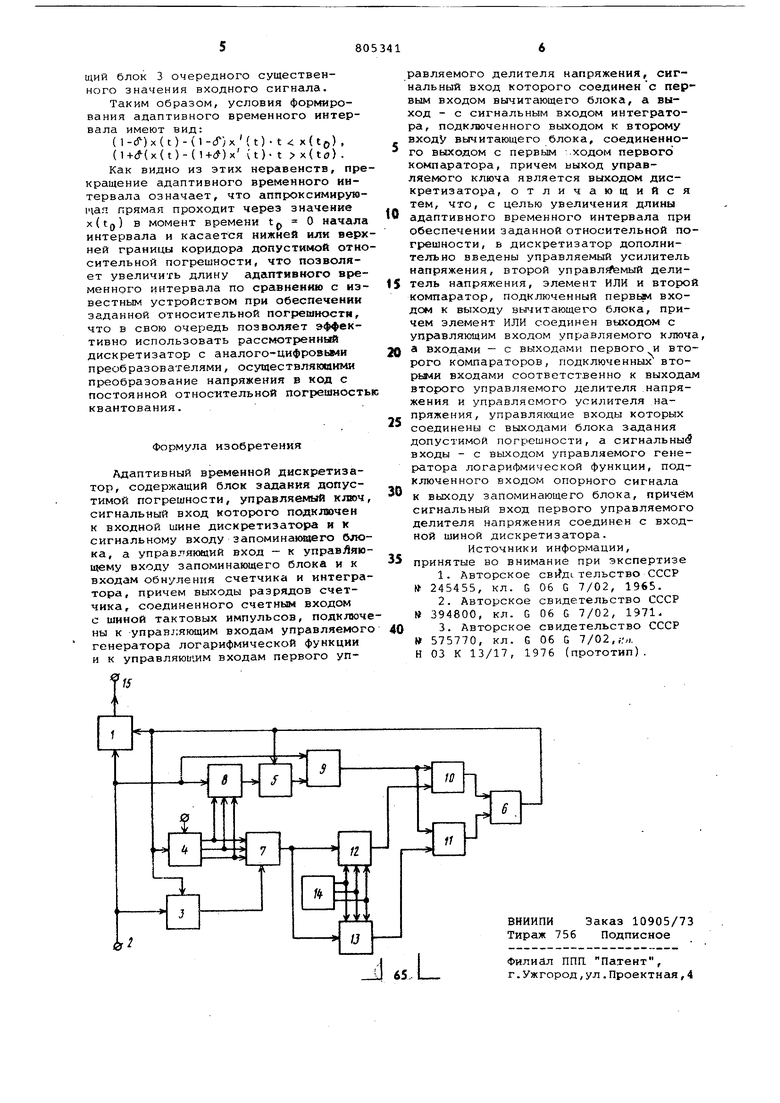

На чертеже изображена блок-схема устройства.

Адаптивный временной дискретизатор содержит управляемый ключ 1, сигнальный вход которого подключен к входной шине 2 дискретизатора и к сигнальному входу запоминающего блок 3, а управляющий вход - к управляющему входу запоминающего блока 3, к входам обнуления счетчика 4 и интегратора 5, и к выходу элемента ИЛИ 6. Выходы разрядов счетчика 4, соединенного счетным входом с шиной тактовых импульсов, подключены к управляю|4им входам управляемого генератора 7 логарифмической Функции и к управляющим входам первого управляемого делителя 8 напряжения. Делитель 8 соединен сигнальным входом с входной шиной 2 дискретиэатора и с первым входом вычитающего блока 9, а выходом с сигнальным входом интегратора 5. Выход Интегратора 5 подключен к второму входу вычитающего блока 9. Выхо блока 9 соединен с первыми входами первого и второго компараторов 10 и 11, подключенных выходами к входам элемента ИЛИ б. Вторые входы компа-раторов 10 и 11 соединены соответственно с выходами второго управляемого делителя напряжения 12 и управляемого усилителя напряжения 13. Делитель 12 и усилитель 13 подключен управляющими входами к выходам блока 14 задания допустимой погрешности, а сигнальными входами - к выходу управляемого генератора 7 логарифмической функции. Вход опорного сигнала генератора 7 соединен с выходом запоминающего блока 3. Выход ключа 1 является выходом 15 дискретизатора

Адаптивный временной дискретизато работает следующим образом.

С выхода вычитающего блока 9 на первые входы компараторов 10 и 11 в момент времени t поступает напряжени

-1dt - x(t),

. V о,

где x(t) - входной сигнал (напряжение) на входной шине 2 дискретизатора.

С выхода управляемого генератора 7 логарифмической функции на вторые входы компараторов 10 и 11 через управляемый делитель напряжения 12 с коэффициентом деления Ид- -- где (5 - допустимая относительная погрешность, задаваемая блоком 14, и через управляемый усилитель напряжения 13 с коэффициентом усиления Ку - --V- подаются напряжения:

2 .

X ( у En t,

и

3

1где X (, t

- значение входного сигнаОла, фиксируемое в запоминающем блоке 3 в момент времени tg.

В процессе работы компараторы 10 и 11 сравнивают напряжение с выхода вычитающего блока 9 с выходными напряжениями делителя 12 и усилителя 13 и в случае невыполнения одного из неравенств

и-з

и. и. Ui

выдают через элемент ИЛИ 6 управляющий сигнал на прекращение текущего адаптивного интервала временной дискретизации. Этот сигнал обнуляет интегратор 5, счетчик 4 и производит перезапись в запоминающий блок 3 очередного существенного значения входного сигнала.

Таким образом, условия формирования адаптивного временного интервала имеют вид:

(l-cf)x(t)-(l-cf)x(t).t x(to),

((x(t)-(l+()x (t). t x(to).

Как видно из этих неравенств, прекращение адаптивного временного интервала означает, что аппроксимирующая прямая проходит через значение x{t(j) в момент времени tp О начала интервала и касается нижней или верхней границы коридора допустимой относительной погрешности, что позволяет увеличить длину адаптивного временного интервала по сравнению с известным устройством при обеспечении заданной относительной погрешности, что в свою очередь позволяет эффективно использовать рассмотренньй дискретизатор с аналого-цифровыми преобразователями, осуществляюиими преобразование напряжения в код с постоянной относительной погрешность квантования.

Формула изобретения

Адаптивный временной дискретизатор, содержащий блок задания допустимой погрешности, управляемьй клвоч, сигнальный вход которого подключен к входной шине днекретизатора и к сигнальному входу запоминакиаего блока, а управлякяций вход к управЛяющему входу запоминающего блока и к входам обнуления счетчика и интегратора, причем вь7ходы разрядов счетчика, соединенного счетным входом с шиной тактовых импульсов, подключены к управляющим входам управляемого генератора логарифмической функции и к управляющим входам первого упff

равляемого делителя напряжения, сигнальный вход которого соединенс первым входом вычитающего блока, а выход - с сигнальным входом интегратора, подключенного выходом к второму входу вычитающего блока, соединенного выходом с первым -ходом первого компаратора, причем выход управляемого ключа является выходом дискретизатора, отличающийся тем, что, с целью увеличения длины адаптивного временного интервала при обеспечении заданной относительной погрешности, в дискретизатор дополнительно введены управляемый усилитель напряжения, второй управл мый делитель напряжения, элемент ИЛИ и второй компаратор, подключенный первь д входом к выходу вы итающего блока, причем элемент ИЛИ соединен выходом с управляющим входом управляемого ключа, Q а входами - с выходами первого и второго компараторов, подключенных втоpifcauiH входами соответственно к выходам второго управляемого делителя напряжения и управляемого усилителя напряжения, управляющие входы которых соединены с выходами блока задания допустимой погрешности, а сигнальный входы - с выходом управляемого генератора логарифмической функции, подключенного входом опорного сигнала к выходу запоминающего блока, причём сигнальный вход первого управляемого делителя напряжения соединен с входной шиной дискретизатора.

Источники информации, принятые во внимание при экспертизе

1.Авторское св11д1, тельство СССР № 245455, кл. G 06 G 7/02, 1965.

2.Авторское свидетельство СССР 394800, кл. G 06 G 7/02, 1971.

3.Авторское свидетельство СССР № 575770, кл. G 06 G 7/02,(.м.

Н 03 К 13/17, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный временной дискретизатор | 1976 |

|

SU575770A1 |

| Устройство для адаптивной дискретизации | 1982 |

|

SU1070566A1 |

| Адаптивный временной дискретизатор | 1977 |

|

SU680015A1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Адаптивный временной дискретизатор | 1987 |

|

SU1522242A1 |

| Устройство для определения моментов времени квантования сигналов | 1979 |

|

SU782146A1 |

| Адаптивный временной дискретизатор | 1988 |

|

SU1658187A1 |

| Адаптивный временной дискретизатор | 1978 |

|

SU721826A1 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| Адаптивный временной дискретизатор | 1986 |

|

SU1401500A1 |

Авторы

Даты

1981-02-15—Публикация

1979-01-16—Подача