(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ

дения, нулевой вход и нулевой выход второго триггера подсоединен к первому входу четвертого элемента совпадения, а первый вход блока синхронизации и приведения в исходное состояние подключен к единичному входу первого триггера.

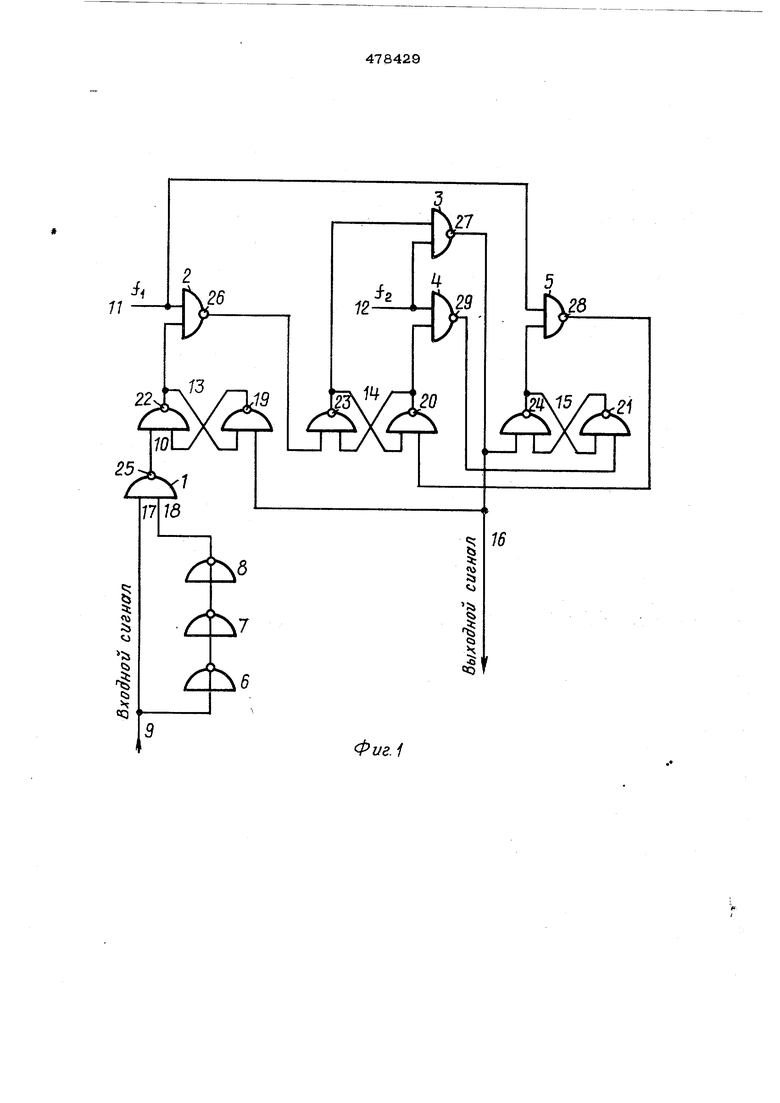

Изобретение пояснено чертежами.

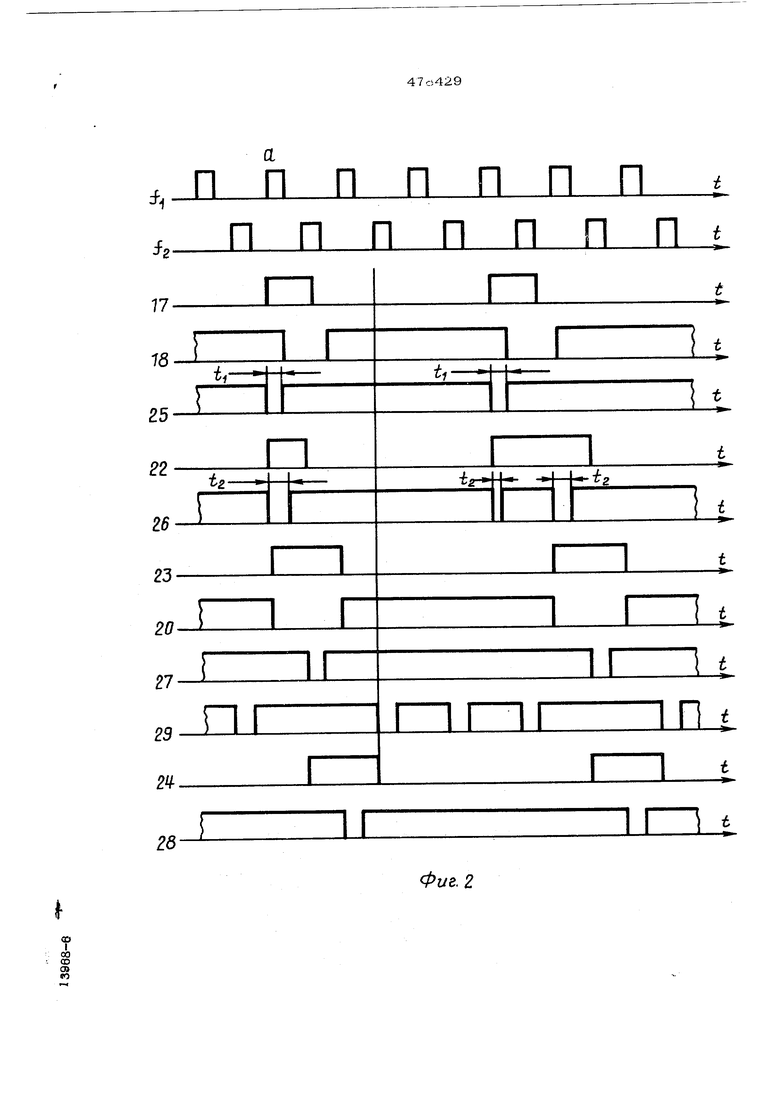

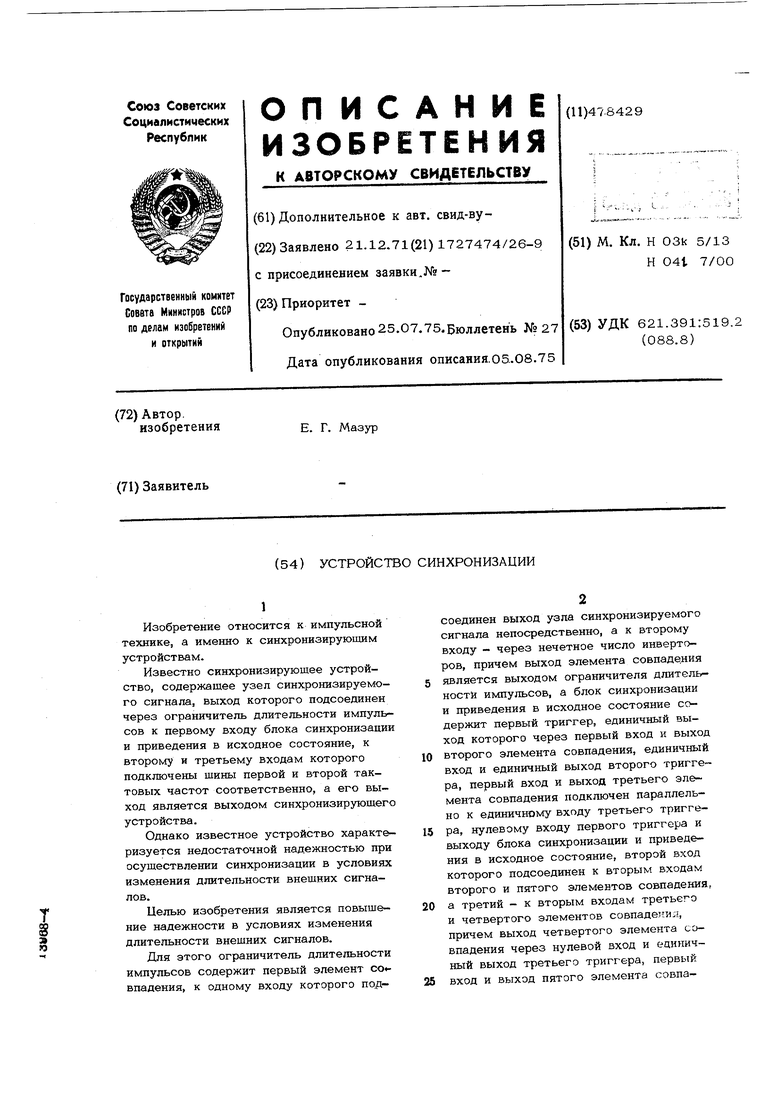

На фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2 временные диаграммы.

Синхронизирующее устройство содержи элементы совпадения 1-5, инверторы 6-8, узел 9 синхронизируемого сигнала, входные шины 10 - 12 блока синхронизации и приведения в исходное состояние, первый, второй и третий триггеры 13 - 1@, выходную шину 16. Элементы 1, 6, 7, 8 образуют ограничитель длительности импульсов, а остальные элементы - блок синхронизации и приведения в исходное состояние. К шинам 11, 12 подводятся колебания первой и второй тактовых частот f и f о

Устройство работает следующим образом.

В исходном состоянии, т.е. до поступления синхронизируемого Сигнала, вход

17первого блока совпадения 1 имеет низкий потенциал, а на его втором входе

18за счет нечетного числа инверторов 6 - 8 - высокий потенциал. На выходах элементов совпадения 1, 2, 3, 5 действуют высокие потенциалы.

Начальное состояние триггеров 13, 14, 15 нулевое, т.е. их нулевые выходы 19, 20, 21 имеют высокий потенциал, единичные выходы 22, 23, 24 - низкий.

При появлении в узле 9 положительного перепада напряжения происходит одновременное переключение первого элемента совпадения 1 и инвертора 6. На выходе 25 первого элемента совпадения 1 образуется низкий потенциал, вызывающий переключение первого триггера 13 в единичное состояние. После последовательного переключения инверторов 6, 7, 8 на втором входе 18 первого блока совпадения появляется низкий потенциал, который вызывает переключение его в исходное состояние, тем самым ограничивая длительность синхронизируемого внешнего сигнала. Задержка на переключение инверторов 6-8 определяет длительность отрцательного импульса 4| на выходе 25 первого элемента совпадения 1 (см. фиг. 2). Число инверторов 6-8 выбирают

таким, чтобы длительность отрицательного уровня на шине 10 была достаточной для переключения первого триггера 13.

После переключения триггера 13 в единичное состояние на его единичном выходе 22 появляется положительный потенциал, разрешающий переключение второго эле|угента совпадения 2 при поступлении положительного импульса первой тактовой частоты f по шине 11. Длительность выходного импульса t второго элемента совпадения 2 зависит от момента переключения первого триггера 13 относительно положительного уровня синхронизирующего сигнала (первой тактовой частоты f ).

Если длительность импульса t достаточна для переключения второго

триггера 14 (см. фиг. 2, а), то на выходе 23 появляется высокий потенциал.

Если длительность t в начале является недостаточной для переключения второго триггера 14 (см. фиг. 2,в),

то при поступлении следующего очередного положительного импульса первой тактовой частоты на выходе 26 второго блока совпадения 2 появляется отрицательный импульс, по длительности

равный положительным импульсам первой тактовой частоты f , который осуществляет переключение второго триггера 14 в единичное состояние.

После переключения второго триггера

14 в единичное состояние положительный потенциал на его единичном выходе 23 разрешает переключение третьего элемента совпадения 3 при поступлении положительного импульса второй тактовой частоты f, по шине 12, а отрицательный потенциал на нулевом выходе 20 запрещает переключение четвертого блока совпадения 4.

Отрицательный импульс, образованный

на выходе 27 третьего элемента совпадения 3, является выходным сигналом устройства, а также переключает третий триггер 15 в единичное состояние, а первый - в нулевое.

После переключения третьего триггера 15 в единичное состояние на его выходе 24. появляется высокий потенциал, разрешающий переключение пятого элемента совпадения 5 при поступлении очередного положительного импульса первой тактовой частоты .

Отрицательный Hivmynbc, появившийся на выходе 28 пятого блока совпадения переключает второй триггер 14 в нулевое состояние.

Третий триггер 15 возвращается в исходное состояние отрицательным импульсом, возникающим на выходе 29 четвертого блока совпадения а такте частотыfg после переключения второго триггера 14 в нулевое состояние.

Предмет изобретения

Устройство синхронизации, содержащее узел синхронизируемого сигнала, выход которого подсоединен через ограничитель длительности импульсов к первому входу блока синхронизации и приведения в исходное состояние, к второму и третьему входам которого подключены щины первой и второй тактовых частот соответственно, а его выход является выходом устройства, отличающееся тем, что, с целью повышения надежности в условиях изменения длительности внешних сигналов, ограничитель длительности импульсов содержит первый элемент совпадения, к одному входу которого подсоединен выход узла синхронизируемого сигнала непосредственно, а к второму входу через нечетное число инверторов, причем выход элемента совпадения является выходом ограничителя длительности импульсов, а блок синхронизации и приведения в исходное состояние содержит первый триггер, единичный выход которого через первый вход и выход второго элемента совпадения, единичный вхтэд и

единичный выход второго триггера, первый вход и выход третьего элемента совпадения подключен параллельно к единичному входу третьего триггера, нулевому входу первого триггера и выходу

блока синхронизации и приведения в

исходное состояние, второй вход которого подсоединен к вторым входам второго и пятого элемен ов совпадения, а третий - к вторым входам третьего и четвертого элементов совпадения, причем выход четвертого элемента совпадения через нулевой вход и единичный выход третьего триггера, первый вход и выход пятого элемента совпадения, нулевой вход и

нулевой выход второго триггера подсодинен к первому входу четвертого элемента совпадения, а первый вход блока синхронизации и приведения в исходное состояние подключен к единичному входу

первого триггера.

16

I §

«о

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсов | 1978 |

|

SU739721A1 |

| Устройство для синхронизацииСигНАлОВ | 1979 |

|

SU853789A1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU940285A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU748839A1 |

| Синхронизирующее устройство | 1988 |

|

SU1619387A1 |

| Устройство для синхронизации сигналов | 1982 |

|

SU1069144A2 |

| Синхронизирующее устройство | 1979 |

|

SU792574A1 |

| Устройство для синхронизации импульсов | 1978 |

|

SU758503A1 |

| Устройство для синхронизации импульсных последовательностей | 1981 |

|

SU961120A1 |

| Устройство для контроля последовательности импульсов | 1989 |

|

SU1709508A1 |

Авторы

Даты

1975-07-25—Публикация

1971-12-21—Подача