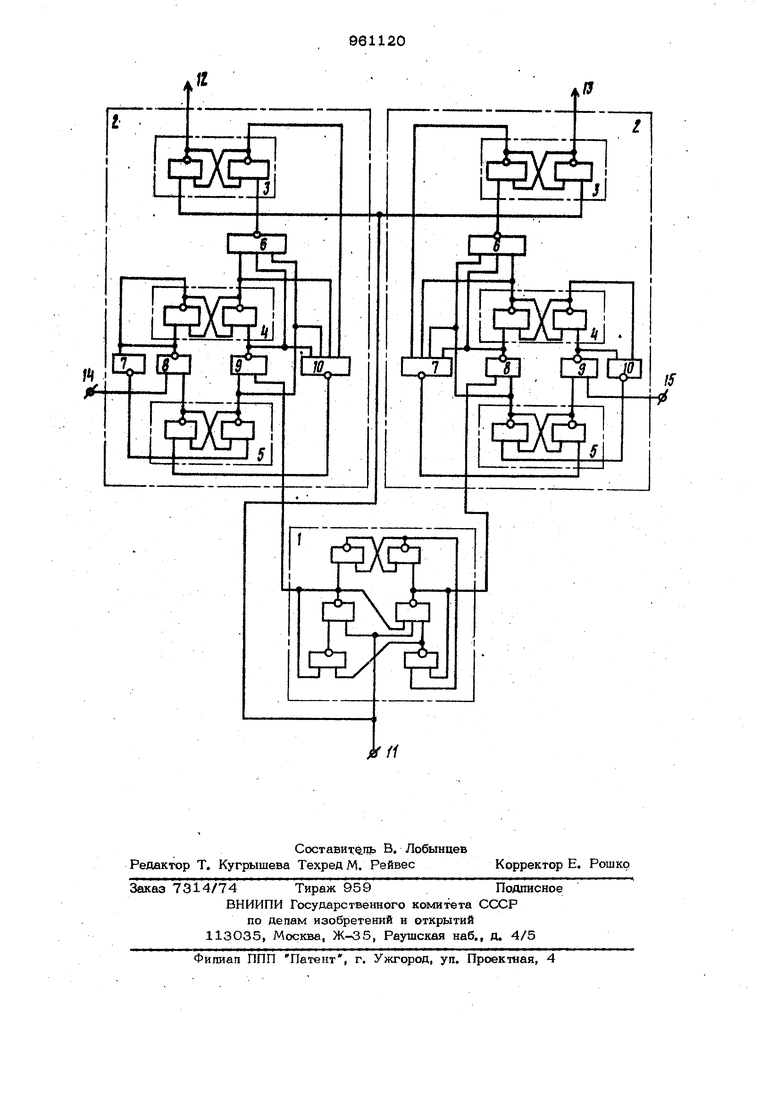

Изобретение относится к импульсной технике и может быть испопьзовано в синхронизаторах и в других устройствах АПЯ синхронизации случайных импульс ных поспедоватепьностей. Известно устройство дня синхронизации последовательностей, содержащее Д-триггер-датчик опорной частоть. и два блока синхронизации tl. Однако в данном устройстве А)граничен диапазон длительностей синхронизируемых импульсов. Наиболее близким к изобретению техническим решением является устройство для синхронизации импульсных последовательностей, которое содержит Д-триг- гер-датчик опорной частоты и два блока синхронизации, содержащие первые RS триггеры, элементы И-НЕ н вторые RS триггеры. Единичные входы вторых RS - триггеров соединены с шинами синхронизируемых последовательностей, а прямые выходы - с первыми входами первых эле ментов И-НЕ, вторые входы которых сое динены с первыми входами вторых элементов И-НЕ и с выходами элементов НЕ, входы которых подключены к выходам Д-триггера-датчика. Прямые выходы первых RS -триггеров соединены с первыми входами третьих элементов И-НЕ и с первыми входами четвертых элементов И-НЕ. Выходы первых элементов ИНЕ соединены с вторыми входами третьих элементов И-НЕ и с единичными входами первых RS -триггеров. Нулевые входы первых PS -триггеров соединены с выходами вторых элементов И-НЕ, вторые входы которых подключены к инверсным выходам вторых RS -триггеров, нулевые входы которых соединены с выходами третьих элементов И-НЕ. Вторые входы четвертых элементов И-НЕ соединены с первыми входами вторых элементов И-НЕ, входящих, в противоположные блоки синхронизации, а выходы подкпюче ны к выходным щинам Г2 Д. Недостатками этого устройства явпяются ограниченность диапазонов синхроHHSHpyejvflax частот и дпитепьностйй импульсов синхронизируемых поспедоватепь ностей, Цепь изобретения - расширение функ ционапьных возможностей устройства. Поставленная цепь достагается тем, что устройство для синхронизации импульсных последовательностей, содержащее датчик опорной частоты, два блока синхронизации, каждый из которых содержит первый триггер, подключенный через J первый и второй элементы И-НЕ к входам второго триггера, первый выход кото рого соединен с первым входом третьего элемента И-НЕ, второй выход Второго триггера подключен к первому входу четвертого элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ, а выход четвертого элемента И-НЕ соединен с первым входом первого триггера, второй вход второго элемента И-НЕ каждого блока синхронизации является первым входом блока и подключен к соответствующему выходу дат чика опорйой частоты, второй вход блока синхронизации подключен к шине синхронизируемой последовательности, вход Датчика опорной частоты подключен к третьим входам блоков синхронизации, а в каждый блок синхронизации дополнительно введены элемент совпадения и триггер первый вход которого является третьим входом блока синхронизации, второй вход схюдинен с выходом третьего основного элемента И-НЕ, а первый выход дополнительного триггера подключен к первому входу дополнительного элемента И-НЕ, второй вход которого соединен с первым I выходом второго основного триггера, тре тий вход соединен с первым выходом пер вого основного триггера и с вторым входом третьего основного элемента И-НЕ, а четвертый вход подключен к первому входу второго основного триггера и к третьему входу третьего основного элемента И-НЕ, выход дополнительного элемента И-НЕ соединен с вторым входом первого основного триггера, причем второй вход первого основного элемента И- НЕ является вторым входом блока синхронизации. На чертеже представлена функциональная схема устройства для синхронизаши импульсных последовательностей. Устройство содержит датчик 1 опорной частоты на Д-триггере, блоки 2 синхронизации, каждый из которых содержит триггеры 3-5, элементы И-НЕ 6-10, шиНУ 11 синхроимпульсов, выходные шины 12 и 13, шины 14 и 15 синхронизируемых последовательностей. Устройство работает следующим образом., На вход датчика 1 с шины 11 поступает частота синхроимпульсов F. На выходах Датчика 1 вырабатываются две несовпадающие импульсные последовательности отрицательных импульсов Рд/2 и FO /2, сдвинутые по. фазе на период частоты FO с длительностью импульсов, равной полупериоду частоты 1. В исходном состоянии триггер 4 петрвого блока 2 находится в состоянии логического нуля, триггер 5 в состоянии логической единицы, триггер 3 в состоянии логической единицы. При этом на вход элемента И-НЕ 8 с прямого выхода триггера 5 поступает разрешающий потенциал. Первый положительный импульс часто1ты Р с шины 14 проходит через открытый элемент И-НЕ 8 и устанавливает триггер 4 в-единичное состояние. При этом с прямого выхода триггера 4 на вход элемента И-НЕ 7 поступает разрешающий потенциал. Задним фронтом импульса частоты F триггер 5 через открытые элементы ИНЕ 8 и 7 устанавливается в нулевое состояние, при этом с его инверсного выхода на входы элементов И-НЕ 6, 9 и 10 поступает разрешающий, потенциал. Первый положительный импульс частоты Ро/2 с выхода датчика 1 проходит через открытый элемент И-НЕ 6 и устанавливает триггер 4 в исходное нулевое состояние. После этого с иггеерсного выхоДа триггера 4 на входы элементов И-НЕ 9 и 1О поступает разрешающий потенциал. При одновременном вйдоействии на триггер 3 положительного импульса частоты FO по единичному и через открытые элементы И-НЕ р и 6 отрицательного импульса частоты /2 по нулевому входу триггер 3 устанавливается в нулевое состояние н через открытый элемент И-НЕ 10 устанавливает в исходное единичное состояние триггер 5. После чего на входы элементов Й-НЕ 9, 10 и 6 с нулевого выхода триггера 5 поступает запрещак)щий потенциал. При последовательной, установке триггеров 3 и 5 соответственно S нулевое и единичное состояния на выходах элеме й)В И-НЕ 9 и 10 формируются короткиеотрицательные импульсьи В еркшпн(йл сЪстоянии 596 триггер 5 находится до появления на шине 14 следующего отрицательного фронта синхронизируемой импульсной последовательности. По окончании положительного импульса частоты Ро на шине 11 триггер 3 устанавнивается в исходное единичное сост(жние. . Таким образом на каждый отрицательный фонтимдупьснсй последовательноеТВ, поступаюшей.на шину 14, на входной шике 12 вырабатывается один отрицатель ный импульс, совпадающий по времени с икшульсом на выходе датчика 1. Анаиогично синхронизируется импуль. сная поспедовате наность с частотой FO поступающая на шину 15. Синхронизация производится частотой PQ/2, сдвинутой относительно частоты Fo/2 на период час тоты FQ, что приводит к появлению на выходных шинах 12 и 13 устройства дву импульснь1Х последовательностей F а, разнесённых во времени на период частоты FO-, Таким образом, предлагаемое устройство обеспечивает синхронизацию последовательностей импульсов с частотами, Не пренышающими Ро/2, при этом Дгштёльноспэ синхронизируемых импульсов не ограничена, так как синхронизация осуществляется по их отрицательным фронтам Формула изобретения Устройство для синхронизации импульс ных последовательностей, содержащее датчик опорной частоты, два блока син}фонизации, каждый из которых содержит первый триггер, подключенный через первый и второй элементы И-НЕ к входам второго триггера, первый выход которого соединен с первым входом третьего элемента И-НЕ, второй выход второго триг0гера подключен к первому входу четвертого элемента И-НЕ, второй входкоторого соединен с выходом первого anetteHTa И-НЕ, а выход четвертого элемента ИНЕ соединен с первым входом первого триггера, второй вход второго элемента И-НЕ каждого блока синхронизации является первым входом блока и подключен к соответствующему выходу датчика onojvной частоты, второй вход блока синхронизации подключен к щине синхронизируемой последовательности, отличающееся тем, что, с целью расширения функциональных возможностей, вход датчика опорной частоты подключен к трв-t тъим входам блоков синхронизации, а в каждый блок синхронизации дополнительно введены элемент совпадения и триггер, первый вход которого является третьим входом блока синхронизации, второй вход соеданен с выходе третьего основного элемента И-НЕ, а первый выход дополнительного триггера подключен к первому входу дополни те льнот-о элемента И-НЕ, второй вход которого соединен с первым выходом второго основного триггера,третий вход соединен с первым выходом первого основного триггера и с вторым vxio дом третьего основного элемента И-НЕ, а четвертый вход подключен к первому входу второго основного триггера и к третьему входу третьего основного элемента И-НЕ, выход дополнительного элемента И-НЕ соединен с вторым входом первого основного триггера, причем Второй - вход первого основного элемента ИНЕ является вторым входом блока син- . : фонизации. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СХ;СР NO 321931, кл. Н ОЗ К 5/00, 197Д. 2.Авторское свидетельство СССР №611294, кл. Н ОЗ К S/OO, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсных последовательностей | 1979 |

|

SU864521A1 |

| Устройство для синхронизации импульсных последовательностей | 1975 |

|

SU611294A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834548A1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1990 |

|

SU1723658A2 |

| Устройство для измерения радиального зазора в турбомашинах | 1989 |

|

SU1670370A1 |

| Устройство синхронизации | 1971 |

|

SU478429A1 |

| Устройство привязи к сигналам точного времени | 1987 |

|

SU1522146A1 |

| Преобразователь интервала времени в цифровой код | 1978 |

|

SU782149A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 2002 |

|

RU2238610C2 |

| Синхронизируемый вентильный электродвигатель | 1985 |

|

SU1317581A1 |

Авторы

Даты

1982-09-23—Публикация

1981-02-11—Подача