1

Изобретение относится к вычислительной технике и может быть использовано в преобразователях временного интервала, частоты и фазы в код, ра- 5 ботающих в широком диапазоне частот.

Известны устройства для синхронизации импульсов , используемые в дискретной автоматике и электронной технике, состоящие из двух тактируемых tO триггеров и одного триггера с установочными входами, одного инвертора и пяти схем совпадения 1.

Однако в этих устройствах не сохраняется длительность синхронизи- j руемых импульсов. Кроме того, необходимо наличие импульсов вспомогательной тактовой частоты для возвращения схемы в исходное состояние.

Наиболее близким по технической 20 сущности к предлагаемому является устройство, содержащее дифференциругаций блок ,дифференцирующие ;цепи, триггеры, импульсно-потенциальные схемы совпадения и реверсивный счет- 25 чик 2.

Недостатком этого устройства является наличие сбоев синхронизации при совпадении во времени переднегсг фронта синхронизируемых импульсов

ямпульсами тактовой частоты, что ограничивает диапазон частот синхронизируемых импульсов.

Цель изобретения - расширение

.функциональных возможностей устройства, а именно обеспечения работоспособности устройства при изменении в широких пределах частоты синхронизируемых импульсов.

Поставленная цель достигается тем, что в устройстве для синхронизации импульсов, содержащем дифференцирующий блок, две дифференцирующие цепи, три триггера, два элемента совпадедения и реверсивный счетчик, вычитающий вход которого через первый элемент совпадения соединен с единичным выходом первого триггера, а суммирующий вход через второй элемент совпадения - с единичным выходом второго триггера, а единичные входы триггеров соединены с соответствующими выходами дифференцирующего блока, вход которого соединен с входом синхронизируемых импульсов, причем импульсные входы элементов совпадения соединены между собой, входом импульсов высокостабильной частоты, выход

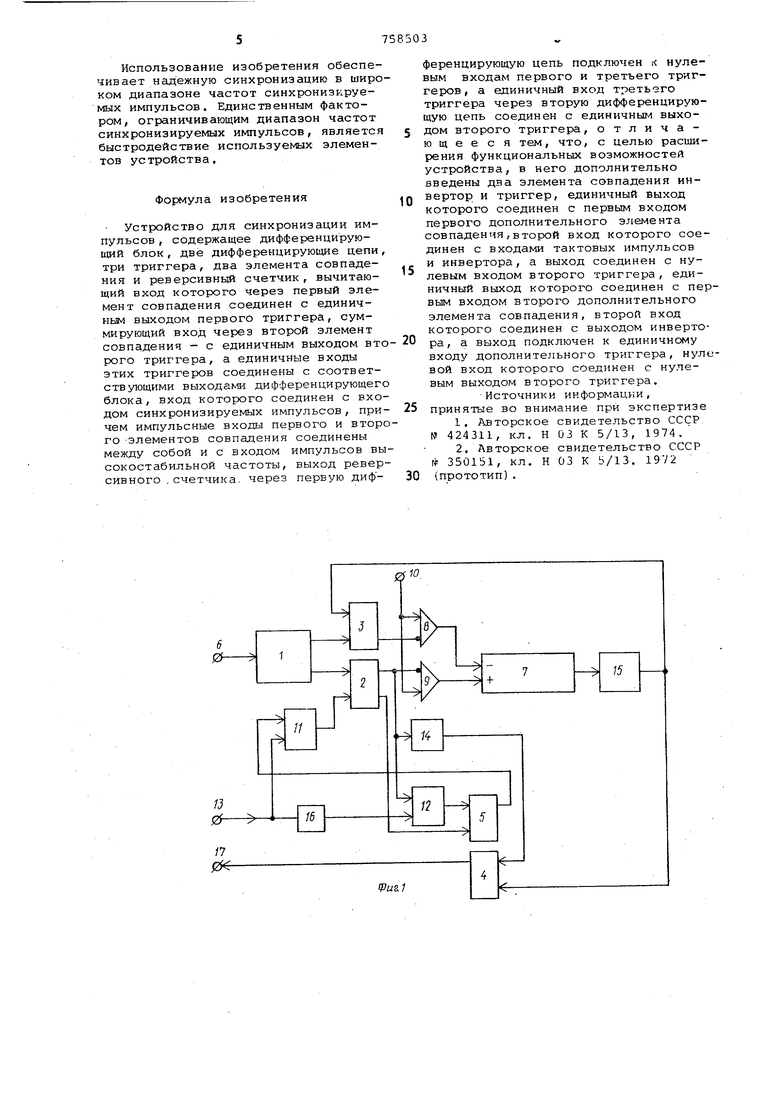

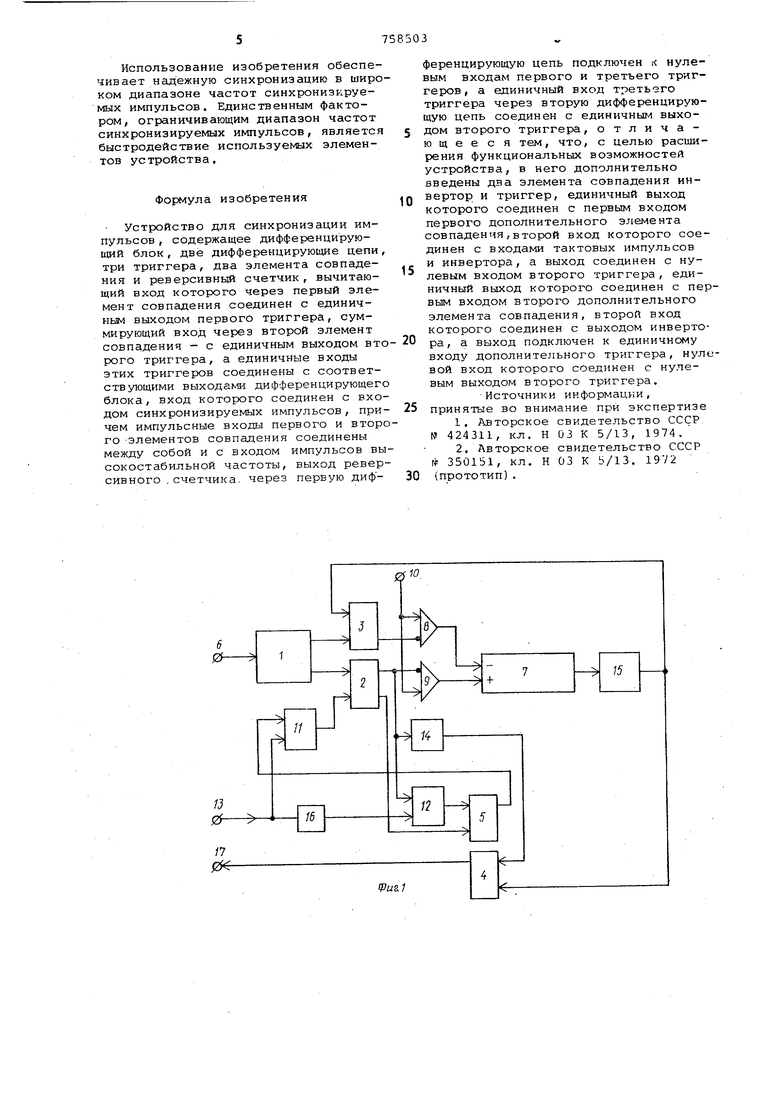

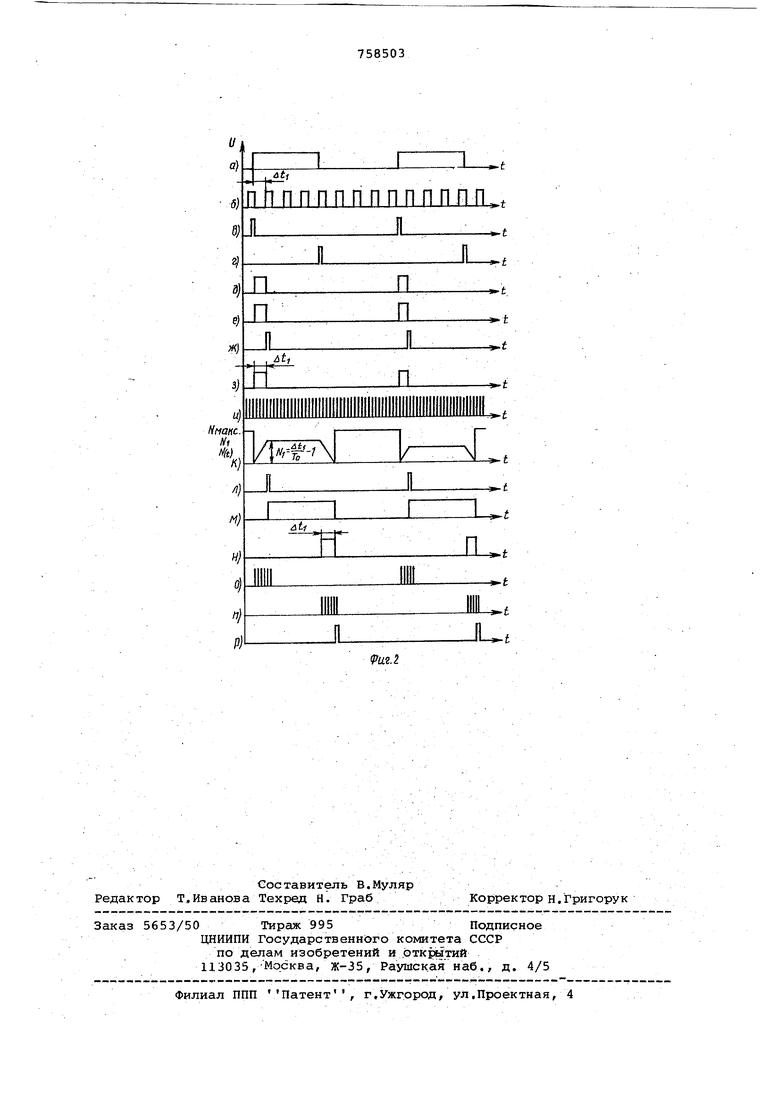

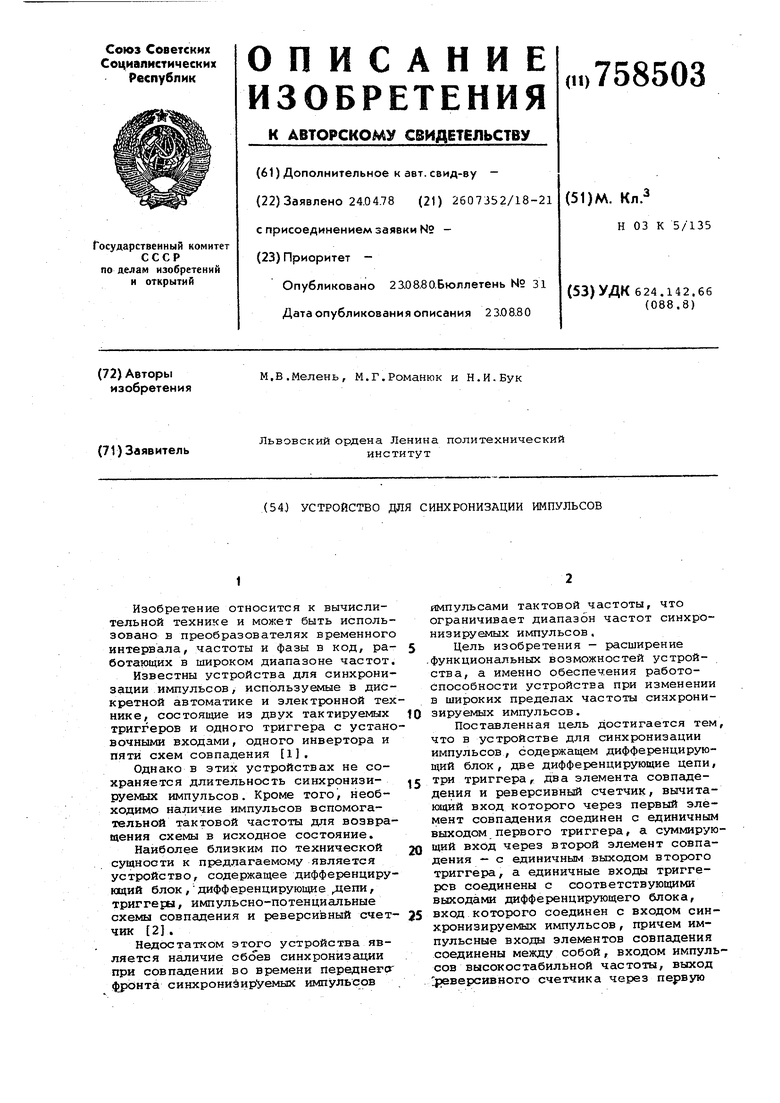

/реверсивного счетчика через первую дифференцирующую цепь подключен к: нулевым входам первого и третьего триггеров, а единичный вход третье го триггера через вторую дифференцирующую цепь соединен с единичным выходом второго триггера, дополнительно введены два элемента совпаде дня, инвертор : триггер, единичный в ход которого соединен с первым входом первого дополнительного элемент совпадения, второй вход которого соединен с входами тактовых импульсов и инвертора, а выход соединен г нулевЕлм входом второго триггера, единичный выход которого соединен с первым входом второго дополнительного элемента со падения, второй вход которого соеди нен с выходом инвертора, а выход подключен к единичному входу дополнительного триггера, нулевой вход к торого соединен с нулевым выходом второго триггера. На фиг.1 представлена структурна схема предлагаемого устройства; на фиг.2 - временные диаграммы, поясняющие его работу. Устройство для синхронизации импульсов содержит дифференцирующий блок 1 с двумя выходами, основные триггеры 2, 3, 4 и дополнительный триггер 5, вход синхронизируемых импульсов б, реверсивный счетчик 7, элементы совпадения 8 и 9, вход импульсов высокостабильной частоты 10 дополнительные элементы совпадения 11 и 12,вход тактовых импульсов 13, дифференцирующие цепи 14 и 15, инвертор 16 и выход устройства 17. Устройство работает следующим образом. В исходном положении все триггеры устройства находятся в нулевом состоянии. На соответствующих -входах элементов совпадения 8, 9, 11 и 12 присутствуют запрещающие .сигна лы, поэтому наличие тактовых импуль сов на первом .входе элемента совпадения 11- и на втором в.ходе элемента совпадения 12 не изменяет состояния устройства. С приходом первого синхронизируемого импульса (см. фиг.2 а) на вхо дифференцирующего блока 1 последний формирует короткие положительные им пульсы, соответствующие по времени переднему ( .см. фиг.2 в)и заднему (фиг.2 г) фронтам этого импульса. Импульс (см. фиг.2 в) ,. поступающий на единичный вход триггера 2, переводит его из нулевого состояния в единичное. С единичного выхода триг гера 2 сигнал поступает на вход эле мента совпадения 12. этом после ний вырабатывает выходной сигнал (с фиг.2 д) в naySe между тактовыми им пульсами (фиг.2 б), так как .между входом элемента совпадения 12 и.вхо дом тактовых импульсов 13 включен инвертор 16. Выходной сигнал элемента совпадения 12 переводит триггер 5 из нулевого состояния в единичное (см. фиг,2 е). С единичного выхода триггера 5 сигнал поступает на второй вход элемента совпадения 11, который с приходом первого тактового импульса (см. фиг.2 б) на первый его вход вырабатывает выходной импульс (см, фиг.2ж) который поступает на нулевой вход триггера 2, возвращая его нулевое состояние, а положительный импульс с нулевого выхода триггера 2 поступает на нулевой вход триггера 5, возвращая его также в нулевое состояние. Таким образом, на единичном выходе триггера 2 формируется положительный импульс (см. фиг,2 з) прямоугольной формы, длительности д t, который разрешает прохождение импульсов высокостабильной частоты (см, фиг.2 и) через импульсно-потенциальный элемент совпадения 9 на суммирующий вход реверсивного счетчика 7, имеющего в исходном состоянии максимальный код (см, фиг.2 к) . За время At в реверсивном счетчике 7 запишется код; Д-t, , где TQ - период следования импульсов высокостабильной частоты. В момент окончания импульсного сигнала (см. фиг.2з) дифференцирующая цепь 14 формирует импульс (см. фиг.2л-), устанавливающий триггер 4 в единичное состояние (см. фиг.2м). Импульс (см. фиг.2г), соответствующий заднему фронту синхронизируемого импульса, переводит триггер 3 в единичное состояние и с его выхода снимается импульс (см. .фиг.2н) прямоугольной формы, разрешающий прохождение импульсов высокостабильной частоты через импульсно-потен- циальный. элемент совпадения 8 на вычитающий вход реверсивного счетчика 7. При этом импульсы высокостабильной частоты считывают записанный в счетчик 7 код N. Импульсные последовательности на вых-оде элементов совпадения 9 и 8 представле.ны на фиг,2о и фиг .2п соответственно. Время, в течение которого в реверсивном счетчике 7 установится исходное значение кода N Qpf. , равно дtд. В момент установки максимального кода К дсчкс дифференцирующая цепь 15 фор- . мирует импульс (см. фиг.2р), устанавливающий триггеры 3 и 4 в нулевое состояние. Схема устройства возвращается в исходное состояние. ; Таким образом, синхронизируемый импульс, передний фронт которого совпадает с передним фронтом импульса тактовой частоты, формируется триггером 4.. , Использование изобретения обеспечивает надежную синхронизацию в широ ком диапазоне частот синхронизируемых импульсов. Единственным фактором, ограничивающим диапазон частот синхронизируемых импульсов, является быстродействие используемых элементов устройства. Формула изобретения Устройство для синхронизации импульсов ; содержащее дифференцирующий блок , две дифференцирующие цепи три триггера, два элемента совпадения и реверсивньй счетчик , вычитающий вход которого через первый элемент совпадения соединен с единичным выходом первого триггера, суммирующий вход через второй элемент совпадения - с единичным выходом вт рого триггера, а единичные входы этих триггеров соединены с соответствующими выходами дифференцирующег блока, вход которого соединен с вхо дом синхронизируемых импульсов, при чем импульсные входы первого и втор го -элементов совпадения соединены между собой и с входом импульсов вы сокостабильной частоты, выход ревер сивного , счетчика, через первую дифференцирующую цепь подключен к нулевым входам первого и третьего триггеров, а единичный вход третьего триггера через вторую диффер енцирующую цепь соединен с единичным выходом второго триггера, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него дополнительно введены два элемента совпадения инвертор и триггер, единичный выход которого соединен с первым входом первого дополнительного элемента совпадения,второй вход которого соединен с входами тактовых импульсов и инвертора, а выход соединен с нулевым входом второго триггера, единичный выход которого соединен с первым входом второго дополнительного элемента совпадения, второй вход которого соединен с выходом инвертора, а выход подключен к единичному входу дополнительного триггера, нулевой вход которого соединен с нулевым выходом второго триггера. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 424311, кл. Н 03 К 5/13, 1974. 2.Авторское свидетельство СССР № 350151, кл. Н 03 К 5/13. 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 1972 |

|

SU350151A1 |

| Отсчетно-измерительное устройство | 1978 |

|

SU746182A1 |

| Формирователь импульсов с линейным изменением периода их следования | 1990 |

|

SU1800640A1 |

| Устройство для синхронизации импульсов | 1985 |

|

SU1325677A1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1990 |

|

SU1723658A2 |

| Устройство для управления тиристорным преобразователем | 1974 |

|

SU516170A1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1594689A1 |

| Синхронизирующее устройство | 1979 |

|

SU792574A1 |

| Устройство для сравнения периодов следования импульсов | 1986 |

|

SU1328932A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

Авторы

Даты

1980-08-23—Публикация

1978-04-24—Подача