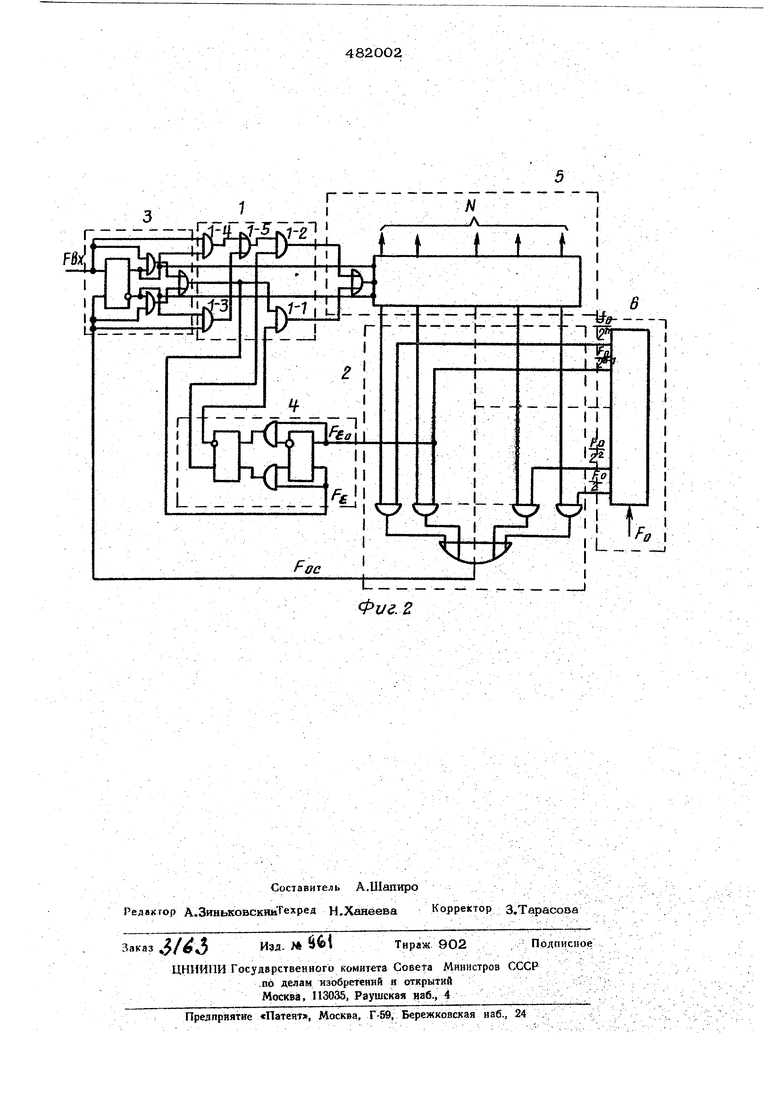

(54) ПРЕОБРАЗСВАТЕЛЬ ЧАСТОТЫ В КОД дервым входом сравнивающего устройства, второй вход которого соединён с npeflnocne ним разрядом делителя частоты. :Изобретение лояснено чертежами. ; На фиг. 1 приведена структурная электрическая схема преобразователя; на фиг, 2 - частично принципиальная электрическа схема преобразователя. Преобразователь частоты в код содержит логический элемент 1, переключающий входные сигналы, который своими входами связан с входом преобразователя частоты в код, с выходом двоичного умножителя 2 с выходами вычитающего устройства 3 и сравнивающего устройства 4, i выход связан с входом реверсивного счетчика 5, Управляющие входы реверсивного счетчика 5 связаны с потенциальными выходами вы читающего устройства 3. Выходы реверсивного счетчика 5, связа ны с входами двоичного умножителя 2, преобразующего код в частоту обратной связи. Другие входы двоичного умножителя 2 соединены с выходами делителя частоты 6 Выход двоичного умножителя 2 соединен с одним из входов вычитающего устройств 3,другой вход KO-ixsporo соединен с входом преобразователя. Выход вычнтающе1Ч) устройства 3 соединен с входом сравнивающего устройства 4,второй вход которого соединен с одним из выходов делителя частоты 6. Блок 1 логических элементов содержит (см. фиг. 2) четыре элемента И ., 1-2, 1-3, и один элемент ИЛИ I-S, ССОД и ценные так, что входы элемента И l связаны с входом нреобразова-геля часючъ в код и с потенциальным выходом вычитающего устройства 3. Входы элемента И 1-3 связаны с выходом двоичного умножителя 2 и с другим потенциальным выходом вычитающего устройства 3. Выходы элементов 1-3 и 1-4 соединены с входами элемента ИЛИ 1-5« Входы элемента И 1-2 соединены с выходом элемента Я ЛИ 1-5 -и с одним из выходов срлвкивающего устройства 4, входы элемента И 1-1 соединены с импульсным DbixoAOM В{;(читс) -устройства 3 и с BTOpbiM нотенниальным выходом сравниваю u(ero устройства 4. Выходы элементов И 1-1 н 1-2 соединены с входом реверсив- ijoix счетчика 5 Г1{к образоватешт частоты в код работает следующим образом. При больм1он ошибке между входным 11 ыходным БОЗДейс-твиями PC Fg элемент Я 1-1 закрыт низким noi-енциалом со сравнивающего устройства 4 и прёоб- J разователь частоты в код разомкнут nt , j ошибке. На вход реверсивного счетчика 5 ноступает входной сигнал или сигнал обратной связи через элемент И 1-2, открытый высоким по-тенциалом с другого выхода сравнивающего устройства 4. Если рассогласование ,/. О , , то на суммирующий вход реверсивного сче-гчика 5 поступают колебания входной частоты через элемент И 1-4, открытый потенциальным выходом вычитающего устройства 3, если рассогласованиеР-Р 0, то на ОАОС вычитающий вход реверсивного счетчика 5 поступают колебания с частоэюй обратной связи с двоичного умнОжктеля 2 через элемент И 1-3, открытый вторым потенциальным выходом вычитающего устройства 3. Импульсами входной частоты или частоты обратной связи набирается на; выходе двоичного умножителя 2 частота, близкая к входной, В этом режиме преобразователь работает, как статический, обладая при этом больЩим быстродействием. Когда ощибка между входной частотой и час1ч гсй обратной связи станет, меньще некоторой наперед заданной малой частоты ff. Fen г тс элемент И 1-1 откроется, а элемент И 1-2 закроется пр -енциалом с выхода сравнивающе1Ю устройства 4, преобразователь замыкается по ощибке и превращается в следящую систему с астатйзмом первого норЯДК4 в установивщемся режиме. Если считать , что нерёхЬд ый процесс заканчивается при переходе преобразовате-; ля в следящий режим, так как воздействие j PC достаточно мало, то наблюдательное . время переходного процесса преобразователя равно , гр « , н т о Получаем вьшгрыщ в быстродействии в In 8 раз. Предмет изобретения Преобразователь частоты в код, содержаихий реверсивный счетчик, двоичный умножит-ель, делитель частоты и вычитающее устройство, причем первый вход вычитающего устройства связан с входом преобразовагеля, а второй вход - с выходом двоичного умножи1-еля, первый выход вычитающеро устройства подк/оочен к знаковому разряду реверсивного счетчика, выходы которого сьъзапы..оцщми входами двоичного умножителя, другие входы двоичного умиожителя соединены с выходами делителя час 1оты, эталоннотчэ генератора, выходы рёверсивно«-ч

,...; . „ , , 5 , , / ,;: ;; -- , ,

счетчика связаны с выходами преобразователе, о т л и ч а ю Щ и Л с я тем, что, с целыр увеличения быстродействия, в него введены сра внивающве устройство и логический авгемейт для яереключевия входных сигналов, входы ко- s тор01Ч) подключены к входу преобразуя-. теля, к выходу, двоичного умноясителя, к , в горому выходу вычитающего у стройства.

к выходу сравнивающего устройства, блока логических элементов связан со счетным входом реверсивного счетчика, второй выход вычитающего устройства свя ; аан с первым входом сравнивающего устройства, второй вход которого соединен с предпоследним разрядом делителя частоты. , ;. . -. . .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1976 |

|

SU661589A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ТЕМПЕРАТУРЫ | 2016 |

|

RU2623196C1 |

| Дискретный электропривод | 1977 |

|

SU809055A1 |

| Дискретный электропривод | 1978 |

|

SU911456A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД С НЕПРЕРЫВНЫМОТСЧЕТОМ | 1971 |

|

SU310383A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД С НЕПРЕРЫВНЫМОТСЧЕТОМ | 1972 |

|

SU337938A1 |

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1403356A1 |

| Дифференцирующе-сглаживающий частотноимпульсный экстраполирующий преобразователь | 1974 |

|

SU532057A1 |

| ВРЕМЯ-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU363990A1 |

fBx

N

5

-ЗР- иг.1 ft f - 1 - П Ipi .j I -1J J L Г

Фvг.

Авторы

Даты

1975-08-25—Публикация

1972-08-11—Подача