(Л С

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1985 |

|

SU1279058A2 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Преобразователь время-код | 1991 |

|

SU1785073A1 |

| Программное устройство для фиксации и документирования времени | 1989 |

|

SU1677691A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ БАЛАНСИРОВКИ РЕЗОНАТОРА ТВЕРДОТЕЛЬНОГО ВОЛНОВОГО ГИРОСКОПА ЛУЧОМ ЛАЗЕРА | 1993 |

|

RU2079107C1 |

Изобретение может быть использовано для восстановления и синтеза частот в системах автоматики и обработки данных, а также в измеритель ных устройствах. Умножитель частоты с следования импульсов содержит фазовый детектор , элементы И 2,3, реверсивный счетчик 12, триггеры 9, 20, инверторы 8,10,19, регистр 13 хранения, цифроаналоговый преобразователь 14, генератор 15 импульсов, делитель 6 частоты, деоичный счетик 7, элемент ИЛИ 4, формирователи 17, 18 выходную и входную шины 16 и 21 соответственно, Умножитель частоты имеет првьшенные точность отработки фазы выходного сигнала и надежность J з.п. ф-лы, 2 ил.

Од

00 сд

О5

Изобретение относится к импульсной технике и может быть использовано для восстановления и синтеза частот в системах автоматики и обработки данных, а также в измерительных устройствах.

Целью изобретения является повыше ние точности отработки фазы выходного сигнала и повьшение надежности устрой ства путем запрета подстройки фазы выходного сигнала в заданном интер- :вале ее отклонений, формирования импульсов, подаваемых на входы фазового детектора, с малыми передними фрон тами, повышения точности фазового детектора и устранения помех на его выходах.

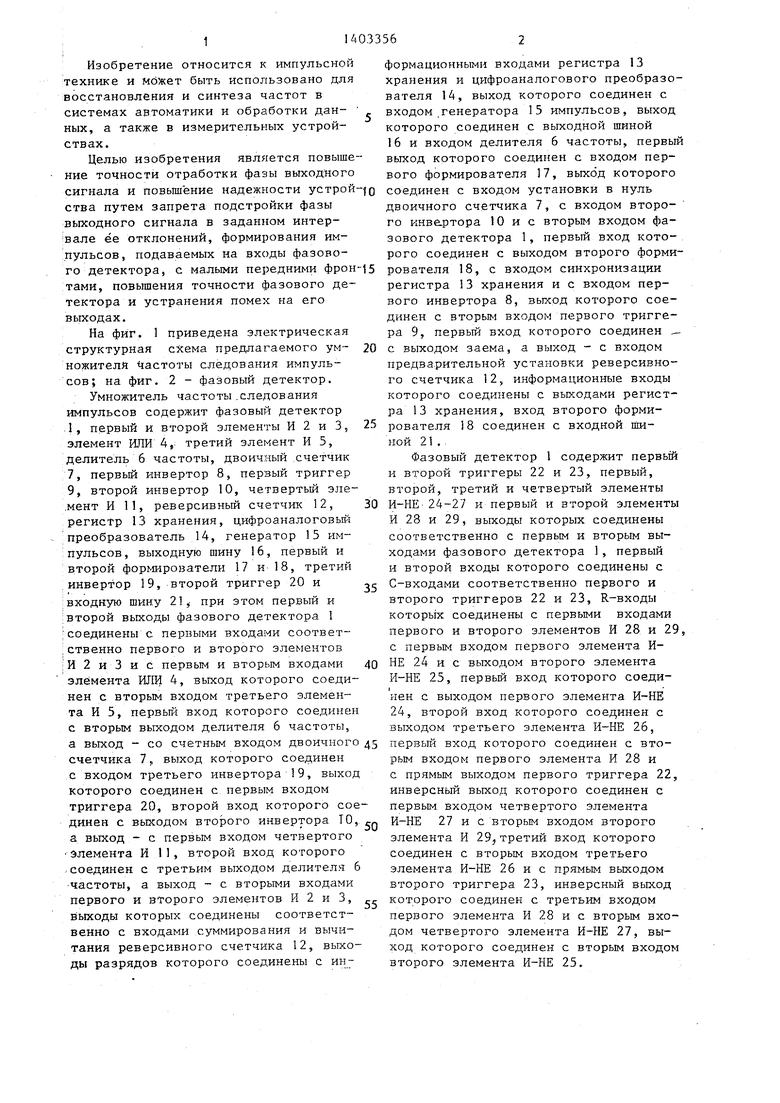

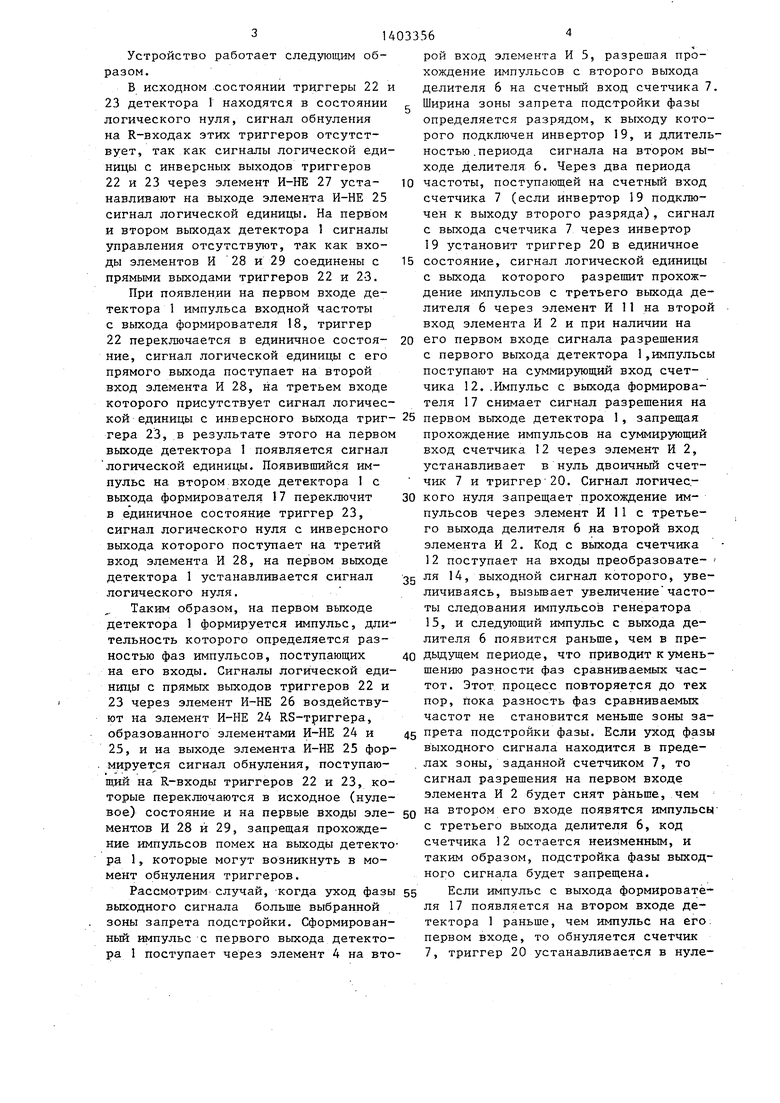

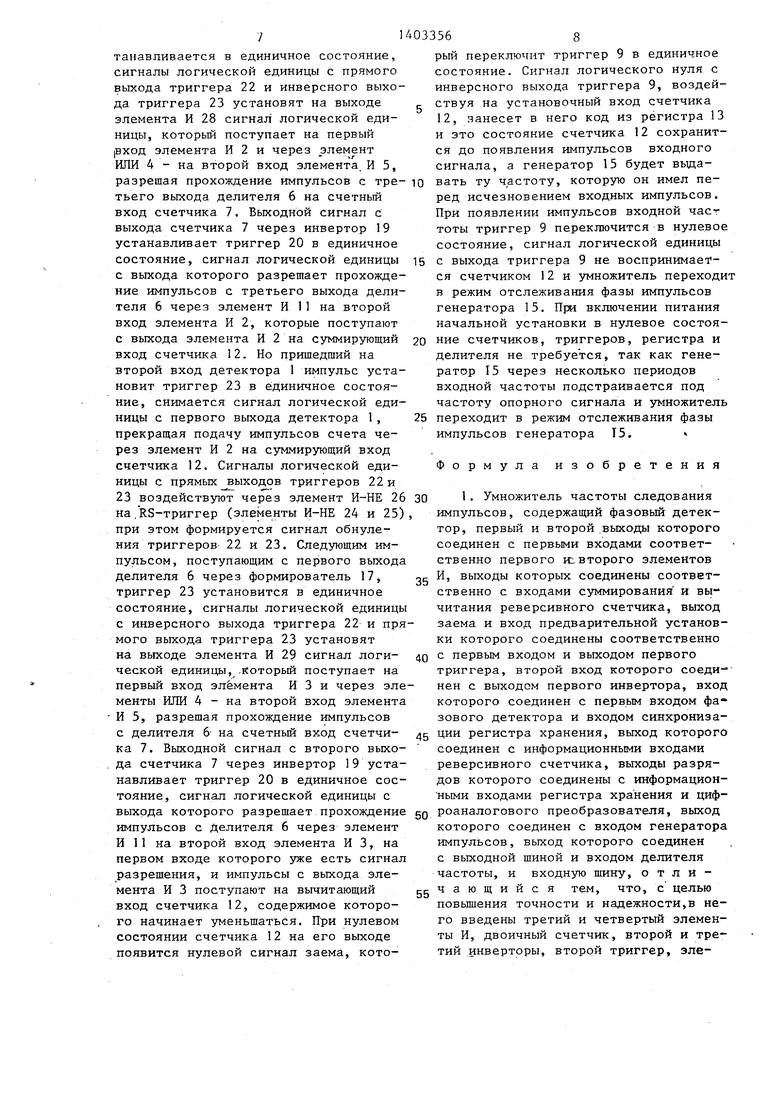

На фиг. 1 приведена электрическая структурная схема предлагаемого умножителя частоты следования импульсов; на фиг. 2 - фазовый детектор.

Умножитель частоты .следования импульсов содержит фазовый детектор .1, первый и второй элементы И 2 и 3, элемент ИЛИ А, третий элемент И 5, делитель 6 частоты, двоичный .счетчик 7, первый инвертор 8, первый триггер 9, второй инвертор 10, четвертый эле- .мент И 11, реверсивный счетчик 12, регистр 13 хранения, цифроаналоговый преобразователь 14, генератор 15 им- :пульсов, выходную шину 16, первый и второй формирователи 17 и 18, третий инвертор 19, второй триггер 20 и : входную шику 21,- при этом первый и :второй выходы фазового детектора 1 соединены с. первыми входами соответ- ственно первого и второго элементов ;И 2 и 3 и с первым и вторым входами элемента МИ 4, выход которого соединен с вторым входом третьего элемента И 5, первый вход которого соединен с вторым выходом делителя 6 частоты, а выход - со счетным входом двоичного счетчика 7., выход которого соединен с входом третьего инвертора 19, выход которого соединен с первым входом триггера 20, второй вход которого сое динан с вьпсодом второго инвертора ТО, а выход - с первым входом четвертого элемента И 11, второй вход которого соединен с третьим выходом делителя 6 частоты, а выход - с вторыми входами первого и второго элементов И 2 и 3, выходы которых соединены соответственно с входами суммирования и вычитания реверсивного счетчика 12, выходы разрядов которого соединены с ин

формационными входами регистра 13 хранения и цифроаналогового преобразователя 14, выход которого соединен с с входом .генератора 15 импульсов, выход которого соединен с выходной шиной 16 и входом делителя 6 частоты, первый выход которого соединен с входом первого формирователя 17, выход которого

to соединен с входом установки в нуль

двоичного счетчика 7, с входом второ- го инвертора 10 и с вторым входом фазового детектора 1, первый вход кото- , рого соединен с выходом второго форми- 5 рователя 18, с входом синхронизации регистра 13 хранения и с входом первого инвертора 8, выход которого соединен с вторым входом первого триггера 9, первый вход которого соединен

0 с выходом заема, а выход - с входом предварительной установки реверсивного счетчика 12, информационные входы которого соединены с выходами регистра 13 хранения, вход второго форми5 рователя 18 соединен с входной шиной 21 . .

Фазовый детектор 1 содержит первьй и второй триггеры 22 и 23, первый, второй, третий и четвертый элементы

0 И-НЕ 24-27 и первый и второй элементы И 28 и 29, выходы которых соединены соответственно с первым и вторьм выходами фазового детектора 1, первый и второй входы которого соединены с

5 С-входами соответственно первого и второго триггеров 22 и 23, R-входы которых соединены с первыми входами первого и второго элементов И 28 и 29, с первым входом первого элемента И0 НЕ 24 и с выходом второго элемента И-НЕ 25, первьй вход которого соединен с выходом первого элемента И-НЕ 24, второй вход которого соединен с выходом третьего элемента И-НЕ 26,

5 первьш вход которого соединен с вторым входом первого элемента И 28 и с прямым выходом первого триггера 22, инверсньш выход которого соединен с первым входом четвертого элемента И-НЕ 27 и с вторым входом второго элемента И 29 третий вход которого соединен с вторым входом третьего элемента И-НЕ 26 и с прямым выходом второго триггера 23, инверсный выход

j которого соединен с третьим входом первого элемента И 28 и с вторым входом четвертого элемента И-НЕ 27, выход которого соединен с вторым входом второго элемента И-НЕ 25.

0

Устройство работает следующим образом.

В исходном состоянии триггеры 22 и 23 детектора 1 находятся в состоянии логического нуля, сигнал обнуления на R-входах этих триггеров отсутствует, так как сигналы логической единицы с инверсных выходов триггеров 22 и 23 через элемент И-НЕ 27 устанавливают на выходе элемента И-НЕ 25 сигнал логической единицы. На первом и втором выходах детектора 1 сигналы управления отсутствуют, так как входы элементов И 28 и 29 соединены с прямыми выходами триггеров 22 и 2-3.

При появлении на первом входе детектора 1 импульса входной частоты с выхода формирователя 18, триггер 22 переключается в единичное состояние, сигнал логической единицы с его прямого выхода поступает на второй вход элемента И 28, на третьем входе которого присутствует сигнал логической единицы с инверсного выхода триг- 25 первом выходе детектора 1, запрещая гера 23, в результате этого на первом прохождение импульсов на суммирзтащий

выходе детектора 1 появляется сигнал логической единицы. Появившийся импульс на втором входе детектора 1 с выхода формирователя 17 переключит в единичное состояние триггер 23, сигнал логического нуля с инверсного выхода которого поступает на третий вход элемента И 28, на первом выходе детектора 1 устанавливается сигнал логического нуля.

Таким образом, на первом выходе детектора 1 формируется импульс, длительность которого определяется разностью фаз импульсов, поступающих на его входы. Сигналы логической единицы с прямых вькодов триггеров 22 и 23 через элемент И-НЕ 26 воздействуют на элемент И-НЕ 24 RS-триггера, образованного элементами И-НЕ 24 и 25, и на выходе элемента И-НЕ 25 фор- мируется сигнал обнуления, поступающий на R-входы триггеров 22 и 23, которые переключаются в исходное (нулевое) состояние и на первые входы элементов И 28 и 29, запрещая прохождение импульсов помех на выходы детектора 1, которые могут возникнуть в момент обнуления триггеров.

Рассмотрим случай, когда уход фазы 55 выходного сигнала больше выбранной зоны запрета подстройки. Сформированный импульс с первого выхода детектора 1 поступает через элемент 4 на вто

30

25

40

45

50

рой вход элемента И 5, разрешая прохождение импульсов с второго выхода делителя 6 на счетный вход счетчика 7.

Ширина зоны запрета подстройки фазы определяется разрядом, к выходу которого подключен инвертор 19, и длительностью .периода сигнала на втором выходе делителя 6. Через два периода

частоты, поступающей на счетный вход счетчика 7 (если инвертор 19 подключен к выходу второго разряда), сигнал с выхода счетчика 7 через инвертор 19 установит триггер 20 в единичное

состояние, сигнал логической единицы с выхода которого разрешит прохождение импульсов с третьего выхода делителя 6 через элемент И 11 на второй вход элемента И 2 и при наличии на

его первом входе сигнала разрешения с первого выхода детектора 1,импульсы поступают на суммирующий вход счетчика 12,.Импульс с выхода формирователя 17 снимает сигнал разрешения на

вход счетчика 12 через элемент И 2, устанавливает в нуль двоичный счет- чик 7 и триггер 20. Сигнал логического нуля запрещает прохождение импульсов через элемент И 11 с третьего выхода делителя 6 на второй вход элемента И 2. Код с выхода счетчика 12 поступает на входы преобразовате-

ля 14, выходной сигнал которого, увеличиваясь, вызьюает увеличение частоты следования импульсов генератора 15, и следующий импульс с выхода делителя 6 появится раньше, чем в предьщущем периоде, что приводит к уменьшению разности фаз сравниваемых частот. Этот процесс повторяется до тех пор, пока разность фаз сравниваемых частот не становится меньше зоны запрета подстройки фазы. Если уход фазы выходного сигнала находится в пределах зоны, заданной счетчиком 7, то сигнал разрешения на первом входе элемента И 2 будет снят раньше, чем на втором его входе появятся импульсы с третьего выхода делителя 6, код счетчика 12 остается неизменным, и таким образом, подстройка фазы выходного сигнала будет запрещена.

Если импульс с выхода формирователя 17 появляется на втором входе детектора 1 раньше, чем импульс на его; первом входе, то обнуляется счетчик 7, триггер 20 устанавливается в нуле

514033566

вое состояние (если он находился в снят, на втором его входе не появят- .единичном состоянии), триггер 23 де- ся импульсы с третьего выхода дели- тектора 1 переключается в единичное теля 6, код счетчика 12 останется состояние, на втором выходе устанав- неизменным. Таким образом, подстройка лйвается сигнал логической единицы, фазы выходного сигнала запрещена, а при появлении импульса на первом По каждому импульсу входной часто- входе детектора 1 триггер 22 также ты в регистр 13 заносится выходной переключается в единичное состояние, код счетчика 12, триггер 9 -устанавли- сигнал на втором выходе фазового де- ю вается в нулевое состояние, сигнал ло- тектора 1 становится равным логичес- гической единицы с инверсного выхода кому нулю, в результате чего на вто- которого не воспринимается счетчиком ; ром выходе детектора 1 формируется 2 и устройство работает так, как бы- импульс, длительность которого опре- ° описано ранеее. При пропадании им- деляется разностью фаз импульсов, 15 пульсов входного сигнала на первом поступающих на входы детектора |. Сиг- входе детектора 1 триггер 23 переклю- .нал обнуления воздействует на R-входы чается в единичное состояние импуль- триггеров 22 и 23, детектор 1 возвра- ° по второму входу, сигналы логи- щается в исходное состояние.ческой единицы с прямого выхода тригРассмотрим случай, когда уход фазы 20 Р 23 и инверсного выхода триггера выходного-сигнала больше выбранной 22 воздействуют на входы элемента И зоны запрета. Сформированный импульс 29, на выходе которого формируется с второго выхода детектора 1 поступа- сигнал логической единицы, который ет через элемент ИЛИ 4 на второй вход поступает на первый вход элемента элемента И 5, разрешая прохождение 25 И 3 и через элемент ИЛИ 4 на второй (импульсов с второго выхода делителя 6 вход элемента И 5, разрёщая прохожде- на счетный вход счетчика 7, через .ние импульсов с выхода делителя 6 на- два периода сигнал с выхода счетчика счетный вход счетчика 7. Выходной 7 через инвертор 19 установит триггер сигнал с выхода счетчика 7 через ин- 20 в единичное состояние, сигнал ло- ЗО рертор 19 устанавливает триггер 20 гической единицы с выхода которого в единичное состояние, сигнал логи-:- разрешает прохождение импульсов с тре- ческой единицы с выхода которого раз- Чьего выхода делителя 6 через эле- решает прохождение импульсов- с мент И 1 1 на второй вход элемента ИЗ,, третьего выхода делителя 6 через эле- при наличии сигнала разрешения с вто- g мент И 11 на второй вход элемента И рого выхода детектора 1 на первом 3, на первом входе которого уже есть Iвходе элемента И 3 импульсы поступают сигнал разрешения. Импульсы с выхода }на вычитающий вход счетчика 12. Им- элемента И 3 поступают на вычитающий :пульс с вьсхода формирователя 18 сни- вход счетчика 12, содержимое которого ;мает сигнал разрешения на второй вы- 40 уменьшаться. При нулевом сос- 1ходе детектора 1, запрещая прохожде- тоянии счетчика 12 на его выходе по- ние импульсов на вычитающий вход счет- явится нулевой сигнал заема, которьй чика 12 через элемент И 3. Код с вы- переключит триггер 9 в единичное сос- хода счетчика 12 поступает на входы . тояние. Сигнал логического нуля с преобразователя 14, выходной сигнал вькоца триггера 9, воздействуя на ус- которого изменяясь вызьшает уменьше- тановочный вход счетчика 12, занесет ние частоты следования импульсов ге- него код из регистра 13, записанный нератора 15, следующий импульс с вы- в него последним импульсом входной хода-делителя 6 появится позже, чем частоты, и это состояние счетчика 12 в предьщущем случае, что приводит к 50 до появления импульсов уменьшению разности фаз сравниваемых входного сигнала, а генератор 15 бу- частот. Этот процесс продолжается до вьздавать ту частоту, которую он тех пор, пока разность фаз сравнивае- имел перед исчезновением входного сиг- мых не становится меньше зоны нала, запр.ета подстройки фазы.55 Если, например, появится ложный

Если фазы выходного сигнала импульс на шине 21, в регистр 13 за- находится в пределах зоны, заданной носится выходной код счетчика 12, счетчиком 7, то сигнал разрешения триггер 9 устанавливается в нулевое на первом входе элемента И 3 будет состояние, триггер 22 детектора 1 ус7

танавливается в единичное состояние, сигналы логической единицы с прямого выхода триггера 22 и инверсного выхода триггера 23 установят на выходе элемента И 28 сигнал логической единицы, который поступает на первый |вход элемента И 2 и через ИЛИ 4 - на второй вход элемента, И 5,

разрешая прохождение импульсов с тре- ю вать ту частоту, которую он имел петьего выхода делителя 6 на счетный вход счетчика 7. Выходной сигнал с выхода счетчика 7 через инвертор 19 устанавливает триггер 20 в единичное состояние, сигнал логической единицы с выхода которого разрешает прохождение импульсов с третьего выхода делителя 6 через элемент И 11 на второй вход элемента И 2, которые поступают

ред исчезновением входных импульсов. При появлении импульсов входной част тоты триггер 9 переключится в нулевое состояние, сигнал логической единицы 15 с выхода триггера 9 не воспринимается счетчиком 12 и умножитель переходит в режим отслеживания фазы импульсов генератора 15. При включении питания начальной установки в нулевое состоя- с выхода элемента И 2 на суммирующий 20 ие счетчиков, триггеров, регистра и вход счетчика 12. Но пришедший на делителя не требуется, так как геневторой вход детектора 1 импульс установит триггер 23 в единичное состояние, снимается сигнал логической единицы с первого выхода детектора 1, прекращая подачу импульсов счета через элемент И 2 на сз ммирующий вход счетчика 12. Сигналы логической единицы с прямых выходов триггеров 22 и 23 воздействуют через элемент И-НЕ 26 30 наДЗ-триггер (элементы И-НЕ 24 и 25), при этом формируется сигнал обнуления триггеров 22 и 23. Следующим импульсом, поступающим с первого выхода делителя 6 через формирователь 17, триггер 23 установится в единичное состояние, сигналы логической единицы с инверсного выхода триггера 22 и прямого выхода триггера 23 установят на выходе элемента И 29 сигнал логи- 0 ческой единицы, .который поступает на первый вход элемента И 3 и через элементы ИЛИ 4 - на второй вход элемента И 5, разрешая прохождение импульсов с делителя 6- на счетньй вход счетчи25

2g

45

ка 7. Выходной сигнал с второго выхода счетчика 7 через инвертор 19 устанавливает триггер 20 в единичное состояние, сигнал логической единицы с

выхрда которого разрешает прохождение gQ роаналогового преобразователя, выход импульсов с Делителя 6 чере:з элемент И 11 на второй вход элемента И 3, на первом входе которого уже есть сигнал разрешения, и импульсы с выхода элемента И 3 поступают на вычитающий gg вход счетчика 12, содержимое которого начинает уменьшаться. При нулевом состоянии счетчика 12 на его выходе появится нулевой сигнал заема, котокоторого соединен с входом генератора импульсов, выход которого соединен с выходной шиной и входом делителя частоты, и входную шину, отличающийся тем, что, с целью повьш1ения точности и надежности,в него введены третий и четвертый элементы И, двоичный счетчик, второй и третий инверторы, второй триггер, элеA033568

рый переключит триггер 9 в единичное состояние. Сигнал логического нуля с инверсного выхода триггера 9, воздействуя на установочный вход счетчика 12, занесет в него код из регистра 13 и это состояние счетчика 12 сохранится до появления импульсов входного сигнала, а генератор 15 будет въща

ратор 15 через несколько периодов входной частоты подстраивается под частоту опорного сигнала и умножитель переходит в режим отслеживания фазы импульсов генератора 15,

Формула изобретения

И, выходы которых соединены соответственно с входами суммирования и вычитания реверсивного счетчика, выход заема и вход предварительной установки которого соединены соответственно с первым входом и выходом первого триггера, второй вход которого соеди нен с выходом первого инвертора, вход которого соединен с первым входом фазового детектора и входом синхрокизации регистра хранения, выход которого соединен с информационными входами реверсивного счетчика, выходы разрядов которого соединены с информацион- ньми входами регистра хранения и цифроаналогового преобразователя, выход

которого соединен с входом генератора импульсов, выход которого соединен с выходной шиной и входом делителя частоты, и входную шину, отличающийся тем, что, с целью повьш1ения точности и надежности,в него введены третий и четвертый элементы И, двоичный счетчик, второй и третий инверторы, второй триггер, элемент ИЛИ, первый, и второй формирователи, вход последнего из которых сое- Динен с входной шиной, выход - с пер- йым входом фазового детектора, второй вход которого соединен с входом рого инвертора, с входом установки в о двоичного счетчика и выходом первого формирователя, вход которого соединен с первым выходом делителя частоты, второй выход которого соединен с первым входом третьего элемента И,, второй вход которого соединен Ь выходом элемента ИЛИ, выход - с йчетньм входом двоичного счетчика, : ьгход которого соединен с входом тре- Тьего инвертора, выход которого сое- ;инен с первым входом второго триггера, второй вход которого соединен с выходом второго инвертора, выход - с Первым входом четвертого элемента И, второй вход которого соединен с тре- в кодом делителя частоты, а выход - с вторыми входами первого и Йторого элементов И, первые входы Которых соединены соответственно с первым и вторым входами элемента ИЛИ.

триггеры, первый, второй, третий и четвертый элементы И-НЕ и первый и второй элементы И, выходы которых соединены соответственно с первым и вторым выходами фазового детектора, первый и второй входы которого соединены с С-входами соответственно первого и второго триггеров, П-входы которьгх соединены с шиной логической единиды, R-входы - с первыми входами первого и второго элементов И, с первым вхо дом первого элемента И-НЕ и выходом второго элемента И-НЕ, первый

вход которого соединен с выходом первого элемента И-НЕ, второй вход которого соединен с выходом третьего элемента И-НЕ, первьй вход которого соединен с вторым входом первого элемента И и прямым выходом первого триггера, инверсньш выход которого соединен с первым входом четвертого элемента И-НЕ и вторым входом второго элемента И, третий вход которого соединен

с вторым входом третьего элемента И-НЕ и прямым выходом второго триггера, инверсный выход которого соединен с. третьим входом первого элемента И и вторым входом четвертого элемента ИНЕ, выход которого соединен с вторым входом второго элемента И-НЕ.

| Умножитель частоты следования импульсов | 1983 |

|

SU1119165A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1279058A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-15—Публикация

1986-11-27—Подача