Известен преобразователь частоты в жод, содержащий реверсивный счетчик, двоичный умножитель с делителем частоты, вычитающее устройство.

Однако, при широком диапазоне входных частот увеличивается объем оборудования и инерционность устройства.

Цель изобретения - сокращение объема оборудования при широком диапазоне Преобразуемых частот.

Это достигается тем, что реверсивный счетчик устройства разделен на две части, выходы т младших его разрядов соединены со входами вентилей первого двоичного умножителя, выходы р старших разрядов через дешифратор соединены с входами вентилей второго двоичного умножителя, выход которого подключен к входу делителя частоты и через второе устройство синхронизации - к одному входу схемы запрета, другой вход которой соединен с нулевой выходной шиной дешифратора, а выход - со входом сборки.

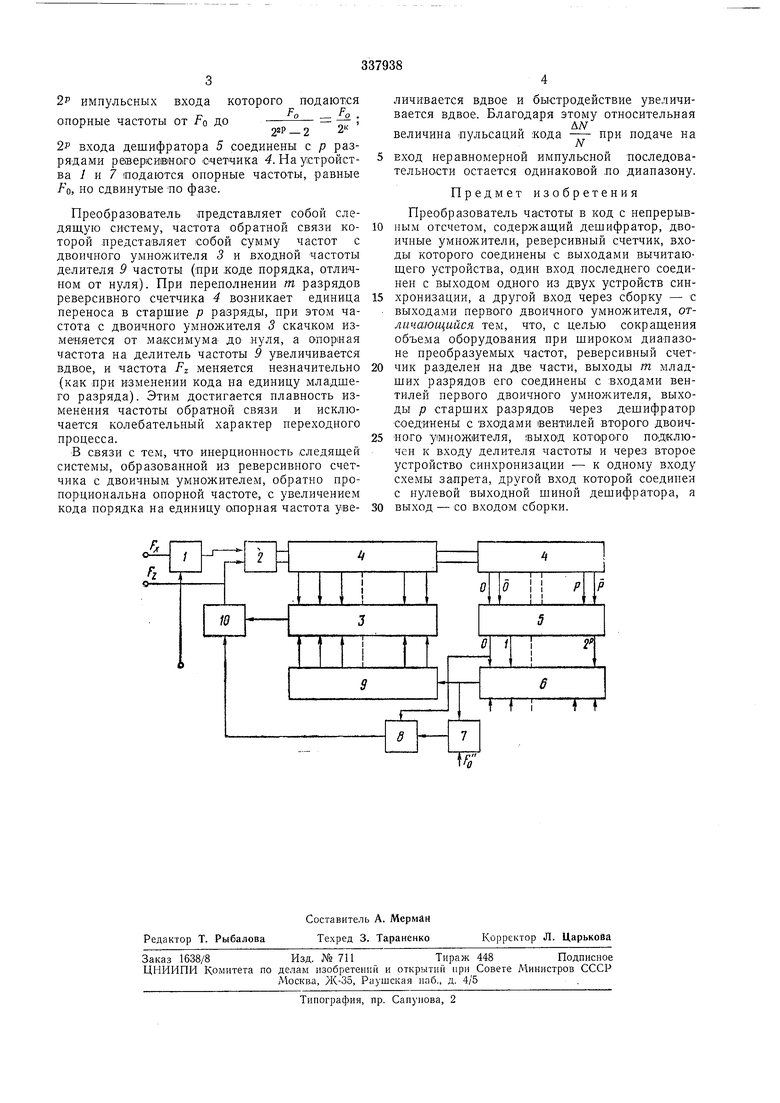

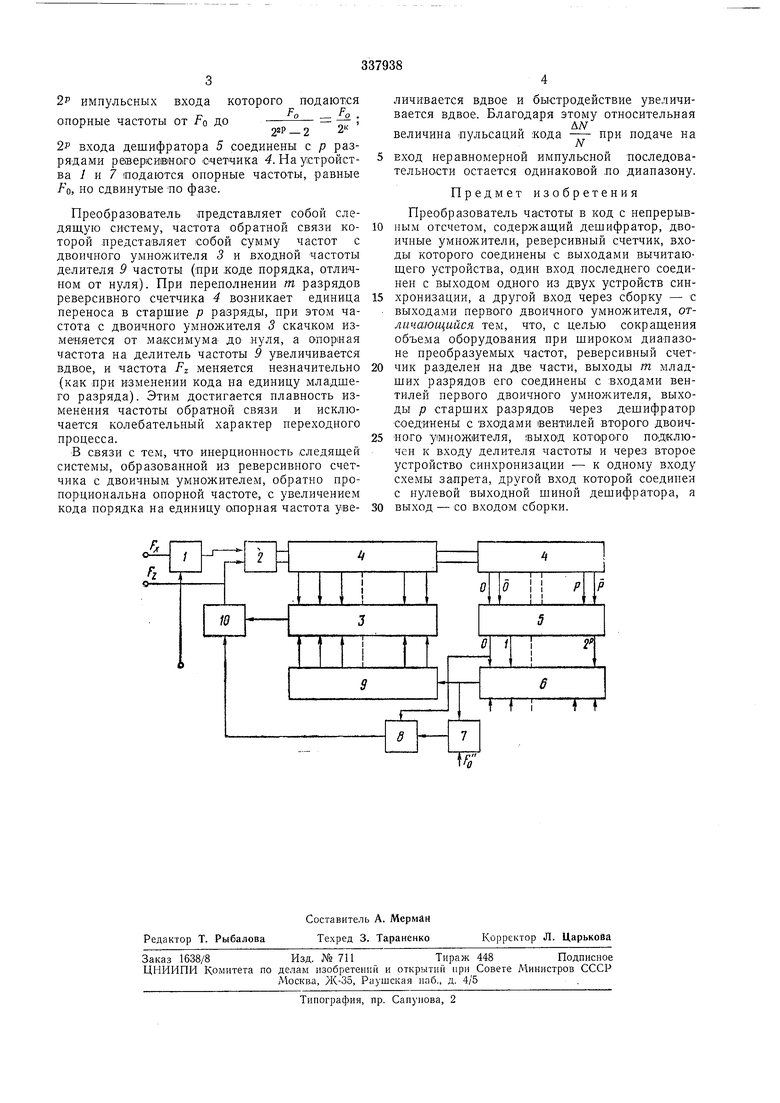

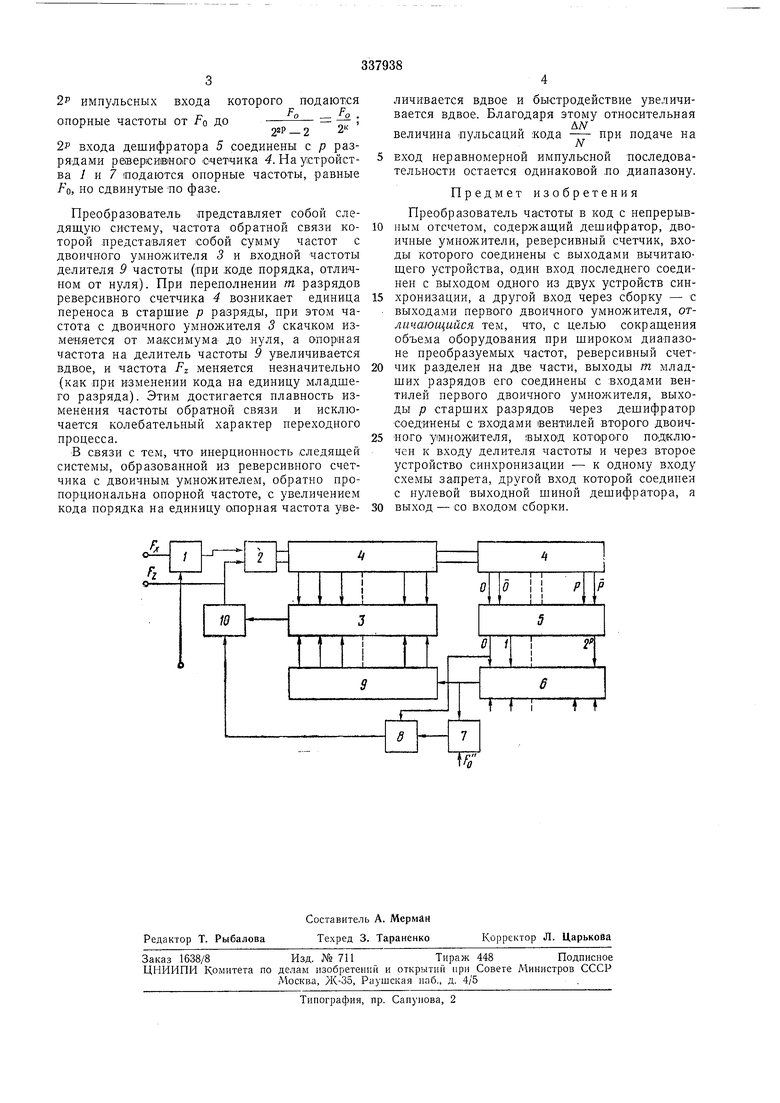

На чертеже приведена блок-схема преобразователя.

Преобразователь состоит из устройства / синхронизации входной частоты, вычитающего устройства 2, вентилей двоичного умножителя 3 мантиссы, (от+р)-разрядного реверсивного счетчика 4, дешифратора 5 порядка на 2 р входов и 2Р выходов, вентилей двоичного

умножителя 6 опорных частот, устройства 7 синхронизации, схемы 8 запрета, делителя 9 частоты мантиссы, сборки 10.

Основной частью преобразователя является (m-j-/;)-разрядный реверсивный счетчик 4. На вход «--|- ючетчика через вычитающее устройство 2 и устройство / ринхронизации подключена измеряемая частота РХ, на вход «- счетчика через вычитающее устройство 2 частота обратной связи fz со сборки 10. Один вход сборки 10 соединен с выходом вентилей двоичного умножителя 3, другой вход -- с выходом схемы 8. Потенциальные входы вентилей двоичного умножителя 3 соединены с единичными выходами т младших разрядов реверсивного счетчика 4. Импульсные входы вентилей двоичного умиожителя 3 соединены с единичными выходами делителя 9 частоты, вход делителя 9 частоты с выходом вентилей двоичного умножителя 6 опорных частот. Кроме того, выход вентилей двоилного умвожителя 6 опорных частот через устройство 7 синхро-низации соединен с импульсным входом схемы 8, потенциальный вход, который соединен с нулевой выходной шиной дешифратора 5 по,ряд:ка; выходных шины дешифратора 5 связаны с потенциальными входами двоичного умножителя 6 опорных частот на

2

которого подаются

импульсных

входа

опорные частоты от FQ до- ,

- 2 2

2Р входа дешифратора 5 соединены с р разрядами ре(Вер1СИ1В НО|Го счетчика 4. На устройства 7 и 7 (подаются опорные частоты, равные РО, но сдвинутые по фазе.

Преобразователь представляет собой следящую систему, частота обратной связи которой представляет собой сумму частот с двоичного умножителя 3 и входиой частоты делителя 9 частоты (при .коде порядка, отличном от нуля). При переполнении m разрядов реверсивного счетчика 4 возникает единица переноса в старшие р разряды, при этом частота с двоичного умножителя 5 скачком изменяется от максимума до .нуля, а о-пор1ная частота на делитель частоты 9 увеличивается вдвое, и частота FZ меняется незначительно (как при изменении кода на единицу мла.дшего разряда). Этим достигается плавность изменения частоты обратной связи и исключается колебательный характер переходного процесса.

В связи с тем, что инерционность следящей системы, образованной из реверсивного счетчика с двоичным умножителем, обратно пропорциональна опорной частоте, с увеличением кода порядка на единицу опорная частота увеличивается вдвое и быстродействие увеличивается вдвое. Благодаря этому относительная

длг

величина пульсации кода при подаче на

TV

вход неравномерной импульсной последовательности остается одинаковой .по диапазону.

Предмет изобретения

Преобразователь частоты в код с непрерьшным отсчетом, содержащий дешифратор, двоичные умножители, реверсивный счетчик, входы которого соединены с выходами вычитающего устройства, один вход последнего соединен с выходом одного из двух устройств синхронизации, а другой вход через сборку - с выходами первОГО двоичного умножителя, отличающийся тем, что, с целью сокращения объема оборудования при широком диапазоне преобразуемых частот, реверсивный счетчик разделен на две части, выходы т младших разрядов его соединены с входами вентилей первого двоичного умнол ителя, выходы р старших разрядов через дешифратор соединены с входами вентилей второго двоич«ого умножителя, выход KOTOiporo подключен к входу делителя частоты и через второе устройство синхронизации - к одному входу схемы запрета, другой вход которой соединен с нулевой выходной шиной дешифратора, а

выход-со входом сборки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД | 1972 |

|

SU426318A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

| Синхронный фильтр | 1983 |

|

SU1131028A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД С НЕПРЕРЫВНЫМОТСЧЕТОМ | 1971 |

|

SU310383A1 |

| Устройство для вычисления логарифмов | 1972 |

|

SU479110A1 |

| Устройство для отображения информации | 1972 |

|

SU458004A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Устройство для контроля метрологических характеристик средств измерений | 1982 |

|

SU1117592A1 |

| ЧАСТОТНО-ИМПУЛЬСНАЯ СЛЕДЯЩАЯ СИСТЕМА | 1973 |

|

SU372543A1 |

| Устройство для вычисления логарифмической функции | 1980 |

|

SU930314A1 |

Даты

1972-01-01—Публикация