граммы формирования компенсирующего напряжения.

Входной сигнал представляют в виде суммы постоянной составляющей f/o и синусоидального сигнала U sin ш/, а выходной как

,x , и, sin (ш/ + ) + Ки,, (/),

где /С - коэффициент передачи линейной

цепи; Ф - угол сдвига фаз между входным

и выходным сигналами; Удр(/) -приведенный к входу линейной цепи источник напряжения дрейфа.

Для компенсации сигнала дрейфа К Uxp(t) постоянной составляющей вырабатывают на протяжении п циклов компенсации уровень напряжения постоянного тока UK n-UcT± + UCT, противоположной по знаку и равный по величине К дрГО с точностью, определяемой дискретностью установки компенсирующего напряжения, где УСТ - уровень дискретности; UK - уровень напряжения компенсации.

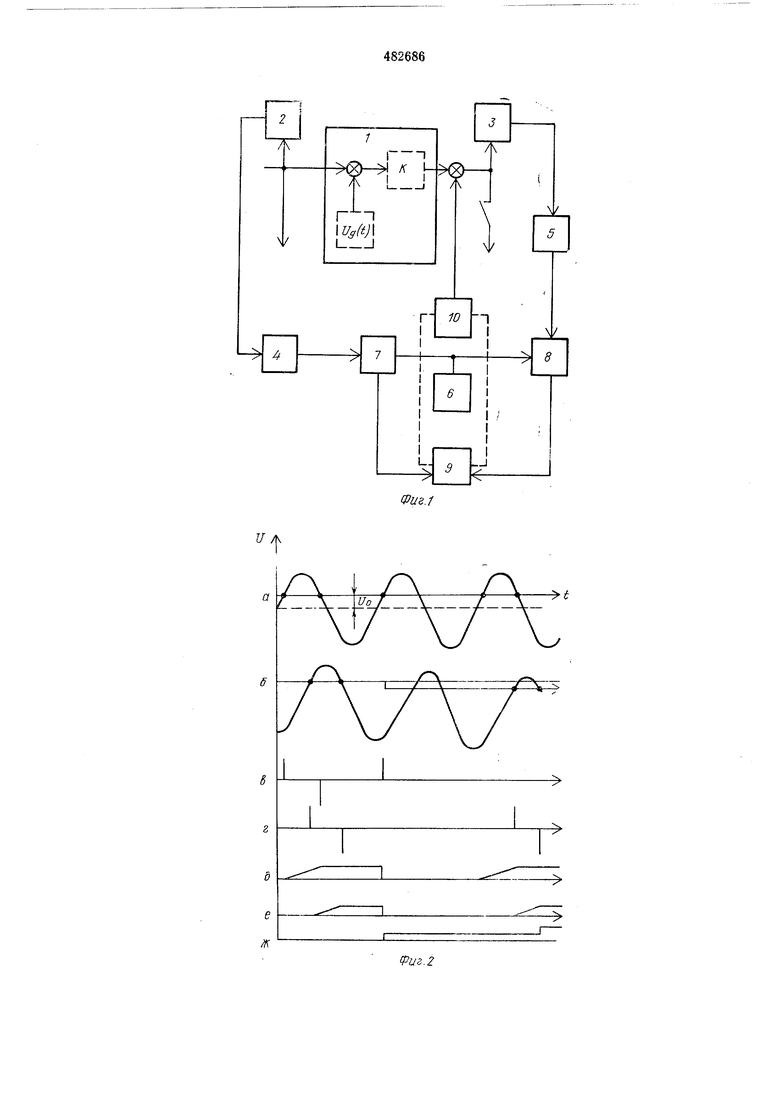

Синусоидальный сигнал с постоянной составляющей, не зависящей от времени, (фиг. 2,а) пропускают через линейную цепь 1 с дрейфом, представляющую собой идеализированную линейную цепь без дрейфа, и приведенный к вхолТ,у линейной цепи источник напряжения суммарного дрейфа. Выходной сигнал линейной цепи (фиг. 2,6), содержащий постоянную составляющую, изменяющуюся во времени, так же, как и входной сигнал линейной цепи одновременно усиливают, ограничивают, дифференцируют в блоках 2, 3, затем с помощью логической схемы 4 выделяют временной интервал, заключенный между временными отметками в моменты перехода входного сигнала через нуль (фиг. 2,в). Аналогично выделяют второй временной интервал (фиг. 2,г) с помощью логической схемы б, соответствующий выходному сигна;) линейной цепи.

В сформированные временные интервалы интегрируют эталонный сигнал, полученный от источника 6 стабилизированного нанряжения постояпного тока при помощи, например, двух электронно-аналоговых интеграторов 7, 8 (фиг. 2,д, е). После окончания интегрирования интеграторы 7, 8 переводят из режима интегрирования в режим запоминания и одновременно производят вычитание уровня выходного напряжения интегратора 8 из уровня выходного напряжения интегратора 7,

сравнение полученной разности с нулевым уровнем.

При неравенстве полученной разности нзлю формируют дискретную ступеньку напряжеПИЯ при помощи блока 9 и источника 10 компенсирующего напряжения, механически управляемого от блока 9 (фиг. 2,ж}.

При достижении нулевой разницы выходных напряжений интеграторов 7, 8 выдают команду на подключение выходного сигнала линейной цепи к входу измерителя сдвига фаз и продолжают выполнять описанные выще операции до окончания измерения.

Предмет изобретения

Способ динамической компенсации дрейфа постоянной составляющей низкочастотного синусоидального сигнала после прохождения

его через линейную цепь с источпиком дрейфа путем усиления, ограничения входного и выходного сигналов линейной цепи, дифференцирования сигналов, полученных после ограничения, и получения временных отметок в моменты перехода синусоидальных сигналов через нуль, отличающийся тем, что, с делыо повыщепия точности измерения фазового сдвига двух синусоидальных сигналов, интегрируют эталонный сигнал в интервалы

времени, определяемые временными отметками, полученными при переходе через нуль синусоидальными сигналами на выходе и входе линейной цепи с источником дрейфа, запоминают достигнутые в результате интегрирования уровни напряжений, вычитают уровень напряжения, полученный после интегрирования эталонного сигнала в интервалы времени, соответствующие переходу синусоидальных напряжений через нуль, определяемый

выходным сигналом линейной цепи, из аналогичпо полученного уровня напряжения, соответствующего входному сигналу, формируют, при отличии полученной разности от нуля, дискретный уровень компенсирующего напряжения постоянного тока со знаком, противоположным полученной разности напряжения, суммируют дискретный уровень компенсирующего напряжения с выходным сигналом линейной цепи, производят операции интегрирования, запоминания, вычитания формирования и суммирования до тех пор, пока разность напряжения после вычитания не станет равной нулю, выдают сигнал на измерение и продолжают выполнять операции интегрирования, запоминания, вычитания и формирования до конца измерений.

I Г

/л

/

u(t)

/

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Детектор квазиравновесия (его варианты) | 1981 |

|

SU1012191A1 |

| Способ импульсно-фазового управления вентильным преобразователем | 1977 |

|

SU769698A2 |

| Устройство для контроля процесса нанесения покрытий | 1989 |

|

SU1682783A1 |

| УСТРОЙСТВО для КОМПЕНСАЦИИ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ | 1972 |

|

SU343272A1 |

| ВОЛОКОННО-ОПТИЧЕСКИЙ ИЗМЕРИТЕЛЬ УГЛОВОЙ СКОРОСТИ | 1994 |

|

RU2112927C1 |

| Интегрирующий преобразователь постоянного напряжения вов временной интервал | 1970 |

|

SU734875A1 |

| СПОСОБ АВТОМАТИЧЕСКОГО РЕГУЛИРОВАНИЯ АСТАТИЧЕСКОГО ОБЪЕКТА | 1996 |

|

RU2103714C1 |

| Запоминающее устройство | 1980 |

|

SU926719A1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ ВО ВРЕМЕННОЙ ИНТЕРВАЛ | 1990 |

|

RU2018137C1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ ВО ВРЕМЕННОЙ ИНТЕРВАЛ | 1990 |

|

RU2018136C1 |

L.

iI .

Авторы

Даты

1975-08-30—Публикация

1973-04-16—Подача