1

Устройство относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств дискретной автоматики и контроля.

Известны устройства для сравнения двоичных чисел, содержащие регистр. Выходы разрядов регистра соединены с соответствующими установочными входами двоичного счетчика, счетный вход которого связан с входной шиной устройства, а выход последнего разряда - с входом установки в единичное состояние триггера знака. Инверсный выход триггера подсоединен к одному из входов первой схемы «И, а прямой выход - к одному из входов второй схемы «И, другой вход которой подключен к выходу переноса соответствующего нижней границе допуска разряда двоичного счетчика, а выход - к входу установки в единичное состояние триггера памяти. Прямой выход триггера памяти связан с одним из входов третьей схемы «И, инверсный - с одним из входов четвертой схемы «И, другой вход которой соединен с прямым выходом триггера знака, а другие входы первой и третьей схемы «И и третий вход четвертой схемы «И - с шиной управления, которая через схему задержки подключена к входам установки в нулевое состояние триггера памяти, триггера знака и регистра. В известное устройство В1 едена н иятая схема «И.

Известные устройства допускового контроля не позволяют анализировать аномальные выбросы оцениваемого параметра, которые необходимы для устройств контроля и диагностики неисправностей.

Цель изобретения - расширение класса решаемых задач.

Для этого в устройство для сравнения двоичных чисел введен дешифратор сбоев, состоящий из двух схем «И, схемы «ИЛИ и двух триггеров, входы установки в нулевое состояние которых связаны с выходом схемы задержки, вход установки в единичное состояние первого триггера - с выходом первого разряда двоичного счетчика, а вход установки в единичное состояние второго триггера - с выходом первой схемы «И дешифратора сбоев, один из входов которой соединен с прямым выходом триггера знака, а другой - с выходом переноса соответствующего верхней границе допуска разряда двоичного счетчика. Прямой выход второго триггера подключен к одному из входов схемы «ИЛИ, другой вход которой связан с выходом второй схемы «И

дешифратора сбоев, входы второй схемы «И - к и 1версным выходам первого триггера и триггера зиака соответственно, а выход схемы «ИЛИ - к одному из входов пятой схелпя «И, другой вход которой соединен с

шиной управления.

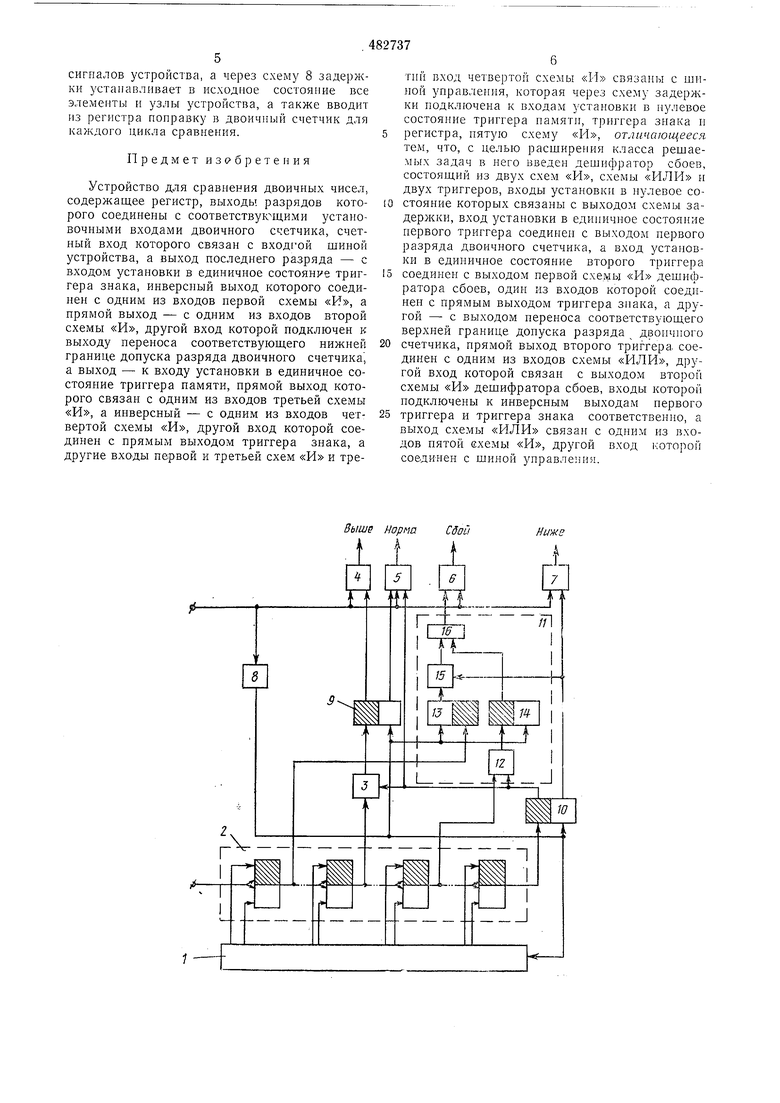

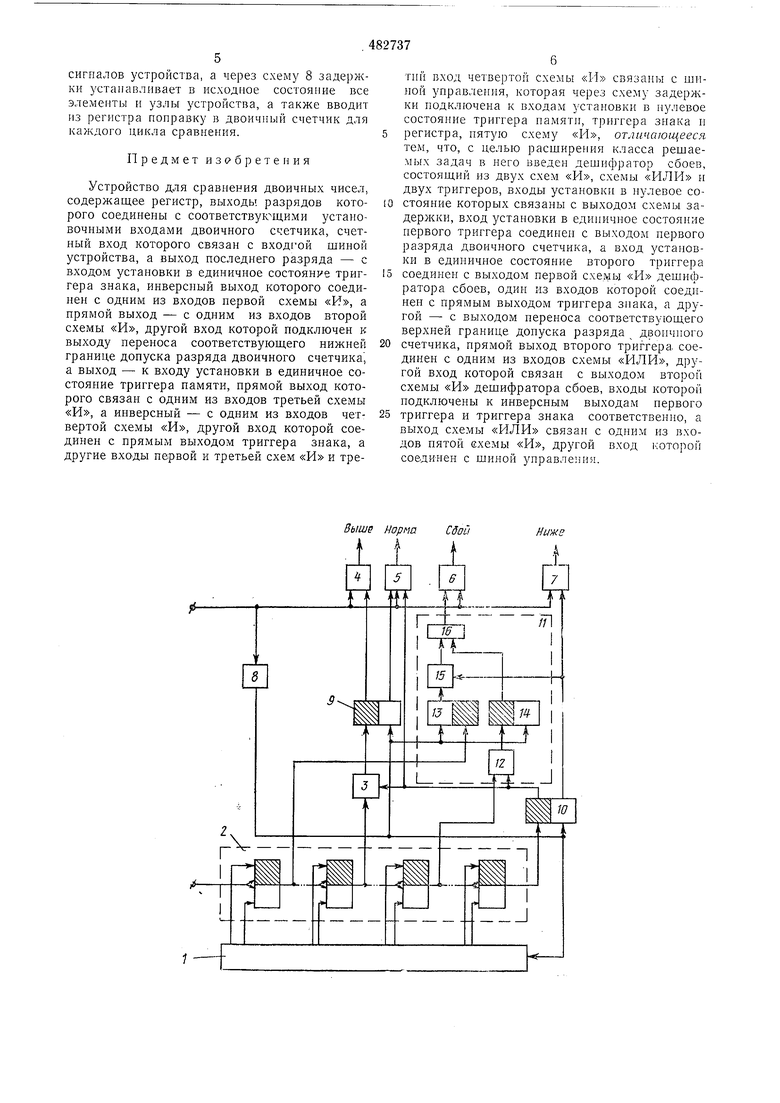

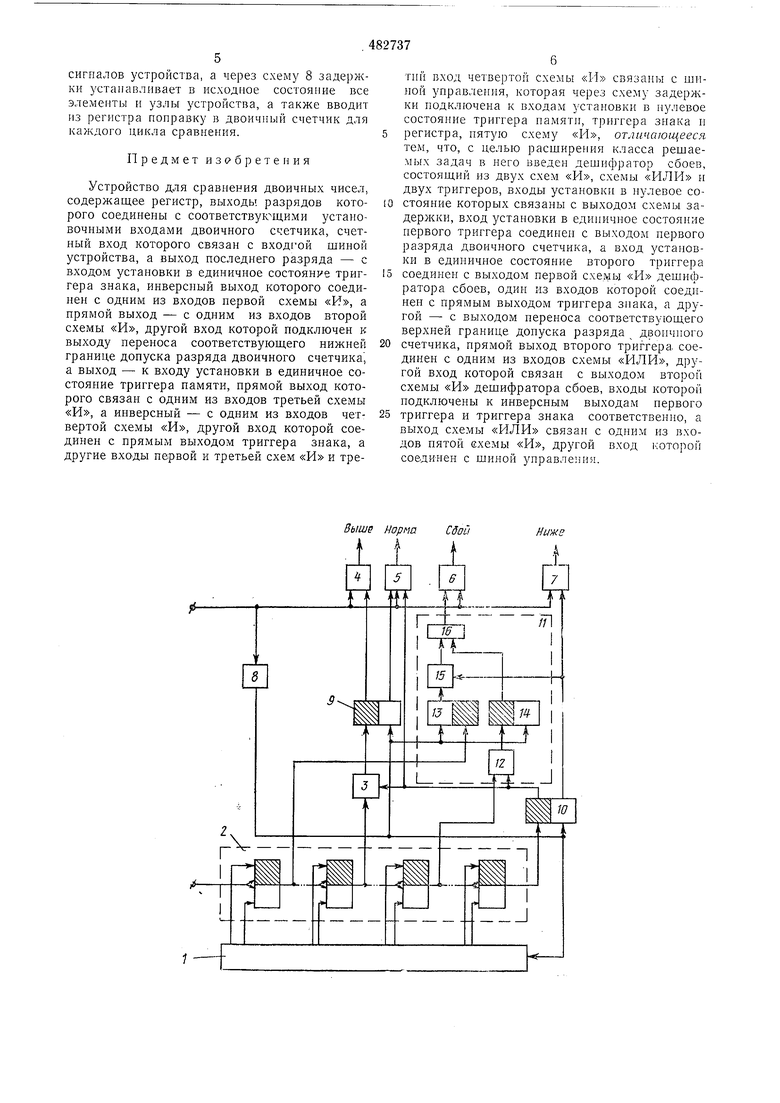

Блок-схема устройства представлена на чертеже.

Устройство содержит регистр I, двоичный счетчик 2, схемы «И 3-7, схему 8 задержки, триггер 9 памяти, триггер 10 знака, дешифратор 11 сбоев, включающий в себя логическую схему «И 12, триггеры 13, 14, схему «И 15, схему «ИЛИ 16.

До начала измерений в регистр 1 вводится поправка, соответствующая нижней границе изменения измеряемой величины, т. е. равная разности между эталонным значением этой величины (N эг ) и допустимым отклонением {±A )

На счетный вход двоичного счетчика 2 поступает число-импульсный код (Л/„зм ), соответствующий измеряемой величине. Так как поправка введена в двоичный счетчик в обратном коде, происходит ее вычитание из после чего проводится анализ состояний соответствующих разрядов двоичного счетчика. Значение допустимого отклонения (±А 2 ) определяется выходом t-ro разряда счетчика.

По окончании последовательности импульсей двоичном счетчике формируется -КОД разности между эталонным (заданным) значением Nsr . и Л/изм Если .последовательность импульсов , поступившая на двоичный счетчик, меньще нижней границы поля допуска, то сквозной перенос в двоичном счетчике не формируется, триггер 10 знака остается в исходном нулевом состоянии и опрос схемы «И 7 управляющим импульсом подает сигнал «Ниже. Сигнал «Сбой формируется, если пет переноса с первого разряда двоичного счетчика, при этом триггеры 13 и 10 остаются В исходном состоящий и схема «И

15выдает сигнал, который через схему «ИЛИ

16открывает вентиль для прохождения управляющего импульса на выход «Сбой.

Когда Л|,зм находится в поле допуска, появляется сквозпой перенос, который устанавливает триггер 10 знака в единичное состояние, при этом триггер 9 памяти остается в исходном нулевом положении, так как схема «И 3 открывается после обнуления двоичного счетчика 2 сквозным переносом, а перенос с j-ro разряда после этого не формируется. Схема «И 5 выдает сигнал «Норма за счет совпадения единичного и нулевого выхода триггеров 10 и 9 соответственно.

Если N нам превышает поле допуска, с выхода f-ro разряда возникает перенос, который устанавливает триггер памяти в единичное состояние, и схема «И 4 подает сигнал «Выше. При дальнейшем увеличении Л,зм появляется перенос с /-го разряда двоичпого счетчика, что фиксируется триггером 14, который устанавливается в единичное состояние через схему «И 12, выход единицы триггера 14 через схему «ИЛИ 16 выдает разрещение на формирование сигнала «Сбой схемой «И 6.

Таким образом, фиксируются все входные ситуации, возникающие при сравнении двух двоичных чисел.

При значениях 4 ( -Д) после окончания цикла сравнения триггер знака остается в нулевом (исходном) состоянии, выдавая с помощью логической схемы «И 7 в момент прохождения управляющего импульса выходной сигнал «Ниже нормы.

При значениях Л„з,„( +Д) после окончания цикла сравнения триггер знака переходит в единичное состояние, закрывая схему «И 7 и открывая по одному из входов схему «И 3. Импульс переноса с i-ro разряда, соответствующий превышению верхнего допз ска, через схему «И 3 устанавливает триггер памяти в единичное состояние, фиксируя с

помощью схемы «И 4 в момент опроса выходной сигнал «Выше нормы.

При значениях () Л,з„ (Ngr + A) по окончании цикла сравнения триггер знака также занимает единичное состояние, запрещая формирование сигнала «Ниже нормы и открывая по одному из входов схемы «И 3, 5, но очередного переноса с г-го разряда двоичного счетчика после переключения триггера знака уже не возникает, так как по условию

Л,з„(Л,,+A).

Таким образом, триггер памяти остается в исходном (нулевом) состоянии, а на выходе логической схемы «И 5 в момент опроса появляется выходной сигнал «Норма.

Аналогичным образом, анализируя состояние любых других разрядов двоичного счетчика (1р ,..., ip . . ., /р. . ., rtp) можно вести оценку любых отклонений параметра Л/„зм В частности, с помощью дешифратора сбоев

по состоянию первого и /-го разрядов счетчика проводится анализ анамальных выбросов (сбоев).

При значениях ( +А) формируется перенос с одного из старших разрядов

(ip ) счетчика разности, который через открытую ранее схему «И 12 устанавливает триггер 14 в единичное состояние. В свою очередь выход триггера 14 выдает разрешение через схему «ИЛИ 16 на схему «И 6, через

которую в момент прохождения управляющего импульса формируется сигнал «Сбой. Наличие при этом сигпала «Выше нормы позволяет однозначно характеризовать отказ (например, N „зы поступает в виде ненрерывной

последовательности).

При вырол денном (вплоть до одного импульса) значении входной импульсной последовательности Л „зм (Л/эт-А) триггер 10 знака и триггер 13 остаются в исходном (пулевом) состоянии и открывают схему «И 15, выходной сигнал которой через схему «ИЛИ 16 и схему «И 6 подается на выход устройства в виде сигнала «Сбой.

Наличие при этом сигнала «Ниже нормы

позволяет сделать вывод о частичном или полном пропадании импульсов измеряемой последовательности.

Синхронизирующий работу всего устройства управляющий импульс опрашивает одновременно схемы «И формирования выходных

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел с допусками | 1980 |

|

SU968805A1 |

| Устройство для сравнения чисел с допуском | 1985 |

|

SU1251067A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Вычислительное устройство | 1983 |

|

SU1167605A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для магнитной записи сигналов времени | 1985 |

|

SU1277182A1 |

Авторы

Даты

1975-08-30—Публикация

1973-04-06—Подача