126U974 синхронных и асинхронных схем на ре- локализацией места неисправности и

альной тактовой частоте в диалоговом режиме работы с оператором с точной

идентификацией ее типа. 8 з.п. ф-л О ил.

i Изобретение относится к контроль- :но-измерительной технике и может быть использовано для контроля элек- трических параметров и диагностики i неисправностей цифровых. узлов.

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения контроля и диагностики цифровых узлов на реальной тактовой частоте в реальном масштабе времени и проведения двук- порогового контроля уровней на любом из выводов контролируемого цифрового узла.

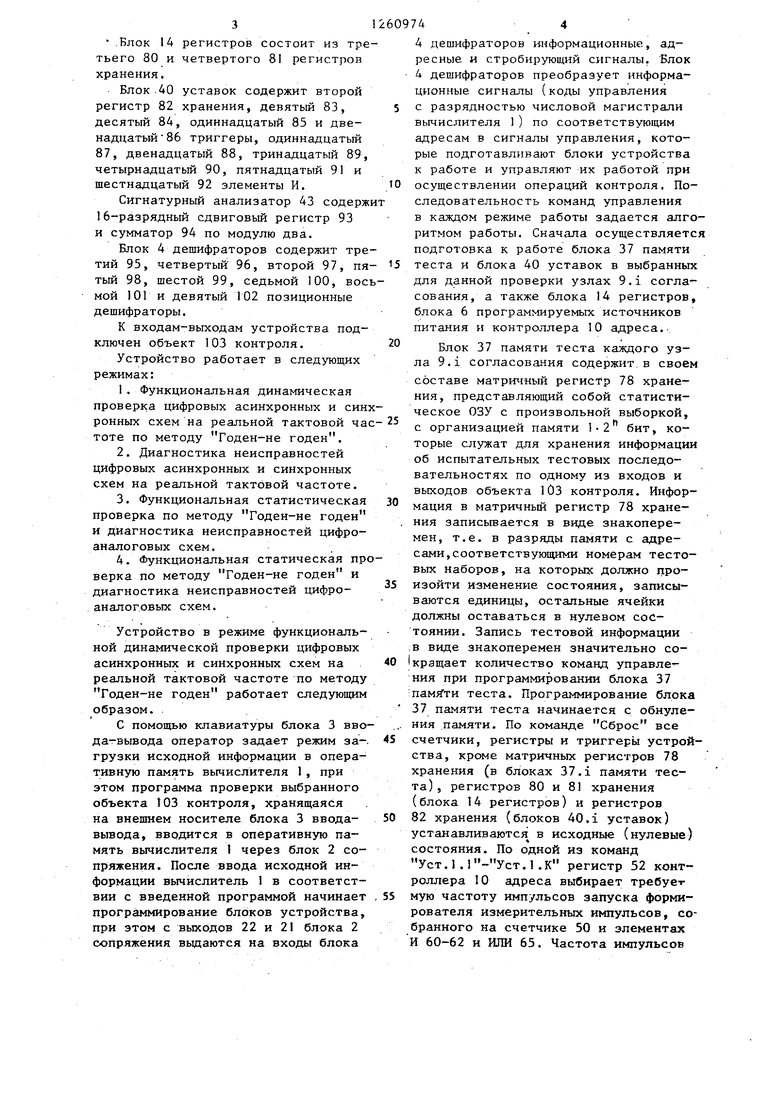

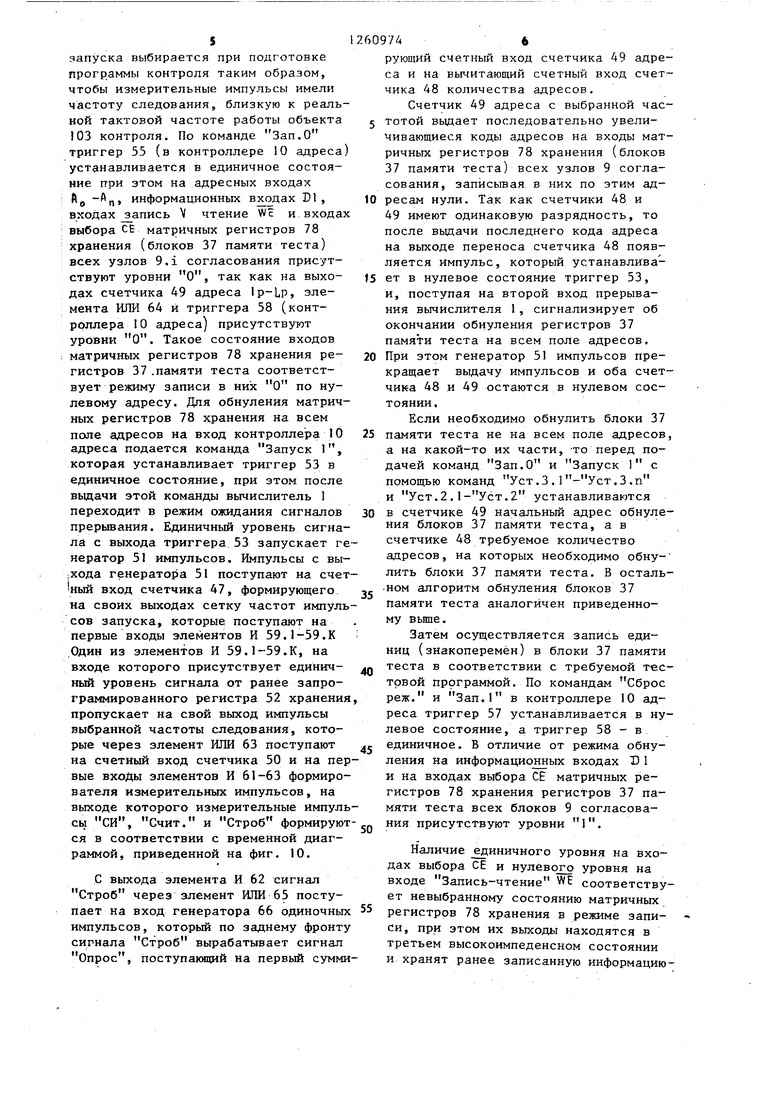

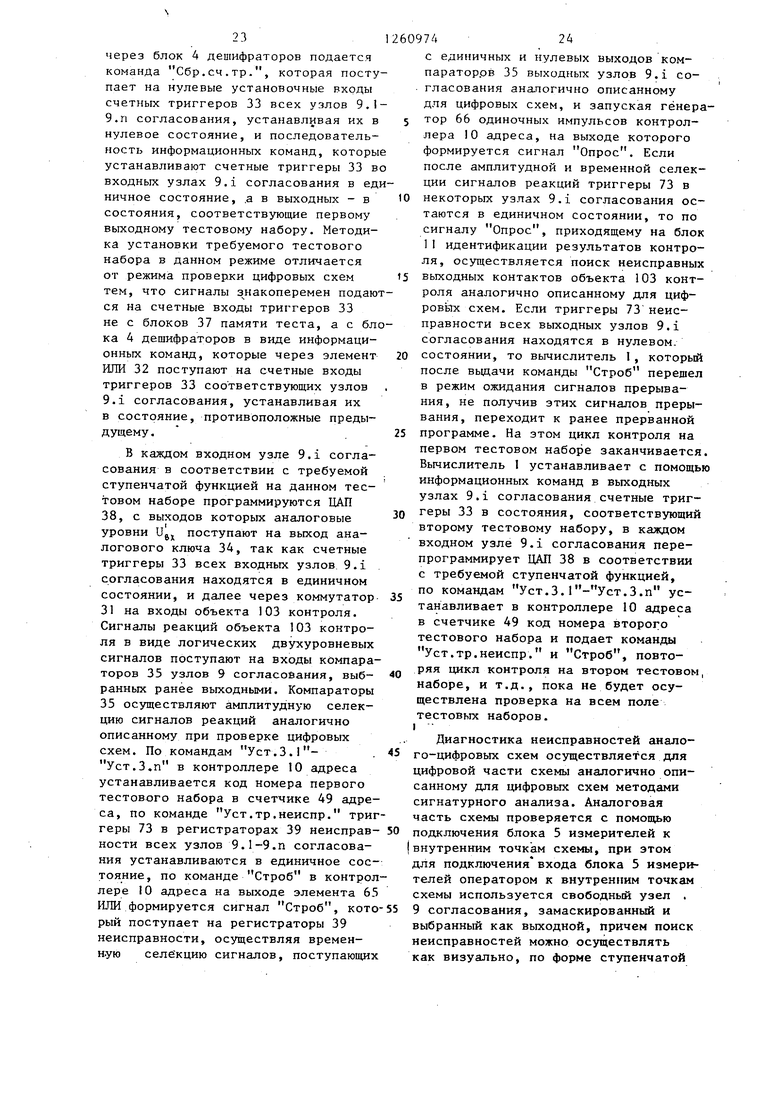

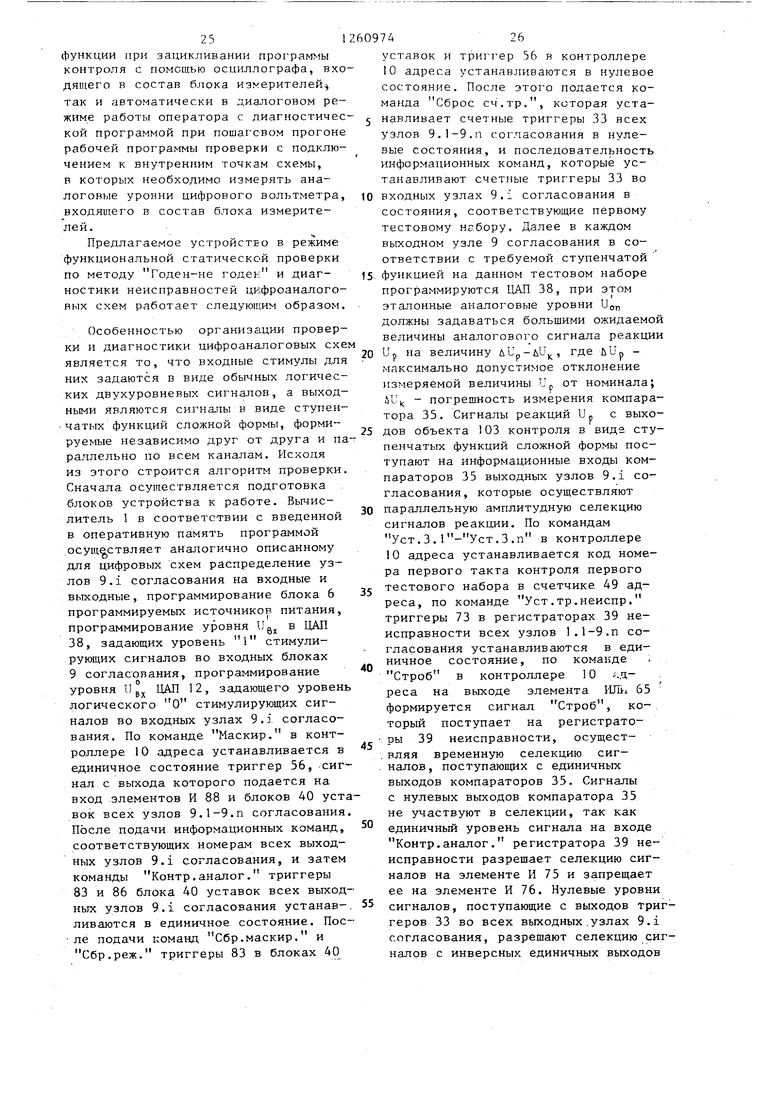

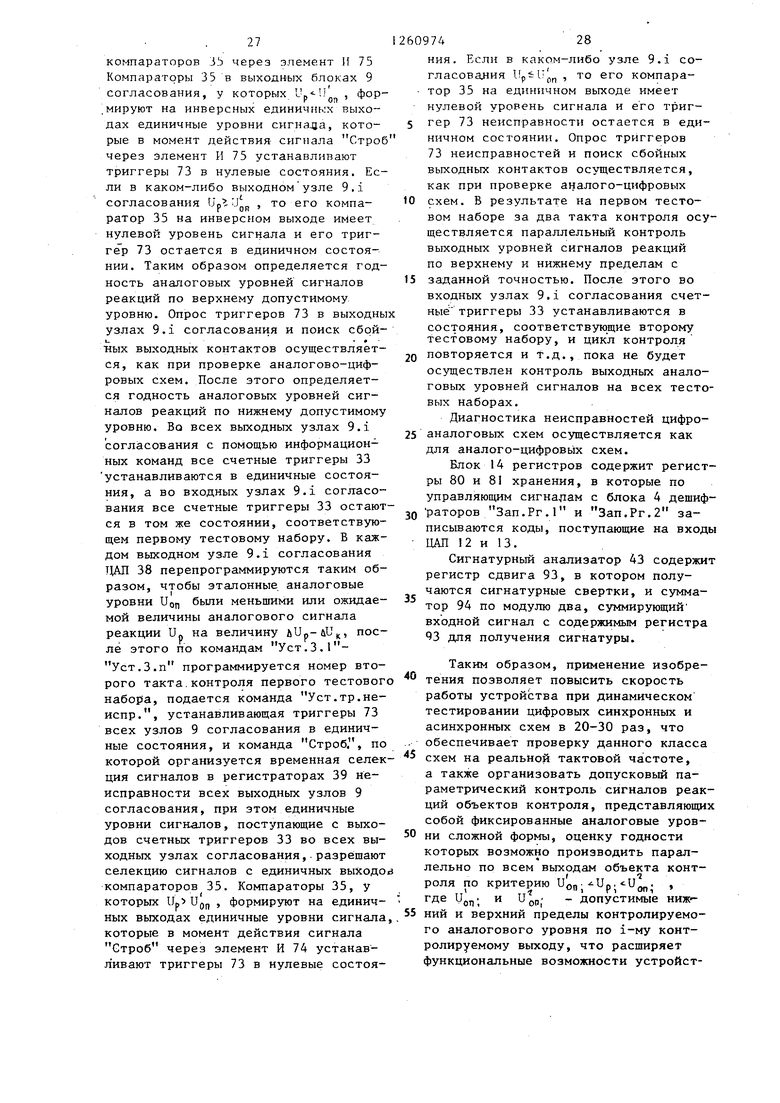

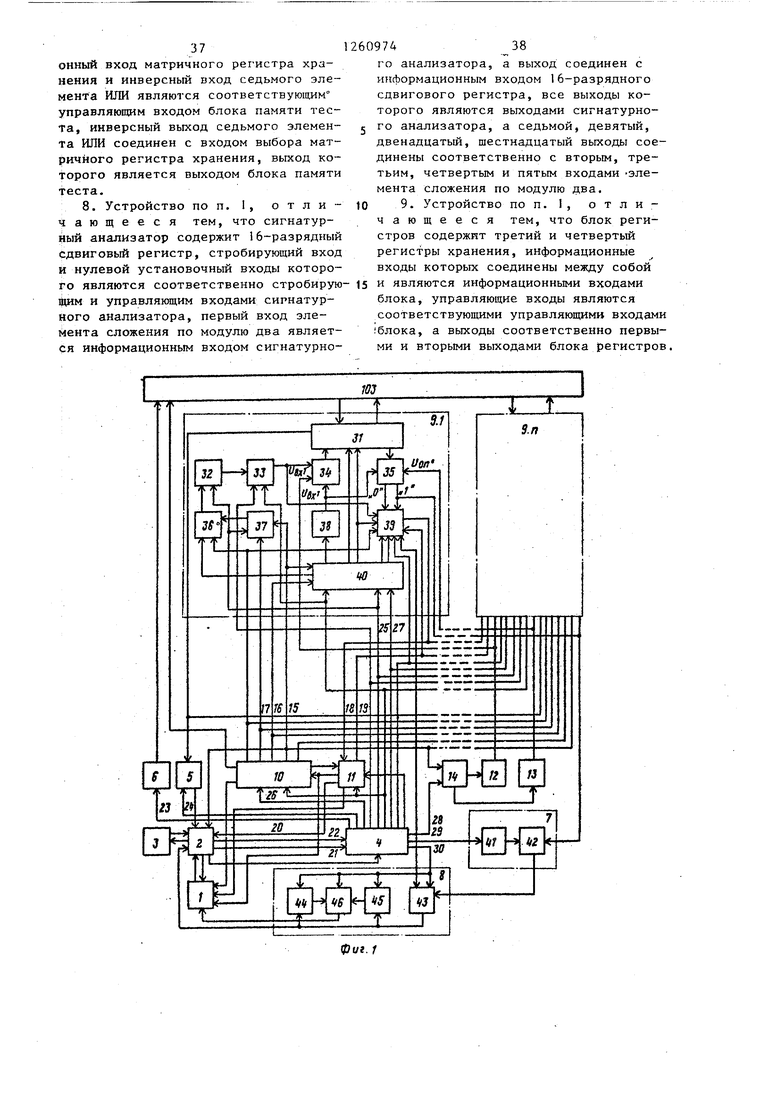

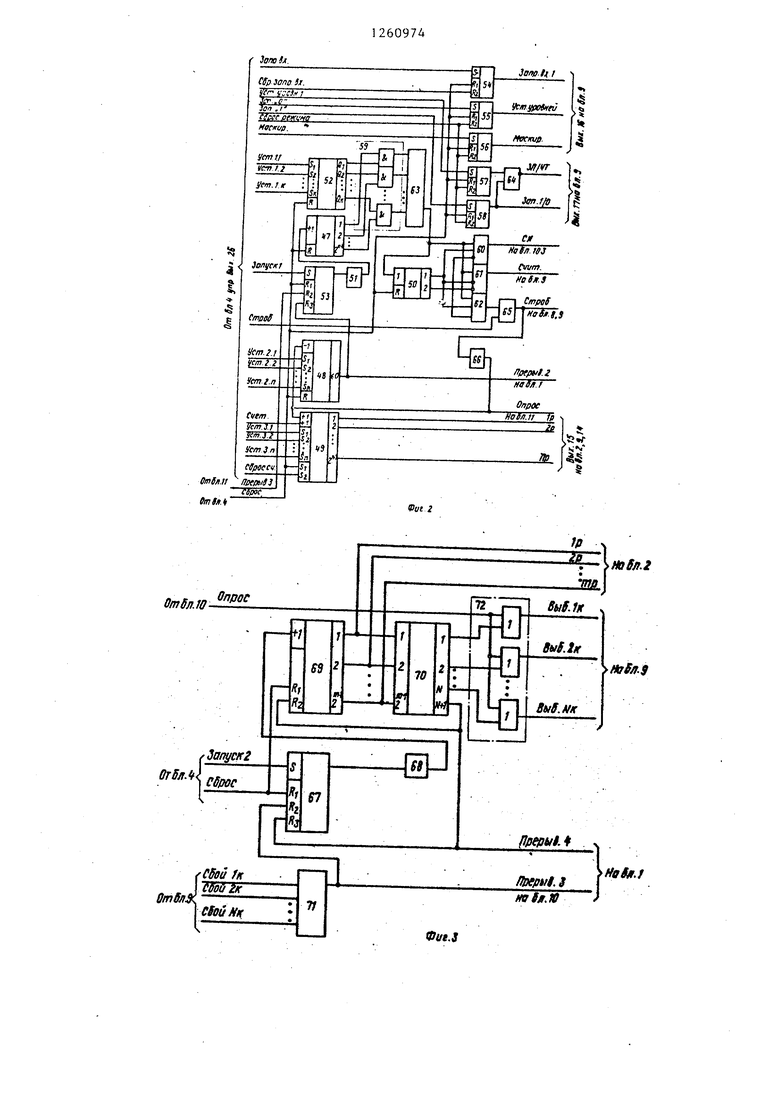

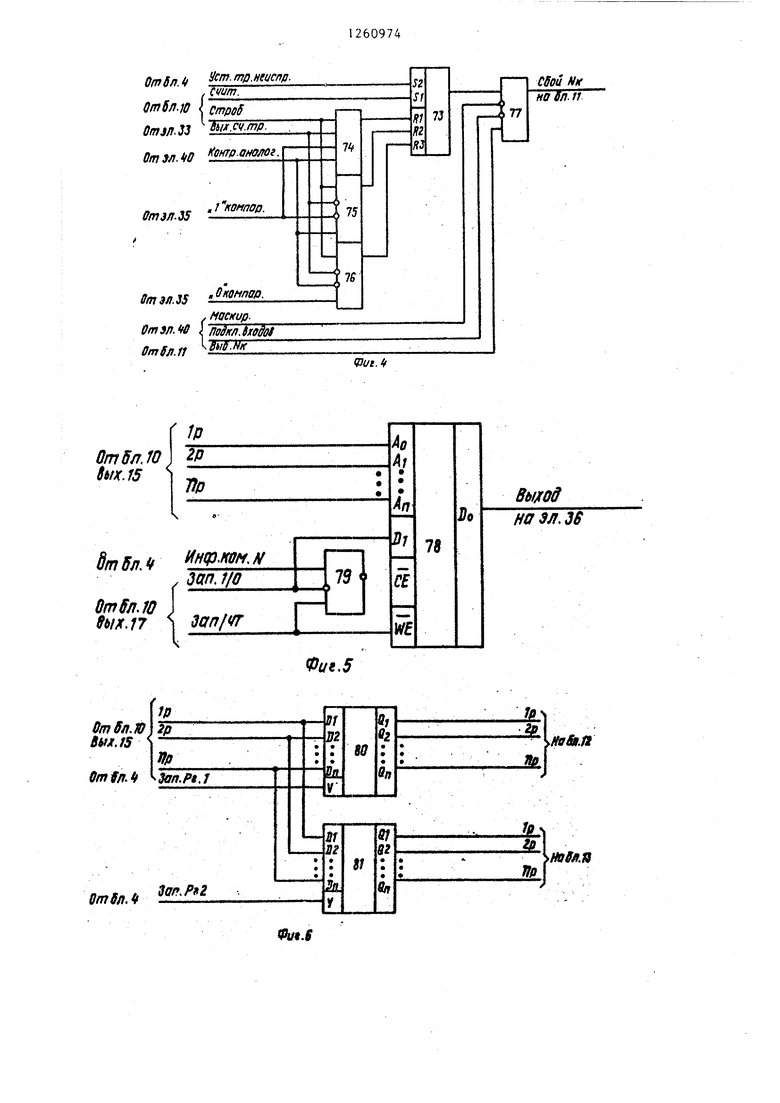

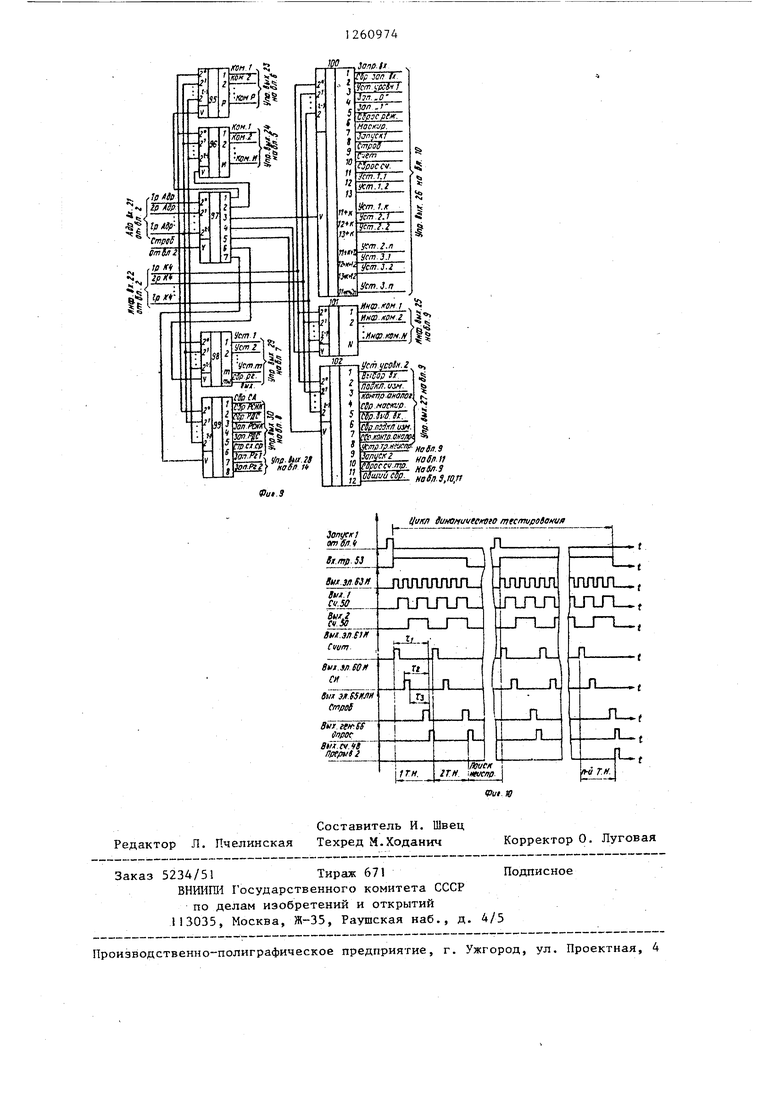

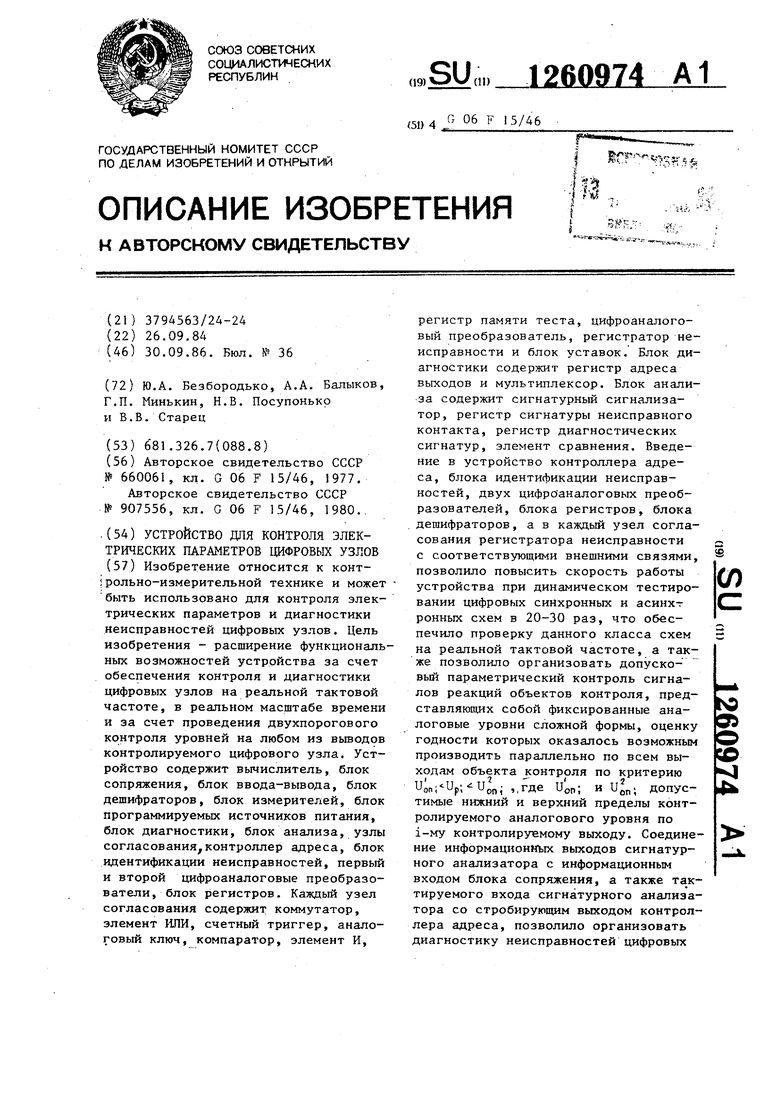

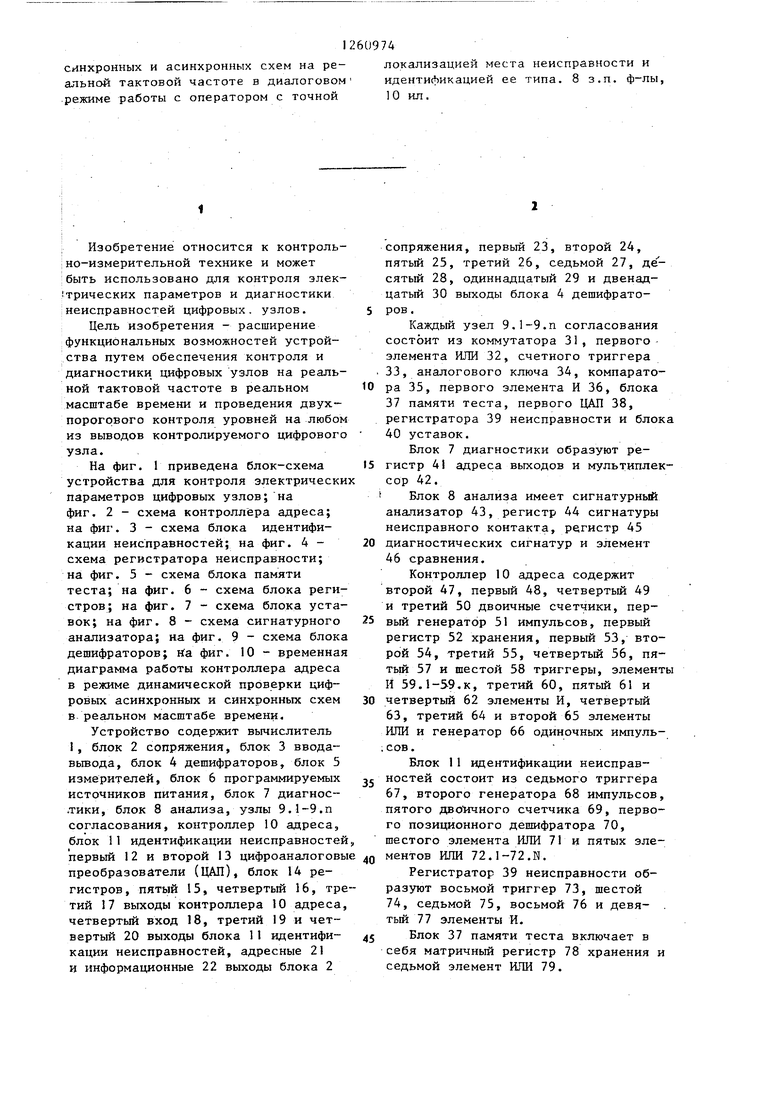

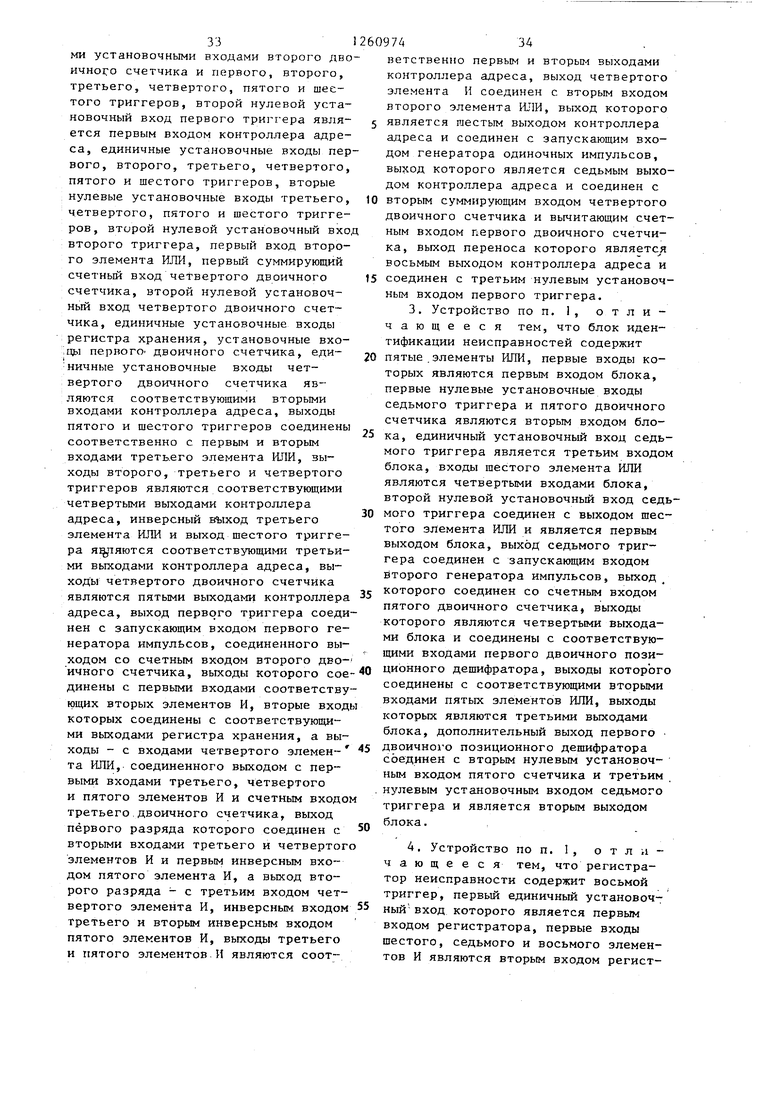

На фиг. 1 приведена блок-схема устройства для контроля электрически параметров цифровых узлов; на фиг. 2 - схема контроллера адреса; на фиг. 3 - схема блока идентификации неисправностей; на фиг. 4 - схема регистратора неисправности; на фиг. 5 - схема блока памяти теста; на фиг. 6 - схема блока регистров; на фиг. 7 - схема блока уставок; на фиг. 8 - схема сигнатурного анализатора; на фиг. 9 - схема блока дешифраторов; Ка фиг. 10 - временная диаграмма работы контроллера адреса в режиме динамической проверки цифровых асинхронных и синхронных схем в реальном масштабе времени.

Устройство содержит вычислитель I, блок 2 сопряжения, блок 3 ввода- вьгеода, блок 4 дешифраторов, блок 5 измерителей, блок 6 программируемых источников питания, блок 7 диагнос- .тики, блок 8 анализа, узлы 9.1-9.П согласования, контроллер 10 адреса, блок 11 идентификации неисправностей первый 12 и второй 13 цифроаналоговы преобразователи (ЦАП), блок 14 регистров, пятый 15, четвертый 16, третий 17 выходы контроллера 10 адреса, четвертый вход 18, третий 19 и четвертый 20 выходы блока 11 идентификации неисправностей, адресные 21 и информационные 22 выходы блока 2

4 локализацией места неисправности и

идентификацией ее типа. 8 з.п. ф-лы, О ил.

сопряжения, первый 23, второй 24, пятый 25, третий 26, седьмой 27, де - сятый 28, одиннадцатый 29 и двенадцатый 30 выходы блока 4 дешифрато- ров.

Каждый узел 9.1-9.П согласования состоит из коммутатора 31, первого элемента ИЛИ 32, счетного триггера 33, аналогового ключа 34, компаратора 35, первого элемента И 36, блока 37 памяти теста, первого ЦАП 38, регистратора 39 неисправности и блока 40 уставок.

Блок 7 диагностики образуют регистр 41 адреса выходов и мультиплексор 42.

Блок 8 анализа имеет сигнатурный анализатор 43, регистр 44 сигнатуры неисправного контакта, регистр 45

диагностических сигнатур и элемент 46 сравнения.

Контроллер 10 адреса содержит второй 47, первый 48, четвертый 49 и третий 50 двоичные счетчики, первый генератор 51 импульсов, первый регистр 52 хранения, первый 53, второй 54, третий 55, четвертый 56, пятый 57 и шестой 58 триггеры, элементы И 59.1-59.к, третий 60, пятый 61 и

четвертый 62 элементы И, четвертый 63, третий 64 и второй 65 элементы ИЛИ и генератор 66 одиночных импуль- сов.

Блок 11 идентификации неисправностей состоит из седьмого триггера 67, второго генератора 68 импульсов, пятого дво ичного счетчика 69, первого позиционного дешифратора 70, шестого элемента ШШ 71 и пятых элементов ИЛИ 72.I-72.N.

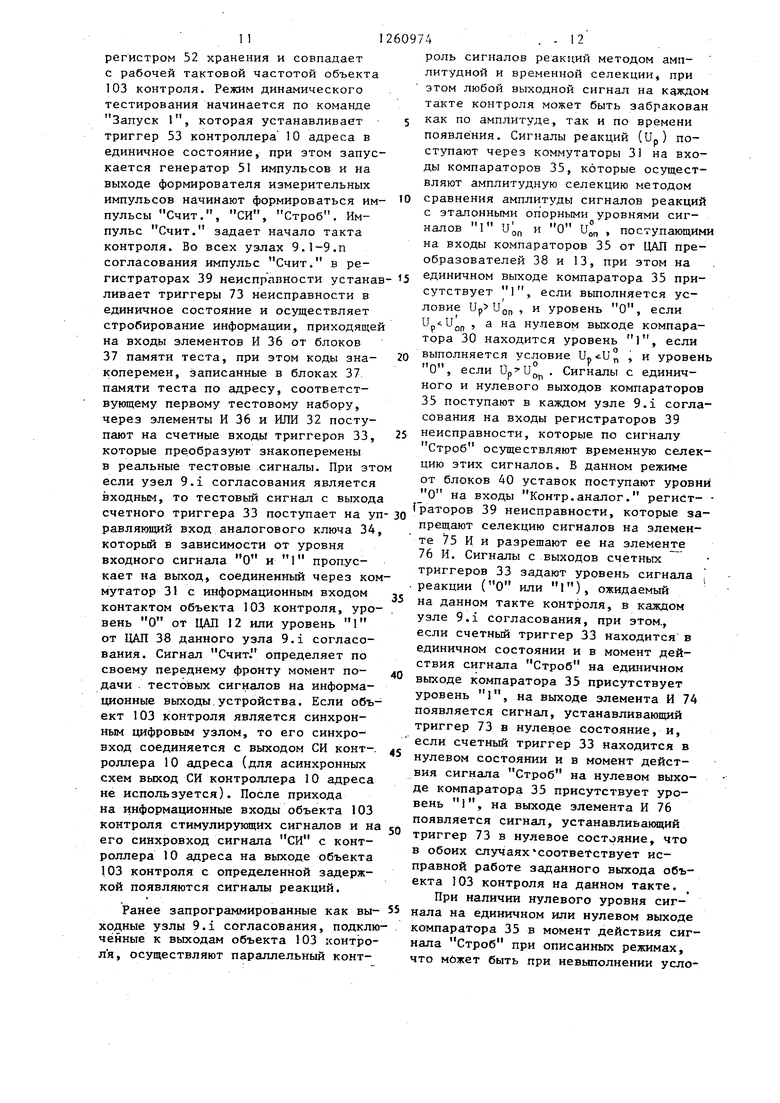

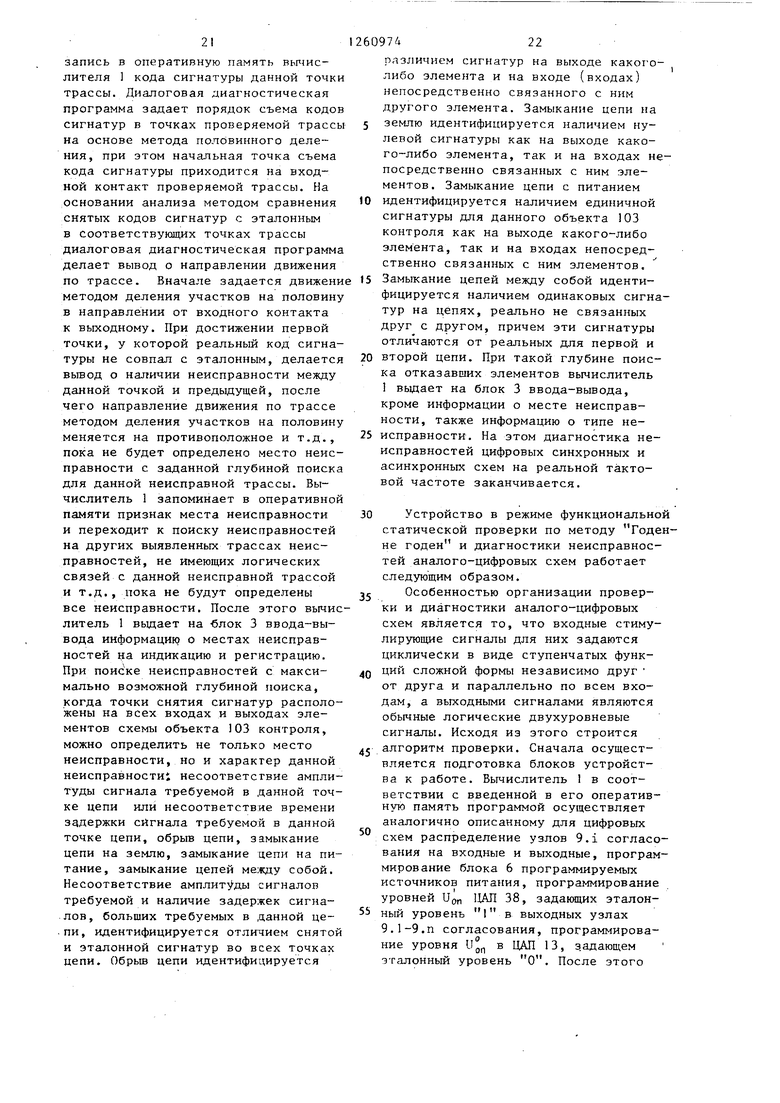

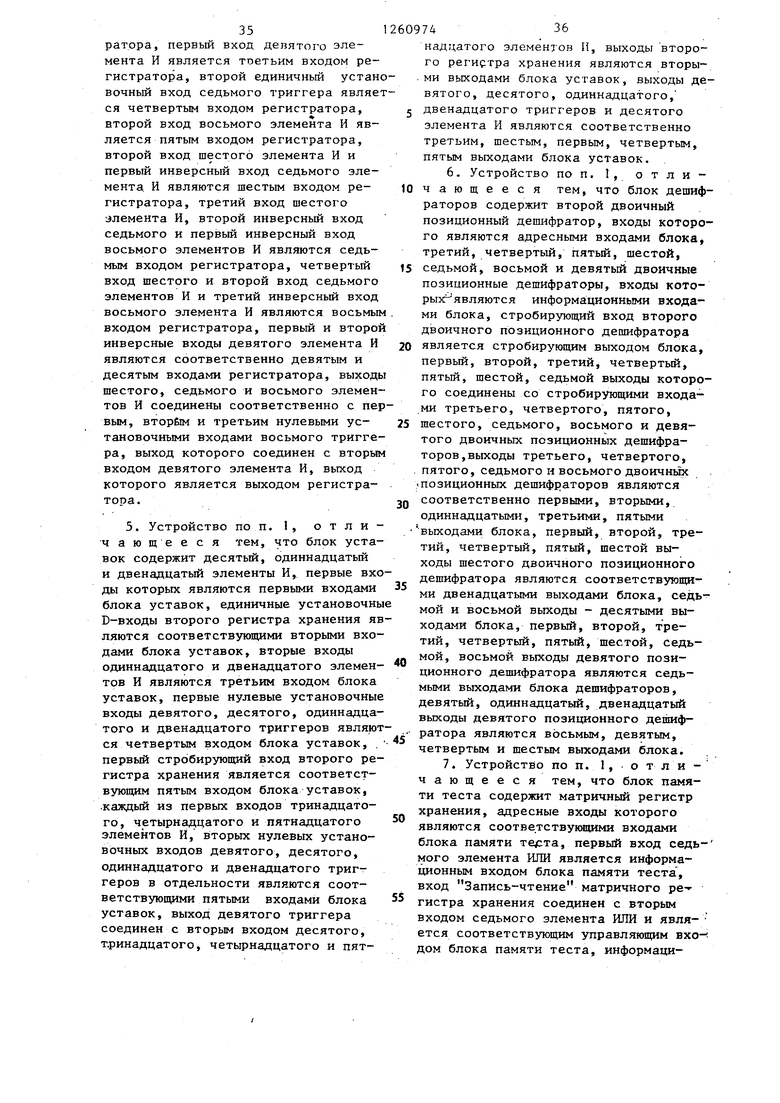

Регистратор 39 неисправности образуют восьмой триггер 73, шестой 74, седьмой 75, восьмой 76 и девя- . тый 77 элементы И.

Блок 37 памяти теста включает в себя матричный регистр 78 хранения и седьмой элемент ИЛИ 79.

.Блок 14 тьего 80 и хранения.

Блок. 40 регистр 82

регистров состоит из тре- четвертого 81 регистров

уставок содержит второй хранения, девятый 83, десятый 84, одиннадцатый 85 и двенадцатый 86 триггеры, одиннадцатый 87, двенадцатый 88, тринадцатый 89, четырнадцатый 90, пятнадцатый 91 и шестнадцатый 92 элементы И.

Сигнатурный анализатор 43 содержи 16-разрядный сдвиговый регистр 93 и сумматор 94 по модулю два.

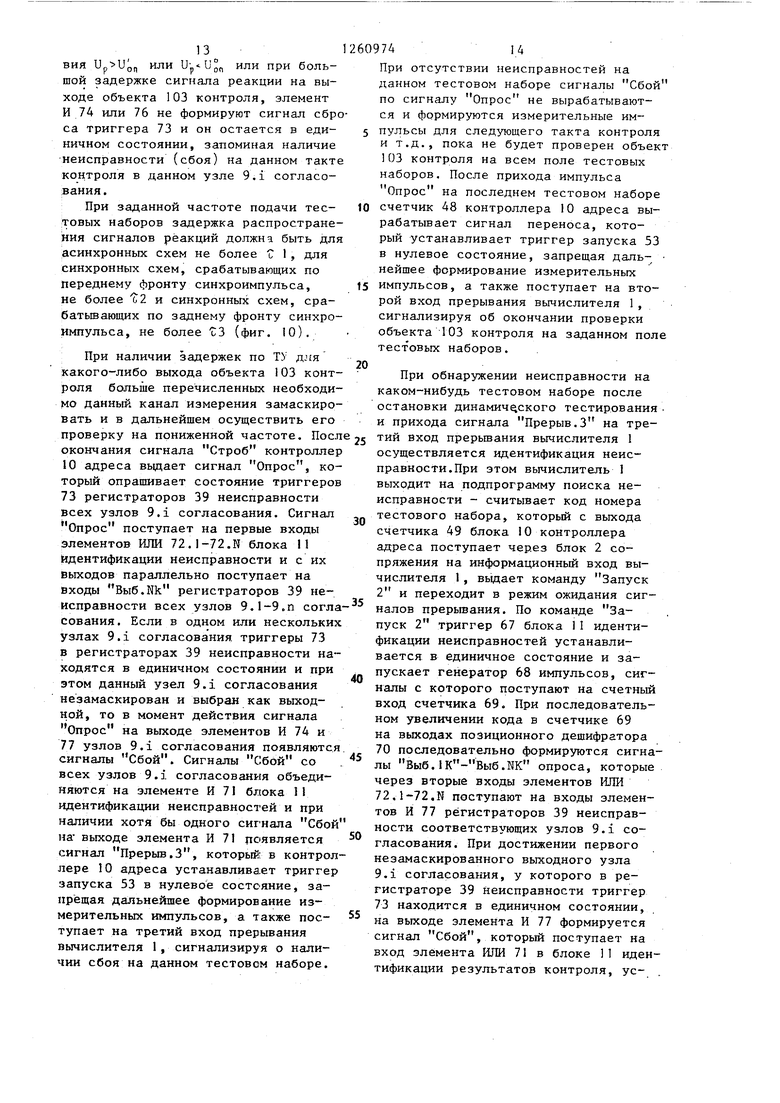

Блок 4 дешифраторов содержит третий 95, четвертый 96, второй 97, пя- тый 98, шестой 99, седьмой 100, восьмой 101 и девятый 102 позиционные дешифраторы.

К входам-выходам устройства подключен объект 103 контроля.

Устройство работает в следующих режимах:

1.Функциональная динамическая проверка Цифровых асинхронных и синхронных схем на реальной тактовой час тоте по методу Годен-не годен.

2.Диагностика неисправностей цифровых асинхронных и синхронных схем на реальной тактовой частоте.

3.Функциональная статистическая проверка по методу Годен-не годен и диагностика неисправностей цифро- аналоговых схем.

4.Функциональная статическая проверка по методу Годен-не годен и диагностика неисправностей цифро- аналоговых схем.

Устройство в режиме функциональной динамической проверки цифровых асинхронных и синхронных схем на реальной тактовой частоте по методу Годен-не годен работает следующим образом. .

С помощью клавиатуры блока 3 ввода-вывода оператор задает режим загрузки исходной информации в оперативную память вычислителя 1, при этом программа проверки выбранного объекта 03 контроля, хранящаяся на внешнем носителе блока 3 ввода- вывода, вводится в оперативную память вычислителя 1 через блок 2 сопряжения. После ввода исходной информации вычислитель 1 в соответствии с введенной программой начинает программирование блоков устройства, при этом с выходов 22 и 21 блока 2 сопряжения вьщаются на входы блока

10

т

5 20

25

2609744

4 дешифраторов информационные, адресные и стробирующий сигналы. Блок 4 дешифраторов преобразует информационные сигналы (коды управления с разрядностью числовой магистрали вычислителя I) по соответствующим адресам в сигналы управления, которые подготавливают блоки устройства к работе и управляют их работой при осуществлении операций контроля. Последовательность команд управления в каждом режиме работы задается алгоритмом работы. Сначала осуществляется подготовка к работе блока 37 памяти теста и блока 40 уставок в выбранных для данной проверки узлах 9.1 согласования, а также блока 14 регистров, блока 6 программируемых источников питания и контроллера 10 адреса..

Блок 37 памяти теста каждого узла 9.1 согласования содержит в своем составе матричный регистр 78 хранения, представляющий собой статистическое ОЗУ с произвольной выборкой,

п

30

35

40 I

45

50

55

с организацией памяти Ь2 бит, которые служат для хранения информации об испытательных тестовых последовательностях по одному из входов и выходов объекта 103 контроля. Информация в матричный регистр 78 хранения записывается в виде знакопере- мен, т.е. в разряды памяти с адресами, соответствующими номерам тестовых наборов, на которых должно произойти изменение состояния, записываются единицы, остальные ячейки должны оставаться в нулевом состоянии. Запись тестовой информации ;в виде знакоперемен значительно сокращает количество команд управле ния при программировании блока 37 памй ти теста. Программирование блока 37 памяти теста начинается с обнуления памяти. По команде Сброс все счетчики, регистры и триггеры устройства, кроме матричных регистров 78 хранения (в блоках 37.i памяти теста) , регистров 80 и 81 хранения (блока 14 регистров) и регистров 82 хранения (блоков 40.i уставок) устанавливаются в исходные (нулевые) состояния. По одной из команд Уст.1..1.К регистр 52 контроллера 10 адреса выбирает трабуе-г мую частоту импульсов запуска формирователя измерительных импульсов, собранного на счетчике 50 и элементах И 60-62 и ИЛИ 65. Частота импульсов

запуска выбирается при подготовке программы контроля таким образом, чтобы измерительные импульсы имели частоту следования 5 близкую к реальной тактовой частоте работы объекта 103 контроля. По команде Зап.О триггер 55 (в контроллере 0 адреса) устанавливается в единичное состояние при этом на адресных входах Ид -А„, информациоиньк входах D1,

входах з апись V чтение WE и входах выбора СЕ матричных регистров 78 хранения (блоков 37 памяти теста) всех узлов 9.1 согласования присутствуют уровни О, так как на выходах счетчика 49 адреса 1р-1р, элемента ИЛИ 64 и триггера 58 (контроллера 1 О адреса) присутствуют уровни О. Такое состояние входов матричных регистров 78 хранения регистров 37 .памяти теста соответствует режиму записи в них О по нулевому адресу. Для обнуления матричных регистров 78 хранения на всем поле адресов на вход контроллера 10 адреса подается команда Запуск 1, которая устанавливает триггер 53 в единичное состояние, при этом после вьодачи этой команды вычислитель 1 переходит в режим ожидания сигналов прерывания. Единичный уровень сигнала с выхода триггера 53 запускает генератор 51 импульсов. Импульсы с вы- ;Хода генератора 51 поступают на счет ный вход счетчика 47, формирующего на своих выходах сетку частот импульсов запуска, которые поступают на первые входы элементов И 59.1-59.К Один из элементов И 59.1-59.К, на входе которого присутствует единич- ный уровень сигнала от ранее запрограммированного регистра 52 хранения пропускает на свой выход импульсы выбранной частоты следования, которые через элемент ИЛИ 63 поступают на счетный вход счетчика 50 и на первые входы элементов И 61-63 формирователя измерительных импульсов, На выходе которого измерительные импульсы СИ, Счит. и Строб формируют ся в соответствии с временной диаграммой, приведенной на фиг. 10.

С выхода элемента И 62 сигнал Строб через элемент ИЛИ 65 поступает на вход генератора 66 одиночных импульсов, который по заднему фронту сигнала Строб вырабатывает сигнал Опрос, поступающий на первый сумми20

25

30

35 jg

2609746

рующий счетный вход счетчика 49 адреса и на вычитающий счетный вход счетчика 48 количества адресов.

Счетчик 49 адреса с выбранной час- 5 тотой выдает последовательно увеличивающиеся коды адресов на входы матричных регистров 78 хранения (блоков 37 памяти теста) всех узлов 9 согласования, запйсьшая в них по этим ад10 ресам нули. Так как счетчики 48 и 49 имеют одинаковую разрядность, то после вьщачи последнего кода адреса на выходе переноса счетчика 48 появляется импульс, который устанавлйва15 ет в нулевое состояние триггер 53, и, поступая на второй вход прерывания вычислителя 1, сигнализирует об окончании обнуления регистров 37 памяти теста на всем поле адресов. При этом генератор 51 импульсов прекращает выдачу импульсов и оба счетчика 48 и 49 остаются в нулевом состоянии.

Если необходимо обнулить блоки 37 памяти теста не на всем поле адресов, а на какой-то их части, То перед подачей команд Зап.О и Запуск 1 с помощью команд Уст.З..3.п и Уст.2..2 устанавливаются

в счетчике 49 начальный адрес обнуления блоков 37 памяти теста, а в

счетчике 48 требуемое количество адресов, на которых необходимо обну- лить блоки 37 памяти теста. В остальном алгоритм обнуления блоков 37 памяти теста аналогичен приведенному вьппе.

Затем осуществляется запись единиц (знакоперемён) в блоки 37 памяти теста в соответствии с требуемой тестовой программой. По командам Сброс реж. и Зап. Г в контроллере 10 адреса триггер 57 устанавливается в нулевое состояние, а триггер 58 - в единичное. В отличие от режима обнуления на информацио2гаых входах D 1 и на входах выбора СЕ матричных регистров 78 хранения регистров 37 памяти теста всех блоков 9 согласования присутствуют уровни 1.

Наличие циничного уровня на входах выбора СЕ и нyлeвoJ уровня на входе Запись-чтение VVH соответствует невыбранному состоянию матричных регистров 78 хранения в режиме записи, при этом их выходы находятся в третьем высокоимпеденсном состоянии и хранят ранее записанную информацию7

Ъ данном случае нули по всем адресам После этого в контроллере 10 адреса по командам , Уст.3. Г -Уст.З.п прог раммируется адрес первого тестового набора требуемой тестовой последовательности и последовательно подаются

.информационные команды на те блоки 9.1 согласования, в которые на .данном тестовом наборе необходимо запи

ствляя генерирование стимулирующих сигналов, и выходным, осуществляя контроль сигналов реакций, а блок 5 измерителей может при этом осуществлять параметрический контроль вы ходных сигналов объекта 103 контроля ЦАП 38 преобразует коды двоичных чисел, поступающих на его информационные выходы с блока 40 уставок, в ана

сать единицы (знакоперемены). Инфор- Q логовые уровни входных сигналов Г

и. вх. для аналогового ключа 34 и в

мационные команды поступают на входы элементов ИЛИ 79 в выбранных блоках 37 памяти тестей в момент их действия на входах СЕ соотв.етствующих матричных регистров 78 хранения присутствуют уровни О, а так как на информационных входах D1 всех матричных регистров 78 хранения присутаналоговые уровни эталонных опорных сигналов 1 Ugn для компараторов 35. Программирование ЦАП 38 во вход15 ных и выходных узлах 9.1 согласовани в данном режиме осуществляется один раз перед началом проверки, при этом уровень сигнала 1 может быть задан в каждом канале независимо,-что

ствует уровень

Г

в них последовательно записываются единицы по дан- 20 позволяет проверять объекты контроля, выполненные на элементах с различным типом логики. Сигналы Маскир. и Контр.аналог., поступающие с блока 40 установок на вход регистраному адресу. После окончания действия информационных команд матричные регистры 78 хранения блоков 37 памяти теста (для выбранных узлов 9.1 согласования) переходят в невыбранное25 тора 39 неисправности, маскируют выход триггера 73 и задают режим контроля реакций логических либо аналоговых сигналов. Программирование блока 40 уставок в данном режиме осу- 30

состояние и хранят ранее записанную информацию, т.е. 1. Затем осуществляется программирование блоков 37 памяти теста на следующем тестовом наборе, при этом на второй счетный вход счетчика 49 адреса подается команда Счет, устанавливая на выходе счетчика 49 адреса код адреса следующего тестового набора. Запись знакоществляется следующим образом. В исходном состоянии триггеры 83-86 блока 40 уставок находятся в нулевом состоянии, при этом все узлы 9.1-9.П согласования размаскированы перемен на данном адресе осуществля- . и выбраны как выходные, входы блока

Тается аналогично описанному вьщ1е КИМ образом программируются блоки 37 памяти теста во всех узлах 9.1 согласования на всем требуемом поле адресов (тестовых наборов).

Далее по командам от блока 4 дешифраторов программируются блоки 40 . уставок, которые определяют состояние .элементов соответствующих узлов 9.1 согласования, а именно коммутаторов 45 31,ЦАП 38 и регистраторов 39 неисправности.

В зависимости от управляющего сигнала Подкл.входов с блока 40 уста- 50 новок коммутатор 31 подключает к контакту объекта I03 контроля выход аналогового ключа 34 и сигнальный вход компаратора 35, а по сигналу Подкл.измер. к данному контакту 55 подключается вход блока 5 измерителей. Соответственно данный узел 9.1 согласования является входным, осуще5 измерителей отключены от контактов объекта 103 контроля, в регистраторе 39 неисправности установлен режим контроля реакций логических сигналов. Для выбора блоков 9.1 согласования, соединенных с входами объекта 103 контроля, в качестве входных подается с блока 4 дешифраторов команд Маскир. на контроллер 10 адреса, при этом триггер 56 устанавливается в единичное состояние и разрешает установку в единичное состояние триггеров 83 в блоках 40 уставок всех узлов 9.1-9.П согласования по информационным командам. После подачи набора требуемых команд и команды Выб.вх.Ч с блока 4 дешифраторов триггеры 84 в соответствующих блоках 40 уставок устанавливаются в единичное состояние, выбирая данные узлы 9.1 согласования как входные. Все незадействованные узлы 9 согласования выбираются как входные для того, чтобы в регистраторах 39

8

ствляя генерирование стимулирующих сигналов, и выходным, осуществляя контроль сигналов реакций, а блок 5 измерителей может при этом осуществлять параметрический контроль выходных сигналов объекта 103 контроля. ЦАП 38 преобразует коды двоичных чисел, поступающих на его информационные выходы с блока 40 уставок, в аналоговые уровни входных сигналов Г

аналоговые уровни эталонных опорных сигналов 1 Ugn для компараторов 35. Программирование ЦАП 38 во вход : ных и выходных узлах 9.1 согласования в данном режиме осуществляется один раз перед началом проверки, при этом уровень сигнала 1 может быть задан в каждом канале независимо,-что

ля, выполненные на элементах с различным типом логики. Сигналы Маскир. и Контр.аналог., поступающие с блока 40 установок на вход регистратора 39 неисправности, маскируют выход триггера 73 и задают режим контроля реакций логических либо аналоговых сигналов. Программирование блока 40 уставок в данном режиме осу-

5 измерителей отключены от контактов объекта 103 контроля, в регистраторе 39 неисправности установлен режим контроля реакций логических сигналов. Для выбора блоков 9.1 согласования, соединенных с входами объекта 103 контроля, в качестве входных подается с блока 4 дешифраторов команд Маскир. на контроллер 10 адреса, при этом триггер 56 устанавливается в единичное состояние и разрешает установку в единичное состояние триггеров 83 в блоках 40 уставок всех узлов 9.1-9.П согласования по информационным командам. После подачи набора требуемых команд и команды Выб.вх.Ч с блока 4 дешифраторов триггеры 84 в соответствующих блоках 40 уставок устанавливаются в единичное состояние, выбирая данные узлы 9.1 согласования как входные. Все незадействованные узлы 9 согласования выбираются как входные для того, чтобы в регистраторах 39

нгисправности выход триггера 73 (фиг.,4) блокировался сигналом Подкл.входов с блока АО, так как при этом запрещается выработка сигнала сбой при идентификации неисправностей. После этого подаются команда Сбр.маскир., устанавливающая триггер 83 всех блоков 40 уставок в нулевое состояние и команда Сброс реж., устанавливающая

триггер 56 контроллера 10 адреса в нулевое состояние.

Для установки заданных уровней ЦАП 38 подается команда Сбр.сч. и требуемые команды Уст.3. Уст.З.п на установочные входы счетчика 49 контроллера 10 адреса, с выхода которого требуемый код числа поступает на информационные

входы блока 40 уставок. Если необходимо задать одинаковые уровни сигналов на выходах ЦАП 38 всех узлов 9.1-9.П согласования, подается команда Уст.уровня 2, по которой заданный код записывается во все регистры 82 хранения блоков 40 уставок всех узлов 9.1-9.П согласования. Если необходимо задать разные единичные уровни в узлах 9.1 согласования, по команде Уст.уровня 1 в контроллере 10 адреса триггер 55 устанавливается в единичное состояние, разрешая запись в регистры 82 хранения требуемого кода по информационным командам. После этого поочередно задаются требуемые коды чисел в счетчике 49 аналогично описанному выше ч подаются требуемые информационные команды, при этом в регистры 82 хранения (блоков 40 уставок) соответствующих узлов 9.1 согласования поочередно записьгеаются требуемые коды чисел, определяющие заданный уровень сигнала ЦАП 38. После этого подается команда Сброс реж., устанавливающая триггер 55 контроллера 10 адреса в нуле- вое состояние. Для маскирования од,ного или нескольких каналов измерения узлов 9.1 согласования триггеры 83.блоков 40 уставок соответствующих узлов 9.1 согласования устанавливаются в единичное состояние аналогично описанному.

По командам от блока 4 дещифрато- , ров программируется блок 14 регистров, который определяет состояние первого 12 и второго 13 ЦАП, которые задают соответственно уровень входных

сигт1алов О и. для аналот овых клю„ ,,, ° чей 34 и уровень эталонных опорных

сигналов ло1 ического О IJex для компараторов 35 всех узлов 9,-9.п согласования. Программирование регистров 80 и 81 хранения блока 14 регистров осуществляется аналогично программированию регистров 82 хранения (блоков АО уставок), при этом код требуемого числа задается счетчиком 49 контроллера 10 адреса, а запись требуемого кода осуществляется в регистр 80 хранения по команде Зап. Рг.1 и в регистр 81 хранения по ко5 манде Зап.Рг.2.

По командам от блока 4 дешифраторов программируется блок 6 программируемых источников питания, на соответствующих вькодах которого, соеди0 ненных с щинами питания объекта 103 контроля, устанавливаются требуемые потенциалы питающих напряжений.

По командам от блока 4 дешифраторов программируется контроллер 10

5 адреса. Подаются команды Уст.3. Уст.З.п и Уст.2..2.п, которые устанавливают соответственно на выходе счетчика 49 адрес первого тестового набора, а в счетчике 48 0 код количества адресов (тестовых наборов), на которых осуществляется динамическая проверка объекта 103 контроля, а затем команда Сброс реж., которая устанавливает триггеры 55-58 в нулевое состояние, при этом на входах Запись-чтение WE матричных регистров 73 хранения всех блоков 37 памяти теста присутствует уровень 1, на стробирующих входах СЕ-уровень О, а на адресных входах

5

0

АО-АП

5

адрес первого тестового набора требуемой тестовой последовательности, что соответствует режиму чтения по первому адресу информации, записанной ранее в матричные регистры 78 хранения блоков 37 памяти теста всех узлов 9.1 согласования, которая с выходов блоков 37 памяти теста поступает на входы элементов И 36. На этом подготовка блоков устройства к работе в данном режиме проверки заканчивается. Проверка объекта 103 контроля осуществляется путем циклического формирования стимулирующих воздействий и оценки его реак- 5 ций, причем цикл контроля задается контроллером адреса измерительными импульсами Счит., СИ и Строб, частота следования которых задается

0

10

20

регистром 52 хранения и совпадает с рабочей тактовой частотой объекта 103 контроля. Режим динамического тестирования начинается по команде Запуск 1, которая устанавливает триггер 53 контроллера 10 адреса в единичное состояние, при этом запускается генератор 51 импульсов и на выходе формирователя измерительных импульсов начинают формироваться импульсы Счит., СИ, Строб. Импульс Счит. задает начало такта контроля. Во всех узлах 9.1-9.П согласования импульс Счит. в регистраторах 39 неисправности устанав- 5 ливает триггеры 73 неисправности в единичное состояние и осуществляет стробирование информации, приходящей на входы элементов И 36 от блоков 37 памяти теста, при этом коды зна- коперемен, записанные в блоках 37 памяти теста по адресу, соответствующему первому тестовому набору, через элементы И 36 и ИЛИ 32 поступают на счетные входы триггеров 33, которые пре;образуют знакоперемены в реальные тестовые сигналы. При этом если узел 9.1 согласования является входным, то тестовый сигнал с выхода счетного триггера 33 поступает на уп-ЗО равляющий вход аналогового ключа 34, который в зависимости от уровня входного сигнала О и 1 пропускает на выход, соединенный через коммутатор 31 с информационным входом j, контактом объекта 103 контроля, уро- веиь О от ЦАП 12 или уровень 1 от ЦАП 38 данного узла 9.1 согласования. Сигнал Счит определяет по своему переднему фронту момент подачи . тестовых сигналов на информационные выходы.устройства. Если объект 103 контроля является синхронным цифровым узлом, то его синхро- вход соединяется с выходом СИ конт-. роллера 10 адреса (для асинхронных схем выход СИ контроллера 10 адреса не используется). После прихода на информационные входы объекта 103

роль сигналов реакций методом амплитудной и временной селекции, при этом любой выходной сигнал на каждом такте контроля может быть забракован 5 как по амплитуде, так и по времени появления. Сигналы реакций (Up) поступают через коммутаторы 31 на входы компараторов 35, которые осуществляют амплитудную селекцию методом сравнения амплитуды сигналов реакций

25

40

45

с эталонными опорными уровнями сигналов I Ug и О UOP , поступающими на входы компараторов 35 от ЦАП преобразователей 38 и 13, при этом на единичном выходе компаратора 35 присутствует 1, если выполняется условие Up UQ , и уровень О, если и , , а на нулевом выходе компаратора 30 находится уровень 1, если выполняется условие , и уровень О, если . Сигналы с единичного и нулевого выходов компараторов 35 поступают в каждом узле 9.1 согласования на входы регистраторов 39 неисправности, которые по сигналу Строб осуществляют временную селекцию этих сигналов. Б данном режиме от блоков 40 уставок поступают уровни 0 на входы Контр.аналог. регист- fpaTopoB 39 неисправности, которые запрещают селекцию сигналов на элементе 75 И и разрешают ее на элементе 76 И. Сигналы с выходов счетных триггеров 33 задают уровень сигнала .реакции (О или 1), ожидаемый на данном такте контроля, в каждом узле 9.1 согласования, при этом., если счетный триггер 33 находится в единичном состоянии и в момент действия сигнала Строб на единичном выходе компаратора 35 присутствует уровень 1, на выходе элемента И 74 появляется сигнал, устанавливающий триггер 73 в нулевое состояние, и, если счетный триггер 33 находится в нулевом состоянии и в момент действия сигнала Строб на нулевом выходе компаратора 35 присутствует уровень 1, на выходе элемента И 76

появляется сигнал, устанавливающий контроля стимулирующих сигналов и на ся

.. .. - триггер 73 в нулевое состояние, что

его синхровход сигнала СИ с контроллера 10 адреса на выходе объекта 103 контроля с определенной задержкой появляются сигналы реакций.

в обоих случаях соответствует исправной работе заданного выхода объекта 103 контроля на данном такте.

При наличии нулевого уровня сиг- Ранее запрограммированные как вы- 55 нала на единичном или нулевом выходе ходные узлы 9.1 согласования, подклю- компаратора 35 в момент действия сиг- чённые к выходам объекта 103 контро- нала Строб при описанных режимах, ля, осуществляют параллельньй конт- что мбжет быть при невыполнении уело10

5 ЗО j,

0974. . 12

роль сигналов реакций методом амплитудной и временной селекции, при этом любой выходной сигнал на каждом такте контроля может быть забракован 5 как по амплитуде, так и по времени появления. Сигналы реакций (Up) поступают через коммутаторы 31 на входы компараторов 35, которые осуществляют амплитудную селекцию методом сравнения амплитуды сигналов реакций

20

5 О ,

5

0

5

с эталонными опорными уровнями сигналов I Ug и О UOP , поступающими на входы компараторов 35 от ЦАП преобразователей 38 и 13, при этом на единичном выходе компаратора 35 присутствует 1, если выполняется условие Up UQ , и уровень О, если и , , а на нулевом выходе компаратора 30 находится уровень 1, если выполняется условие , и уровень О, если . Сигналы с единичного и нулевого выходов компараторов 35 поступают в каждом узле 9.1 согласования на входы регистраторов 39 неисправности, которые по сигналу Строб осуществляют временную селекцию этих сигналов. Б данном режиме от блоков 40 уставок поступают уровни 0 на входы Контр.аналог. регист- fpaTopoB 39 неисправности, которые запрещают селекцию сигналов на элементе 75 И и разрешают ее на элементе 76 И. Сигналы с выходов счетных триггеров 33 задают уровень сигнала .реакции (О или 1), ожидаемый на данном такте контроля, в каждом узле 9.1 согласования, при этом., если счетный триггер 33 находится в единичном состоянии и в момент действия сигнала Строб на единичном выходе компаратора 35 присутствует уровень 1, на выходе элемента И 74 появляется сигнал, устанавливающий триггер 73 в нулевое состояние, и, если счетный триггер 33 находится в нулевом состоянии и в момент действия сигнала Строб на нулевом выходе компаратора 35 присутствует уровень 1, на выходе элемента И 76

ВИЯ

13

или

или при большой задержке сигнала реакции на выходе объекта 103 контроля, элемент И 74 или 76 не формируют сигнал сбрса триггера 73 и он остается в единичном состоянии, запоминая наличие неисправности (сбоя) на данном такт коцтроля в данном узле 9.i согласования.

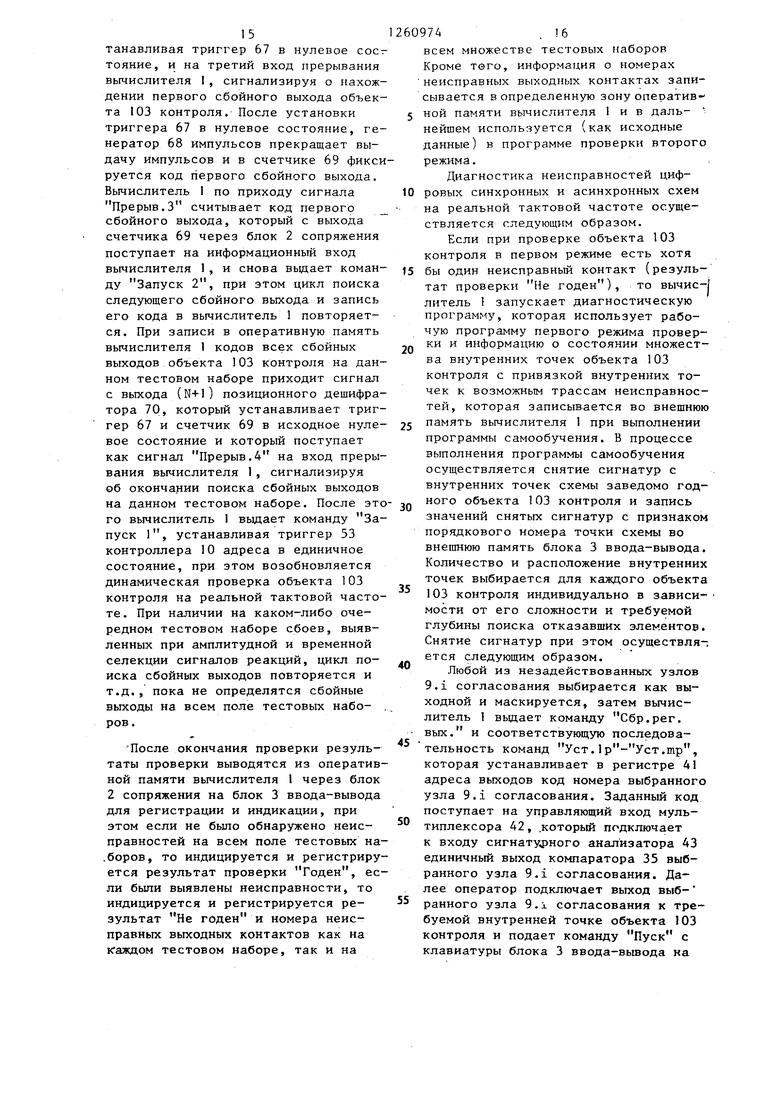

При заданной частоте подачи тестовых наборов задержка распространения сигналов реакций должна быть дл асинхронных схем не более С 1 ,, для синхронных схем, срабатывающих по переднему фронту синхроимпульса, не более о2 и синхронных схем, сра- батьшающих по заднему фронту синхроимпульса, не более Z3 (фиг. 10).

При наличии задержек по ТУ для какого-либо выхода объекта 103 контроля больше перечисленных необходимо данный канал измерения замаскировать и в дальнейшем осуществить его

проверку на пониженной частоте. После 25 тий вход прерьюания вычислителя 1 окончания сигнала Строб контроллер 10 адреса выдает сигнал Опрос, который опрашивает состояние триггеров 73 регистраторов 39 неисправности всех узлов 9.1 согласования. Сигнал Опрос поступает на первые входы элементов ИЛИ 72.1-72.N блока 11 идентификации неисправности и с их выходов параллельно поступает на входы Bыб.Nk регистраторов 39 не30

осуществляется идентификация неисправности. При этом вычислитель 1 выходит на подпрограмму поиска неисправности - считывает код номера тестового набора, который с выхода счетчика 49 блока 10 контроллера адреса поступает через блок 2 сопряжения на информационный вход вы числителя 1, вьщает команду Запус 2 и переходит в режим ожидания си

Исправности всех узлов 9.1-9.П согла- налов прерьгоания. По команде За

сования. Если в одном или нескольких узлах 9.1 согласования триггеры 73 В регистраторах 39 неисправности находятся в единичном состоянии и при этом данный узел 9.1 согласования незамаскирован и выбран как выходной, то в момент действия сигнала Опрос на выходе элементов И 74 и 77 узлов 9.1 согласования появляются сигналы Сбой. Сигналы Сбой со всех узлов 9.1 согласования объеди-- няются на элементе И 71 блока II идентификации неисправностей и при наличии хотя бы одного сигнала Сбой иа- выходе элемента И 71 появляется сигнал Прерыв.З, который; в контроллере 10 адреса устанавливает триггер запуска 53 в нулевое состояние, запрещая дальнейшее формирование измерительных импульсов, а также поступает на третий вход прерывания вычислителя 1, сигнгшизируя о наличии сбоя на данном тестовом наборе.

14

При отсутствии неисправностей на данном тестовом наборе сигналы Сбой по сигналу Опрос не вырабатываются и формируются измерительные импульсы для следующего такта контроля и т.д., пока не будет проверен объект 103 контроля на всем поле тестовых наборов. После прихода импульса Опрос на последнем тестовом наборе счетчик 48 контроллера 10 адреса вырабатывает сигнал переноса, который устанавливает триггер запуска 53 в нулевое состояние, запрещая даль- нейшее формирование измерительных импульсов, а также поступает на второй вход прерывания вычислителя 1, сигнализируя об окончании проверки объекта 103 контроля на заданном поле тестовых наборов.

При обнаружении неисправности на каком-нибудь тестовом наборе после остановки динамического тестирования . и прихода сигнала Прерыв.З на третий вход прерьюания вычислителя 1

осуществляется идентификация неисправности. При этом вычислитель 1 выходит на подпрограмму поиска неисправности - считывает код номера тестового набора, который с выхода счетчика 49 блока 10 контроллера адреса поступает через блок 2 сопряжения на информационный вход вычислителя 1, вьщает команду Запуск 2 и переходит в режим ожидания сигналов прерьгоания. По команде За

пуск 2 триггер 67 блока 1I идентификации неисправностей устанавливается в единичное состояние и запускает генератор 68 импульсов, сигналы с которого поступают на счетный вход счетчика 69. При последовательном увеличении кода в счетчике 69 на выходах позиционного дешифратора 70 последовательно формируются сигналы Выб..ЫК опроса, которые через вторые входы элементов ИЛИ 72.1-72.N поступают на входы элементов И 77 регистраторов 39 неисправности соответствующих узлов 9.1 согласования. При достижении первого незамаскированного выходного узла 9.1 согласования, у которого в регистраторе 39 неисправности триггер 73 находится в единичном состоянии, на выходе элемента И 77 формируется сигнал Сбой, который поступает на вход элемента ИЛИ 71 в блоке 11 идентификации результатов контроля, ус15

танавливая триггер 67 в нулевое состояние, и на третий вход прерывания вычислителя I, сигнализируя о нахождении первого сбойного выхода объекта 103 контроля. После установки триггера 67 в нулевое состояние, генератор 68 импульсов прекращает выдачу импульсов и в счетчике 69 фиксируется код первого сбойного выхода. Вычислитель I по приходу сигнала Прерыв.З считывает код первого сбойного выхода, который с выхода счетчика 69 через блок 2 сопряжения поступает на информационный вход вычислителя 1, и снова выдает команду Запуск 2, при этом цикл поиска следующего сбойного выхода и запись его кода в вычислитель 1 повторяется. При записи в оперативную память вычислителя 1 кодов всех сбойных выходов объекта 103 контроля на данном тестовом наборе приходит сигнал с выхода (N+I) позиционного дешифратора 70, который устанавливает триггер 67 и счетчик 69 в исходное нулевое состояние и который поступает как сигнал Прерыв.4 на вход прерывания вычислителя 1, сигнализируя об окончании поиска сбойных выходов на данном тестовом наборе. После этого вычислитель I вьщает команду Запуск 1, устанавливая триггер 53 контроллера 10 адреса в единичное состояние, при этом возобновляется динамическая проверка объекта 103 контроля на реальной тактовой частоте. При наличии на каком-либо очередном тестовом наборе сбоев, выявленных при амплитудной и временной селекции сигналов реакций, цикл поиска сбойных выходов повторяется и т.д., пока не определятся сбойные выходы на всем поле тестовых набо- ров.

После окончания проверки результаты проверки выводятся из оперативной памяти вычислителя 1 через блок 2 сопряжения на блок 3 ввода-вывода для регистрации и индикации, при этом если не было обнаружено неисправностей на всем поле тестовых на- .боров, то индицируется и регистрируется результат проверки Годен, если были выявлены неисправности, то индицируется и регистрируется результат Не годен и номера неисправных выходных контактов как на к аждом тестовом наборе, так и на

60974. 16

всем множестве тестовых наборов Кроме того, информация о номерах неисправных выходных контактах записывается в определенную зону оператив- 5 ной памяти вычислителя I и в дальнейшем используется (как исходные данные) в программе проверки второго режима.

Диагностика неисправностей циф- 10 ровых синхронных и асинхронных схем на реальной тактовой частоте осуществляется следующим образом.

Если при проверке объекта 103 контроля в первом режиме есть хотя 15 бы один неисправный контакт (результат проверки Не годен), то вычис-| литель I запускает диагностическую программу, которая использует рабочую программу первого режима проверки и информацию о состоянии множест0

ва внутренних точек объекта 103

контроля с привязкой внутренних точек к возможным трассам неисправностей, которая записывается во внешнюю

5 память вычислителя 1 при выполнении программы самообучения. В процессе выполнения программы самообучения осуществляется снятие сигнатур с внутренних точек схемы заведомо годного объекта 103 контроля и запись значений снятых сигнатур с признаком порядкового номера точки схемы во внешнюю память блока 3 ввода-вывода. Количество и расположение внутренних точек выбирается для каждого объекта 103 контроля индивидуально в зависимости от его сложности и требуемой глубины поиска отказавших элементов. Снятие сигнатур при этом осуществля-, ется следующим образом.

Любой из незадействованных узлов 9.1 согласования выбирается как выходной и маскируется, затем вычислитель 1 выдает команду Сбр.рег. вых. и соответствующую последова тельность команд Уст..тр, которая устанавливает в регистре 41 адреса выходов код номера выбранного узла 9.1 согласования. Заданный код поступает на управляющий вход мультиплексора 42, .который подключает к входу сигнату4 ного анализатора 43 единичный выход компаратора 35 выбранного узла 9.1 согласования. Далее оператор подключает выход выб5 ранного узла 9.1 согласования к требуемой внутренней точке объекта 103 контроля и подает команду Пуск с клавиатуры блока 3 ввода-вьшода на

0

0

1 7

вычислитель 1, который после получения команды оператора маскирует все выходные блоки 9 согласования для исключения остановки тестовой программы при обнаружении ошибок, подает команду Сбр.СА и запускает програм .му динамического тестирования первого режима. При этом на входы объекта 103 контроля аналогично первому режиму, поступают входные тестовые последовательности, которые генерируют в заданной внутренней точке конечную последовательность сигналов, которую сигнатурный анализатор 43, стробируе мый сигналом Строб от контроллера 10 адреса, на реальной тактовой частоте преобразует в код сигнатуры. При этом компаратор 35 выбранного узла 9. согласования осуществляет амплитудную селекдию последовательности сигналов в заданной внутренней точке, а сигнал Строб --временную

селекцию. После окончания динамического тестирования по приходу сигнала Прерыв.2 вычислитель 1 считывает код сигнатуры, который поступает на его информационный вход с выхода сигнатурного анализатора 43 через блок 2 сопряжения и вьщает его с признаком внутренней точки на внешнюю память блока 3 ввода-вывода. После считывания аналогично описанному кодов сигнатур для всех выбранных внутренних точек объекта 103 контроля и занесения их во внешнюю память необходимо занести во внешнюю память вычислителя 1 признаки всех возможных трасс неисправностей. Для каждого выходного контакта определяется связанное подмножество выбранных точек внутри объекта 103 контроля, находящихся на пути от выходного контакта до входных и имеющих логическую связь с входным.

Множество Q; входных контактов, имеющих логическую связь с i-M выходным контактом, зависит от дерева логического графа объекта 103 контроля, а множество М групп Q; оп- р деляется количеством выходных контактов объекта 103 контроля Трассы возможных неисправностей вносятся оператором с клавиатуры блока 3 ввода-вывода следующим образом.

Сначала записывается номер i-ro выходного контакта потом по очереди все номера точек,, расположенные между ним и 3 -м входным контактом, а

6097418

потом номер 3 -го входного контакта После этого записывается следующая трасса неисправности и т.д., пока не будут записаны все возможные трас- 5 сы неисправности для 1-го выходного контакта. После этого записываются подмножества возможных трасс неисправностей для другого выходного контакта и т.д., пока не будут запи0 саны все возможные трассы неисправностей для множества М выходных контактов. Подмножества точек внутри возможных трасс неисправностей могут быть пересекающимися, т.е. некоторые

5 точки могут принадлежать нескольким трассам возможных неисправностей. На этом программа самообучения заканчивается. Запись исходной информации о состоянии внутренних точек

0 конкретного объекта контроля и расположения их в трассах неисправностей производится один раз и в дальнейшем хранится на внешнем носителе блока 3 ввода-вывода.

5 f

После запуска диагностической

программы вычислитель 1 обращается в область оперативной памяти, где хранится информация о номерах неисправных выходных контактах, определенных при проверке в первом режиме, вьщеляя подмножество трасс неисправностей Q,; для подмножества Р выходных контактов из множества всех возможных трасс неисправностей Q для мно- 5 жества М выходных контактов. После этого вычислитель 1 программирует регистр адреса выходов 41, код адреса которого с выкода поступает на управляющий вход мультиплексора 42, который подключает единичный выход компаратора 35 узла 9.1 согласования, соединенного с i-м выходным контактом из подмножества Р, к входу сигнатурного анализатора 43. Далее вычислитель 1 маскирует все выходные узлы 9.1 согласования для исключения остановки тестовой программы при обнаружении ошибок, подает команду Сбр.СА, устанавливая сигнатурный анализатор 43 в нулевое состояние, и запускает программу динамического тестирования первого режима. На входы объекта 103 контроля аналогично первому режиму поступают входные тесто0

0

5

0

5

вые последовательности, которые генерируют на его выходных контактах конечную последовательность сигналов (ответных реакций), которую сигнатурный анализатор 43, стробируемый сигналом Строб от контроллера 10 адреса на реальной тактовой частоте, преобразует в код сигнатуры. При эт компаратор 35 выбранного узла 9,1 согласования осуществляет амплитудную селекцию последовательности выходных сигналов, а сигнал Строб контроллера 10 адреса - временную селекцию. После окончания динамического тестирования по приходу сигнала Прерыв.2 вычислитель 1 через блок 4 дешифраторов выдает команды Сбр.РСНК и Зап. в РСНК (на блок 8), при этом в регистр 44 с выхода сигнатурного анализатора 43 записывается значение кода сигнатуры для выбранного i-ro неисправного выходного контакта объекта 103 контроля. Значение кода сигнатуры для i-ro выходного контакта может быть любым и зависит от места и типа неисправности. После этого вычислитель 1 через блок 4 дешифраторов подает команды Запр.вх., Маскир. на контроллер 10 адреса и информационную команду, соответствующую номеру 1-го выходного контакта, на блок 40 уставок J-ro узла 9 согласования, с выхода элемента И 92 блока 40 уставок которого поступает сигнал на запрещающий вход элемента И 36, при этом запрещается прохождение сигнало с выхода блока 37 памяти теста данного узла 9.J согласования на счетный вход счетного триггера 33. Далее вычислитель 1 снова запускает программу динамического тестирования первого режима. В этом случае генерируются по всем входам, кроме выбранного 1-го, те же входные последовательности, что и в предьщущем случае. При этом, если на трассе от

входного 1-го до вьрсодного i-ro кон- такта нет неисправностей, в сигнатурном анализаторе 43 фиксируется код сигнатуры, отличный от предьщущего, .так как на 1-м входном контакте присутствует постоянный уровень сигнала вместо ранее подаваемой на него последовательности сигналов, а если на этой трассе имеется одна или несколько неисправностей типа конституэнта О или конституэнта 1, в сигнатурном анализаторе 43 фиксируется код сигнатуры, равный предыдущему, так как отключение 1-го входа объекта 103 контроля в случае отсутствия сходящихся разветвлений

0

5

0

5

0

5

0

5

5

в дереве логического Графа множества Q; не приводит к измерению выходной последовательности на выходе i-ro неисправног о контакта. После этого вычислитель 1 через блок 4 де-- шифраторов- вьщает команды Сбр.РДС и Зап.РДС на блок 8 анализа. При этом с выхода сигнатурного анализатора 43 в регистр 45 заносится значение кода диагностической сигнатуры входного контакта. Если коды сигнатур в регистрах 43 и 45 равны, то после подачи команды Стр.сх.ср. элемент 46 сравнения выдает сигнал, поступающий на первый вход прерывания вычислителя 1, сигнализируя о наличии неисправностей на проверяемой трассе. Отсутствие данного сигнала указывает на отсутствие неисправностей на данной трассе. После перебора всех входных контактов множества Q, для выходного i-ro неисправного контакта вычислитель 1 программирует в регистре 41 адрес следующего неисправного контакта, для которого проводятся те же операции, что и для i-ro неисправного контакта с целью выявления трасс неисправности и т.д., пока не будут обработаны все подмножества Р выходных неисправных контактов. Информация о всех выявленных неисправных трассах заносится в оперативную память вычислителя 1 и используется при поиске отказавших элементов с заданной глубиной поиска в диалоговом режиме работы оператора с диагностической программой. После этого информация о взаимном расположении, признаках и состоянии внутренних точек первой выявленной трассы неисправности, ранее записанная при выполнении программы самообучения на внешнем носителе блока 3 ввода-вывода, вводится в оперативную память вычислителя 1, при этом запускается диалоговая диагностическая программа, ко- -торая дает целеуказания оператору, в ыдавая на дисплей блока 3 ввода- вывода номер первой точки проверяемой трассы. Оператор подключает к указанной точке трассы вьгход одного из незадействованных узлов 9.i согласования и выдает команду Пуск с клавиатуры блока 3 ввода-вывода, п)н этом аналогично описанному при выполнении программы самообучения осуществляется программирование выбранного узла 9.i согласования, съем и

21

запись в оперативную память вьтис- лителя 1 кода сигнатуры данной точки трассы. Диалоговая диагностическая программа задает порядок съема кодов сигнатур в точках проверяемой трассы на основе метода полбвинного деления, при этом начальная точка съема кода сигнатуры приходится на входной контакт проверяемой трассы. На основании анализа методом сравнения снятых кодов сигнатур с эталонным в соответствующих точках трассы диалоговая диагностическая программа делает вывод о направлении движения по трассе. Вначале задается движени методом деления участков на половину в направлении от входного контакта к выходному. При достижении первой точки, у которой реальный код сигнатуры не совпал с эталонным, делается вьгоод о наличии неисправности между данной точкой и предыдущей, после чего направление движения по трассе методом деления участков на половину меняется на противоположное и т.д., пока не будет определено место неисправности с заданной глубиной поиска для данной неисправной трассы. Вычислитель 1 запоминает в оперативной памяти признак места неисправности и переходит к поиску неисправностей на других выявленных трассах неисправностей, не имеющих логических связей с данной неисправной трассой и т.д., пока не будут определены все неисправности. После этого вычислитель 1 выдает на 5лок 3 ввода-вывода информацию о местах неисправностей ца индикацию и регистрацию. При поиске неисправностей с максимально возможной глубиной поиска,

когда точки снятия сигнатур расположены на всех входах и выходах элементов схемы объекта 103 контроля, можно определить не только место неисправности, но и характер данной неисправности несоответствие амплитуды сигнала требуемой в данной точке цепи или несоответствие времени задержки сигнала требуемой в данной точке цепи, обрыв цепи, замыкание цепи на землю, замыкание депи на питание, замыкание цепей между собой. Несоответствие амплитуды сигналов требуемой и наличие задержек сигналов, больших требуемых в данной це- .пи, идентифицируется отличием снятой и эталонной сигнатур во всех точках цепи. Обрью цепи идентифицируется

6097422

различием сигнатур на выходе какого- либо элемента и на входе (входах) непосредственно связанного с ним другого элемента. Замыкание цепи на

5 землю идентифицируется наличием нулевой сигнатуры как на выходе какого-либо элемента, так и на входах непосредственно связанных с ним элементов. Замыкание цепи с питанием

0 идентифицируется наличием единичной сигнатуры для данного объекта 03 контроля как на выходе какого-либо элемента, так и на входах непосредственно связанных с ним элементов,

5 Замыкание цепей между собой идентифицируется наличием одинаковых сигнатур на цепях, реально не связанных друг с другом, причем эти сигнатуры отличаются от реальных для первой и

0 второй цепи. При такой глубине поиска отказавших элементов вычислитель 1 вьздает на блок 3 ввода-вывода, кроме информации о месте неисправности, также информацию о типе не5 исправности. На этом диагностика неисправностей цифровых синхронных и асинхронных схем на реальной тактовой частоте заканчивается.

0 Устройство в режиме функциональной статической проверки по методу Годен- не годен и диагностики неисправностей аналого-цифровых схем работает следующим образом.

r Особенностью организации проверки и диагностики аналого-цифровых схем является то, что входные стимулирующие сигналы для них задаются циклически в виде ступенчатых функ0 ций сложной формы независимо друг от друга и параллельно по всем входам, а вьгходньми сигналами являются обычные логические двухуровневые сигналы. Исходя из этого строится

алгоритм проверки. Сначала осуществляется подготовка блоков устройства к работе. Вычислитель 1 в соответствии с введенной в его оперативную память программой осуществляет

аналогично описанному для цифровых схем распределение узлов 9.1 согласования на входные и выходные, программирование блока 6 программируемых источников питания, программирование уровней U(,n Щ1 38, задающих эталон- 55 ный уровень 1 в выходных узлах

9.1-9.П согласования, программирование уровня Ugj в ЦАП 13, задающем эталонный уровень О. После этого

50

23

через блок 4 дешифраторов подается команда Сбр.сч.тр., которая поступает на нулевые установочные входы счетных триггеров 33 всех узлов 9.1- 9.П согласования, устанавливая их в нулевое состояние, и последовательность информационных команд, которые устанавливают счетные триггеры 33 во входных узлах 9.1 согласования в единичное состояние, .а в выходных - в состояния, соответствующие первому выходному тестовому набору. Методика установки требуемого тестового набора в данном режиме отличается от режима проверки цифровых схем тем, что сигналы знакоперемен подаются на счетные входы триггеров 33 не с блоков 37 памяти теста, а с блока 4 дешифраторов в виде информационных команд, которые через элемент ИЛИ 32 поступают на счетные входы триггеров 33 соответствующих узлов 9.1 согласования, устанавливая их в состояние, противоположные предыдущему.

В каждом входном узле 9.1 согласования в соответствии с требуемой ступенчатой функцией на данном тестовом наборе программируются ЦАП 38, с выходов которых аналоговые уровни Ujj поступают на выход аналогового ключа 34, так как счетные триггеры 33 всех входных узлов 9.1 согласования находятся в единичном состоянии, и далее через коммутатор- 31 на входы объекта 103 контроля. Сигналы реакций объекта 103 контроля в виде логических двухуровневых сигналов поступают на входы компараторов 35 узлов 9 согласойания, выбранных ранее выходными. Компараторы 35 осуществляют амплитудную селекцию сигналов реакций аналогично описанному при проверке цифровых схем. По командам Уст.3. Уст.З.п в контроллере 10 адреса устанавливается код номера первого тестового набора в счетчике 49 адреса, по команде Уст.тр.неиспр. триггеры 73 в регистраторах 39 неисправности всех узлов 9.1-9.П согласования устанавливаются в единичное соетояние, по команде Строб в контроллере IО адреса на выходе элемента 65 ИЛИ формируется сигнал Строб, который поступает на регистраторы 39 неисправности, осуществляя временную селе кцию сигналов, поступающих

6097424

с единичных и нулевых выходов ком- параторрв 35 выходных узлов 9.1 согласования аналогично описанному для цифровых схем, и запуская гёнера5 тор 66 одиночных импульсов контроллера 10 адреса, на выходе которого формируется сигнал Опрос. Если после амплитудной и временной селекции сигналов реакций триггеры 73 в

10 некоторых узлах 9.1 согласования остаются в единичном состоянии, то по сигналу Опрос, приходящему на блок 1I идентификации результатов контроля, осуществляется поиск неисправных

15 выходных контактов объекта 103 контроля аналогично описанному для циф- ровЫх схем. Если триггеры 73 неисправности всех выходных узлов 9.1 согласования находятся в нулевом.

20 состоянии, то вычислитель I, который после вьщачи команды Строб перешел в режим ожидания сигналов прерывания , не получив этих сигналов прерывания, переходит к ранее прерванной

5 программе. На этом цикл контроля на первом тестовом наборе заканчивается. Вычислитель 1 устанавливает с помощью информационных команд в выходных узлах 9.1 согласования счетные триг0 геры 33 в состояния, соответствующий второму тестовому набору, в каждом входном узле 9.1 согласования перепрограммирует ЦАП 38 в соответствии с требуемой ступенчатой функцией, по командам Уст.З. .3.п устанавливает в контроллере 10 адреса в счетчике 49 код номера второго тестового набора и подает команды Уст.тр.неиспр. и Строб, повторяя цикл контроля на втором тестовом, наборе, и т.д., пока не будет осуществлена проверка на всем поле

тестовых наборов. I

Диагностика неисправностей анало5 го-цифровьгх схем осуществляется для цифровой части схемы аналогично описанному для цифровых схем методами сигнатурного анализа. Аналоговая часть схемы проверяется с помощью

0 подключения блока 5 измерителей к I внутренним точкам схемы, при этом для подключения входа блока 5 измерителей оператором к внутренним точкам схемы используется свободньй узел .

5 9 согласования, замаскированный и выбранный как выходной, причем поиск неисправностей можно осуществлять как визуально, по форме ступенчатой

5

20

25

ункции при зацикливанин nporpawibi ко 1троля с помощью осциллографа, входящего в состав блока измерителей так и автоматически в диалоговом режиме работы оператора с л.иагиостичес- , кой программой при пошаговом прогоне рабочей программы проверки с подключением к внутренним точкам схемы, в которых необходимо измерять анаоговые уровни цифрового вольтметра, о входящего в состав блока измеритее и.

Предлагаемое устройство в режиме ункциональной статической проверки по методу Годен-не годен и диаг- 5 остики неисправностей цкфроаналого- ых схем работает следующим образом.

Особенностью организации проверки и диагностики цифроаналоговых схем является то, что входные стимулы для них задаются в виде обычных логических двухуровневых сигналов, а выходными являются сигналы в виде ступенат 1х функций сложной формы, формируемые независимо друг от друга и параллельно по всем каналам. Исходя из этого строится алгоритм проверки. Сначала осуществляется подготовка блоков устройства к работе. Вычислитель 1 в соответствии с введенной в оперативную память программой

осуществляет аналогично описанному для цифровых схем распределение узлов 9.1 согласования на входные и выходные, программирование блока 6 35 программируемых источников питания, программирование уровня Ug в ЦАП 38, задающих уровень 1 стимулирующих сигналов во входных блоках 9 согласования, программирование уровня и jjj ДАЛ 12, задающего уровень логического О стимулирующих сигналов во входных узлах 9.i согласования. По команде Маскир. в контроллере 10 адреса устанавливается в единичное состояние триггер 56, .сигнал с выхода которого подается на вход элементов И 88 и блоков 40 уставок всех узлов 9.1-9.П согласования. После подачи информационных команд, соответствующих номерам всех выходных узлов 9.1 согласования, и затем команды Контр.аналог. триггеры 83 и 86 блока 40 уставок всех выходных узлов 9.1 согласования устанав-. 55 ливаются в единичное состояние. После подачи команд Сбр.маскир. и Сбр.реж. триггеры 83 в блоках 40

30

40

45

50

0

5

, о

5

5 5

0

0

5

0

уставок и трип ер 56 в контроллере 10 адреса устанавливаются в нулевое состояние. После этого подается команда Сброс сч.тр., которая устанавливает счетные триггеры 33 всех узлов 9.1-9.П согласования в нулевые состояния, и последовательность информационных команд, которые устанавливают счетные триггеры 33 во входных узлах 9.i согласования в состояния, соответствующие первому тестовому набору. Далее в каждом вькодном узле 9 согласования в соответствии с требуемой ступенчатой функцией на данном тестовом наборе программируются ЦАП 38, при этом эталонные а1 алоговые уровни U(,n должны задаваться больщими ожидаемой величины аналогового сигнала реакции Up на величину uU -дЬ , где uUp - максимально допустимое отклонение измеряемой величины Up от номинала; iUj, - погрешность измерения компаратора 35. Сигналы реакций U., с выходов объекта 103 контроля в виде сту- пенчать х функций сложной формы поступают на информационные входы компараторов 35 выходных узлов 9.1 согласования, которые осуществляют параллельную амплитудную селекцию сигналов реакции. По командам Уст.З..З.п в контроллере 10 адреса устанавливается код номера первого такта контроля первого тестового набора в счетчике 49 адреса, по команде Уст.тр.неиспр. триггеры 73 в регистраторах 39 неисправности всех узлов 1.1-9.П согласования устанавливаются в единичное состояние, по команде

Строб в контроллере 10 ;.д- реса на выходе элемента ItTbi 65 формируется сигнал Строб, ко- торьш поступает на регистрато- ры 39 неисправности, осущест,вляя временную селекцию сиг- . налов, поступающих с единичных выходов компараторов 35. Сигналы с нулевых выходов компаратора 35 не участвуют в селекции, так как единичный уровень сигнала на входе Контр.аналог. регистратора 39 неисправности разрешает селекцию сигналов на элементе И 75 и запрещает ее на элементе И 76. Нулевые уровни сигналов, поступающие с выходов триггеров 33 во всех выходных.узлах 9.1 согласования, разрешают селекцию сигналов с инверсных единичных выходов

27

компараторов ЗЬ через элемент И 75 Компараторы 35 в выходных блоках 9 согласования, у которых - р д,, фор- мируют на инверсных единичных выходах единичные уровни сигнала, которые в момент действия сигнала Строб через элемент И 75 устанавливают триггеры 73 в нулевые состояния. Если в каком-либо выходном узле 9.1 согласования Ь р U , то его компаратор 35 на инверсном выходе имеет нулевой уровень сигнала и его триггер 73 остается в единичном состоянии. Таким образом определяется годность аналоговых уровней сигналов реакций по верхнему допустимому уровню. Опрос триггеров 73 в выходны

узлах 9.1 согласования и поиск сбрй- 1 .-

пых выходных контактов осуществляется, как при проверке аналогово-циф- ровых схем. После этого определяется годность аналоговых уровней сигналов реакций по нижнему допустимому уровню. BQ всех выходных узлах 9.1 согласования с помощью информационных команд все счетные триггеры 33

устанавливаются в единичные состояния, а во входных узлах 9.1 согласования все счетные триггеры 33 остаются в том же состоянии, соответствующем первому тестовому набору. В каждом выходном узле 9.1 согласования 1Щ1 38 перепрограммируются таким образом, чтобы эталонные, аналоговые уровни UOD были меньшими или ожидаемой величины аналогового сигнала реакции U. на величину iUp-AL, после этого по командам Уст.3. Уст.З.п программируется номер второго такта.контроля первого тестовог набора, подается команда Уст.тр.не- испр., устанавливающая триггеры 73 всех узлов 9 согласования в единичные состояния, и команда Строб., по которой организуется временная селекция сигналов в регистраторах 39 неисправности всех выходных узлов 9 согласования, при этом единичные уровни сигналов, поступающие с выходов счетных триггеров 33 во всех выходных узлах согласования,.разрешают селекцию сигналов с единичных выходо компараторов 35. Компараторы 35, у которых Up U(j , формируют на единичных выходах единичные уровни сигнала которые в момент действия сигнала Строб через элемент И 74 устанавливают триггеры 73 в нулевые состоя6097428

ния. Если в каком-либо узле 9.1 согласования Ир-1 рп , то его компара- тор 35 на единичном выходе имеет нулевой уровень сигнала и его триг5 гер 73 неисправности остается в единичном состоянии. Опрос триггеров 73 неисправностей и поиск сбойных выходных контактов осуществляется, как при проверке аналого-цифровых

0 схем. В результате на первом тестовом наборе за два такта контроля осуществляется параллельный контроль выходных уровней сигналов реакций по верхнему и нижнему пределам с

5 заданной точностью. После этого во входных узлах 9.1 согласования счетные триггеры 33 устанавливаются в состояния, соответствующие второму тестовому набору, и цикл контроля

0 повторяется и т.д., пока не будет осуществлен контроль выходных аналоговых уровней сигналов на всех тестовых наборах.

Диагностика неисправностей цифро5 аналоговых схем осуществляется как для аналого-цифровых схем.

Блок 14 регистров содержит регистры 80 и 81 хранения, в которые по управляющим сигналам с блока 4 дешиф30 раторов Зап.Рг.Г и Зап.Рг.2 записываются коды, поступающие на входы ЦАП 12 и 13.

Сигнатурный анализатор 43 содержит регистр сдвига 93, в котором получаются сигнатурные свертки, и сумматор 94 по модулю два, суммирующий входной сигнал с содержимым регистра 93 для получения сигнатуры.

Таким образом, применение изобретения позволяет повысить скорость работы устройства при динамическом тестировании цифровых сиихронных и асинхронных схем в 20-30 раз, что обеспечивает проверку данного класса схем на реальной тактовой частоте, а также организовать допусковый параметрический контроль сигналов реакций объектов контроля, представляющих собой фиксированные аналоговые уров- ни сложной формы, оценку годности которых возможно производить паралельно по всем выходам объекта конт1 1 роля по критерию Uo.Up. U. ,

где и UQP - допустимые ниж- НИИ и верхний пределы контролируемого аналогового уровня по 1-му контолируемому выходу, что расширяет ункциональные возможности устройст24

ва. Кроме того, удалось организовать диагностику неисправностей цифровых синхронных и асинхронных схем на реальной тактовой частоте в диалоговом режиме работы с опера 1 ором с точной локализацией места неисцрав- ности и идентификацией ее типа, что также -расширяет функциональные возможности устройства.

о р м у л а изобретения

1 . Устройство для контроля электрических параметров цифровых узлов, содержащее узлы согласования по числу контролируемых параметров, блок программируемых источников питания, блок сопряжения, соединенный первыми информационными входами и выходами соответственно с первыми информационными выходами и входами вычислителя, вторыми информационными входами и выходами - с информационными выхо- т,ами и входами блока ввода-вывода, третьими информационными входами - с информационными выходами блока измерителей, сигнальный вход которого соединен с первыми выходами узлов согласования, вторые выходы и первые входы которых являются стимулирующими выходами и измерительными входами устройства, первь й вход преры- вычислителя соединен с первым выходом блока анализа, информационный вход которого соединен с информационным выходом блока диагностики, информационные которого соединены с третьими выходами узлов согласования, каясдый узел согласования содержит первый элемент И, первый элемент HTOi, блок памяти теста, счетный триггер, коммутатор, соединенный первым, вторым выходами и первым входом с первым, вторым выходами и первым входом узла согласования, третьим выходом - с первым входом компаратора, вторым входом - с выходом аналогового ключа, третьим входом - с первым выходом блока уставок, вторые выходы которого соеди- не ны с информационными входами первого цифроаналогового преобразователя, вьтход которого соединен с первым входом аналогового ключа и вторым входом компаратора, блок диагностики содержит регистр адресов выходов, йходы которот о являются управляющими входами блока диагностики, а выходы соединены с управляющими входами

60974 . 30

мультиплексора, сигнальные входы которого являются информационными входами блока диагностики, а выход является информационным выходом блока 5 диагностики, блок анализа.содержит сигнатурный анализатор, информационный вход которого является информационным входом блока анализа, а выходы соединены с информационными входа- 10 ми регистра сигнатуры неисправного контакта и регистра диагностических сигнатур, вв/ходы которых соединены соответственно с первыми и вторыми входами элемента сравнения, выход 15 которого является первым выходом блока анализа, соединенного управ- л гюшими входами с управляющими входами сигнатурного анализатора, регистра сигнатуры неисправного контак20 та и регистра диагностических сигнатур, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения контроля и диагностики 5 на реальной тактовой частоте в реальном масштабе времени, а также двухпорогового контроля уровней на любом из выводов контролируемого цифрового узла, в него введены конт- 0 роллер адреса, блок идентификации неисправностей, блок дешифраторов, два цифроаналоговых преобразователя, блок регистров, а в каждый узел согласования дополнительно введен реги, стратор неисправности, причем выходы программируемых источников питания являются выходами питающих напряжений устройства, первый выход контроллера адреса является выходом синхронизации устройства, второй вьгход контроллера адреса соединен с вторыми входами узлов согласования, третьи и четвертые выходы - с третьими и четвертыми входами узлов согласования, пятые выходы - с пятыми входами узлов согласования, с четвертыми информационными входами блока сопряжения и информационными входами блока регистров, шестой выход - с шестыми входами узлов согласования и стробирующим входом блока анализа, седьмой выход - с первым входом блока идентификации неисправностей, а восьмой вьгход - с вторым входом прерывания вычислителя, первый выход блока идентификации неисправностей соединен с первым входом контроллера адреса и третьим входом прерывания вычислителя, второй выход0

5

0

5

с четвертым входом прерывания вычислителя, третьи выходы - с соответствующими седьмыми входами каждого узла согласования, а четвертые

выходы блока идентификации неис-

.

правностеи соединены с пятыми информационными входами блока сопряже- HHHj первые выходы блока дешифраторов соединены с управляющими входами блока программируемых источников питания, вторые выходы - с управляющими входами блока измерителей, третьи выходы - с вторыми входами контроллера адреса, четвертые выходы - с восьмыми входами узлов согласова- НИН, пятые выходы - с девятыми входами соответствующих узлов согласования, шестые выхода. - с вторым входом блока идентификации неисправносте третьим входом контроллера адреса и десятыми входами узлов согласования, седьмые выходы - с одиннадцатыми входами узлов согласования, восьмой выход - с двенадцатыми входами узлов согласовайия, девятый выход - с тре- тьим входом блока идентификации неисправностей, десятые выходы - с управляющими входами блока регистров, одиннадцатые выходы - с управляющими входами блока диагностики, а две- надцатые выходы блока дешифраторов соединены с управляющими входами блока анализа, первый и второй выходы блока регистров соединены соответственно с информационными входами второго и третьего цифроаналоговых преобразователей, выходы которых соединены соответственно с тринадцатыми и четырнадцатыми входами узлов согласования, соединенных четвертыми выходами с.соответствующими четвертыми входами блока идентификации неисправностей, блок сопряжения соединен третьими информационными выходами, адресными выходами и стробирующйми выходом соответственно с информационными входами, адресньми входами и стробирующим входом блока дешифраторов , вторые выходы блока анализа соединены с шестым информационным входом блока сопряжения, а в каждом узле согласования второй его вход соединен с первым входом первого элемента И и первым входом регистратора неисправности, третьи входы - с управляющими входами блока памяти теста, четвертые входы - с первыми входами блока уставок, пятые входы - с. вторыми входами блока уставок и

г

J

ю 15 20 25 зо . .

5

0

5

адресными входами блока памяти теста, шестой и седьмой входы соответствен- но - с вторым и третьим входами регистратора неисправности, восьмой вход - с первым нулевым установочным входом счетного триггера, девятый вход - с третьим входом блока уставок, первым входом первого элемента ИЛИ и информационным входом блока памяти теста, десятый вход - с четвертым входом блока уставок и вторым нулевым установочным входом счетного триггера, одиннадцатые входы - с пятыми входами блока уставок, двенадцатый вход - с четвертым входом регистратора неисправности, тринадцатый вход - с вторым входом аналогового ключа, а четырнадцатый вход каждого узла согласования соединен с третьим входом компаратора, которйй соединен нулевым и единичным выходами с пятым и шестым входом регистратора неисправности, выход блока памяти теста соединен с вторым входом первого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, соединенного выходом со счетным входом счетного триггера, соединенного выходом с третьим входом аналогового ключа и седьмым входом регистратора неисправности, выход регистратора неисправности и единичный выход компаратора являются соответственно четвертым и третьим выходами узла согласования, . восьмой и девятый входы регистратора неисправности соединены соответственно с третьим и четвертым выходами блока уставок, пятый выход которого соединен с инверсным входом первого элемента И, а шестой выход соединен с четвертым входом коммутатора и десятым входом регистратора неисправности, а в блоке анализа его строби- рующий вход соединен со стробирукицим входом сигнатурного анализатора, выходы которого являются вторьо4И выходами блока анализа, управляющий вход которого соединен с третьим входом

элемента сравнения, I

2. Устройство по п. I, отличающееся тем, что контроллер адреса содержит первый регистр хранения, нулевые входы которого являются третьим входом, контроллера адреса и соединены с нулевыми установочными входами первого, второго и третьего двоичных счетчиков и первыми иулевыми установочньми входами второго дво ИЧНО1ГО счетчика и первого, второго, третьего, четвертого, пятого и шестого триггеров, второй нулевой установочный вход первого триггера явля- ется первым входом контроллера адреса, единичные установочные входы первого, второго, третьего, четвертого, пятого и шестого триггеров, вторые нулевые установочные входы третьего, четвертого, пятого и шестого триггеров, второй нулевой установочный вхо второго триггера, первый вход второго элемента ИЛИ, первый суммирующий счетный вход четвертого двоичного счетчика, второй нулевой установочный вход четвертого двоичного счетчика, единичные установочные входы регистра хранения, установочные вхо- цы первого двоичного счетчика, еди- ничные установочные входы четвертого двоичного счетчика являются соответствующими вторыми входами контроллера адреса, выходы пятого и шестого триггеров соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выходы второго, третьего и четвертого триггеров являются соответствующими четвертыми выходами контроллера адреса, инверсный выход третьего элемента ИЛИ и выход шестого триггера я яются соответствующими третьими выходами контроллера адреса, выходы четвертого двоичного счетчика являются пятыми выходами контроллера адреса, выход первого триггера соединен с запускающим входом первого генератора импульсов, соединенного выходом со счетным входом второго дво ичного счетчика, выходы которого сое динеиы с первыми входами соответствующих вторых элементов И, вторые вход которых соединены с соответствующими выходами регистра хранения, а выходы - с входами четвертого элемен- та ИЛИ, соединенного выходом с первыми входами третьего, четвертого и пятого элементов И и счетным входо третьего,двоичного счетчика, выход первого разряда которого соединен с вторыми входами третьего и четвертог элементов И и первым инверсным входом пятого элемента И, а выход второго разряда - с третьим входом четвертого элемента И, инверсным входом третьего и вторым инверсным входом пятого элементов И, выходы третьего и пятого элементов.И являются соот

5 Q 0 0 5

0

5

ветственно первым и вторым выходами контроллера адреса, выход четвертого элемента И соединен с вторым входом второго элемента ИЛИ, выход которого является шестым выходом контроллера адреса и соединен с запускающим входом генератора одиночных импульсов, выход которого является седьмым выходом контроллера адреса и соединен с вторым суммирующим входом четвертого двоичного счетчика и вычитающим счетным входом первого двоичного счетчика, выход переноса которого являетс я восьмым выходом контроллера адреса и соединен с третьим нулевым установочным входом первого триггера.

3.Устройство по п. , отличающееся тем, что блок идентификации неисправностей содержит пятые элементы ИЛИ, первые входы которых являются первым входом блока, первые нулевые установочные входы седьмого триггера и пятого двоичного счетчика являются вторым входом блока, единичный установочный вход седьмого триггера является третьим входом блока, входы шестого элемента ИЛИ являются четвертыми входами блока, второй нулевой установочный вход седьмого триггера соединен с выходом шестого элемента ИЛИ и является первым выходом блока, выход седьмого триггера соединен с запускающим входом второго генератора импульсов, выход которого соединен со счетным входом пятого двоичного счетчика, выходы которого являются четвертьми выходами блока и соединены с соответствующими входами первого двоичного позиционного дешифратора, выходы которого соединены с соответствующими вторыми входами пятых элементов ИЛИ, выходы которых являются третьими выходами блока, дополнительный выход первого

двоичного позиционного дешифратора соединен с вторым нулевым установочным входом пятого счетчика и третьим . нулевым установочным входом седьмого триггера и является вторым выходом блока.

4.Устройство по п. 1, отличающееся тем, что регистратор неисправности содержит восьмой триггер, первый единичный установочный вход которого является первым входом регистратора, первые входы шестого, седьмого и восьмого элементов И являются вторым входом регист35

ратрра, первый вход девятого элемента И является тоетьим входом регистратора, второй единичный установочный вход седьмого триггера является четвертым входом регистратора, второй вход восьмого элемента И является пятым входом регистратора, второй вход шестого элемента И и первый инверсный вход седьмого элемента. И являются шестым входом регистратора, третий вход шестого элемента И, второй инверсный вход седьмого и первый инверсный вход восьмого элементов И являются седьмым входом регистратора, четвертый вход шестого и второй вход седьмого элементов И и третий инверсный вход восьмого элемента И являются восьмым входом регистратора, первый и второй инверсные входы девятого элемента И являются соответственно девятым и десятым входами регистратора, выходы шестого, седьмого и восьмого элементов И соединены соответственно с первым, вторим и третьим нулевыми установочными входами восьмого триггера, выход которого соединен с вторым входом девятого элемента И, выход которого является выходом регистра- топа.

1

5. Устройство по п. 1, отли- Ч ающе е с я тем, что блок уставок содержит десятый, одиннадцатый и двенадцатый элементы И, первые входы которых являются первыми входами блока уставок, единичные установочные D-входы второго регистра хранения являются соответствующими вторыми входами блока уставок, вторые входы одиннадцатого и двенадцатого элементов И являются третьим входом блока уставок, первые нулевые установочные входы девятого, десятого, одиннадцатого и двенадцатого триггеров являются четвертым входом блока уставок, . первый стробирующий вход второго регистра хранения является соответствующим пятым входом блока уставок, .каждый из первых входов тринадцатого, четырнадцатого и пятнадцатого элементов И, вторых нулевых установочных входов девятого, десятого, одиннадцатого и двенадцатого триггеров в отдельности являются соответствующими пятыми входами блока уставок, выход девятого триггера соединен с вторым входом десятого, тринадцатого, четырнадцатого и пят,

26097436

Падцатого элементов II, выходы второго регис1тра хранения являются вторы- . ми выходами блока уставок, выходы девятого, десятого, одиннадцатого, 5 двенадцатого триггеров и десятого элемента И являются соответственно третьим, шестым, первым, четвертым, пятым выходами блока уставок.

6. Устройство по п. 1, о т л и - 10 чающееся тем, что блок дешифраторов содержит второй двоичный позиционный дешифратор, входы которого являются адресными входами блока, третий, четвертый, пятый, шестой, 15 седьмой, восьмой и девятый двоичные позиционные дешифраторы, входы кото- рых являются информационными входами блока, стробирующий вход второго двоичного позиционного депшфратора 20 является стробирующим выходом блока, первый, второй, третий, четвертый, пятый, шестой, седьмой выходы которого соединены со стробирующими входами третьего, четвертого, пятого, 25 шестого, седьмого, восьмого и девятого двоичных позиционных дешифраторов, выходы третьего, четвертого, . пятого, седьмого и восьмого двоичных позиционных дешифраторов являются 3Q соответственно первыми, вторыми,.

одиннадцатыми, третьими, пятыми . выходами блока, первый, второй, тре5

0

5

0

5

тий, четвертый, пятый, шестой выходы шестого двоичного позиционного дешифратора являются соответствующими двенадцатыми выходами блока, седьмой и восьмой выходы - десятыми выходами блока, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой выходы девятого позиционного дешифратора являются седьмыми выходами блока дешифраторов, девятый, одиннадцатый, двенадцатый выходы девятого позиционного дешифратора являются восьмым, девятым, четвертым и шестым выходами блока.

7. Устройство по п. 1, о тли - чающееся тем, что блок памяти теста содержит матричный регистр хранения, адресные входы которого являются соответствующими входами блока памяти текста, первый вход седь- мого элемента ИЛИ является информационным входом блока памяти теста, вход Запись-чтение матричного рв гистра хранения соединен с вторым входом седьмого элемента ИЛИ и явля- ется соответствующим управляющим вхо-: дом блока памяти теста, информаци37

онный вход матричного регистра хранения и инверсный вход седьмого элемента ИЛИ являются соответствующим управляющим входом блока памяти тес- ta, инверсный выход седьмого элемента ИЛИ соединен с входом выбора матричного регистра хранения, выход которого является выходом блока памяти теста,

8. Устройство по п. I, отличающееся тем, что сигнатурный анализатор содержит 16-разрядный сдвиговый регистр, стробирующий вход и нулевой установочный входы которого являются соответственно стробирую адим и управляющим входами сигнатурного анализатора, первый вход элемента сложения по модулю два является информационным входом сигнатурно26097438

го анализатора, а выход соединен с информационным входом 16-разрядного сдвигового регистра, все выходы которого являются выходами сигнатурно- 5 го анализатора, а седьмой, девятый, двенадцатый, шестнадцатый выходы соединены соответственно с вторым, третьим, четвертым и пятым входами -элемента сложения по модулю два, 10 9. Устройство по п. I, отличающееся тем, что блок регистров содержит третий и четвертый регистры хранения, информационные входы которых соединены между собой 15 и являются информационными входами блока, управляющие входы являются соответствующими управляющими входами 1блока, а выходы соответственно первыми и вторыми выходами блока |регистров.

HaSff.y

fW/77.

OmSn.ti

dm 6л. JO I ctnpoS

ycm.mff.Htucnp.

0mm S3 Вш.сч.тр.

ОтмМ .

14

Отзл.35

, J компор.

А 75

Отза.З ° « ffР

МОСнир.

Omsn.tfH nodKa.ixoSot

Отбл.11 МЖФи.5

Cffou NK

НО 6П. It

73

Л 77

41. If

H9S.n

ноелп

унадл.2

Фи9.9

Составитель И. Швец Редактор Л. Пчелинская Техред М.Ходанич

Заказ 5234/51Тираж 671Подписное

ВНИИПИ 1 осударственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская каб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор О. Луговая

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |