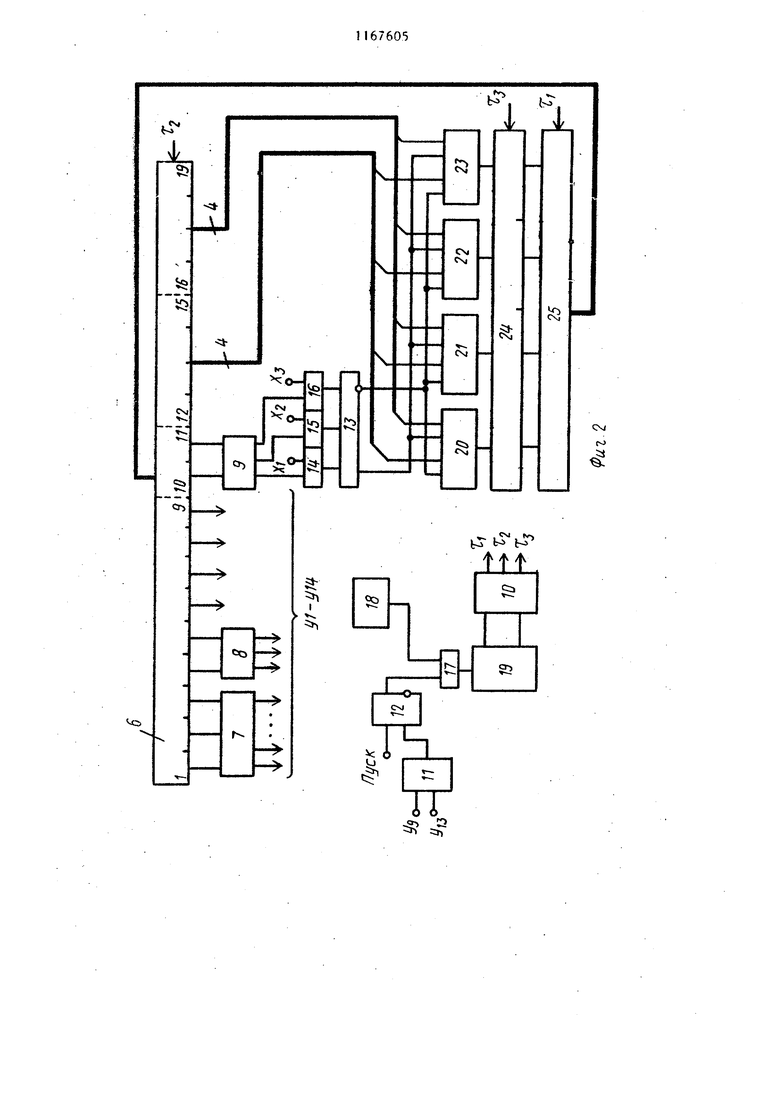

ного выхода памяти микропрограмм подключены к соответствующим разрядам информационного входа регистра микрокоманды, четвертый рьжод первого дешифратора подключен к первому входу элемента ИЛИ, седьмой выход первого дешифратора подключен к второму входу элемента ИЛИ, выход элемента ИЛИ подключен к входу сброса триггера пуска, выход триггера пуска подключен к первому входу четвертого элемента И, к второму входу четвертого элемента И подключен выход генератора импульсов, выход четвертого элемента И подключен к входу счетчика управления, информационные выходы счетчика управления подключены к входам четвертого дешифратора, первьй выход четвертого дешифратора подключен к управляющему входу синхронизации памяти NMKponporpaMM, второй выход четвертого дешифратора подключен к управляющему входу записи регистра микрокоманды, третий выход четвертого дешифратора подключен к управляющему входу записи регистра адреса микрокоманды, причем первый выход первого дешифратора подключен к входу управления занесением информации регистра числа, первьй выход второго дешифратора подключен к входу сброса двоичного реверсивного счетчика, второй выход первого дешифратора подключен к входу управления вьщачей информацги

регистра числа, второй выход второго дешифратора подключен к входу управления вьщачей информации двоичного реверсивного счетчика, выход шестого разряда регистра микрокоманды подключен к управлякяпему входу вьщачи информагщи сумматора-вьгчитателя, выход седьмого разряда регистра микрокоманды подключен к мпадшему разряду второй группы входов сумматора-вычитателя, выход восьмого разряда регистра микрокоманды подключен к управляющему входу задания режима вычитания сумматора-вычитателя, третий выход первого дешифратора подключен к входу инкремента двоичного реверсивного счетчика пятьй выход первого дешифратора подключен к управляющему входу сброса регистра числа, третий выход второго дешифратора подключен к входу управления занесением информагщи в двоичный реверсивный счетчик, шестой выход первого дешифратора подключен к входу декремента двоичного реверсивного счетчика, выход девятого разряда регистра микрокоманды подключен к управляющему входу задания режима суммирования сумматора-вьгчитателя, выход триггера знака подключен к второму входу второго элемента И , выход переполнения двоичного реверсивного счетчика подключен к второму входу третьего элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1988 |

|

SU1541557A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА С АВТОМАТИЧЕСКИМ ПРОГРАММИРОВАНИЕМ И МИКРОПРОГРАММНЫМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1964 |

|

SU224161A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1975 |

|

SU532295A1 |

| УСТРОЙСТВО ОБУЧЕНИЯ ОПЕРАТОРОВ | 1997 |

|

RU2129734C1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее регистр числа, триггер знака, блок управления и сумматорвычитатель, причем информационный выход сумматора-вьгчитателя подключен к информационному входу регистра числа, выход регистра числа подключен к первой группе входов сумматоравычитателя, выход старшего разряда регистра числа подключен к входу установки триггера знака, отличающееся тем, что, с целью сокращения количества оборудования и расширения функциональных возможностей за счет обеспечения возм жности возведения в квадрат, в него введен двоичный реверсивньй счетчик, причем выходы двоичного реверсивного счетчика подключены к второй группе входов сумматора-вычитателя, начиная с предпоследнего разряда, причем блок управления содержит регистр микрокоманды, четыре дешифратора, четыре элемента И, элемент ИЛИ-НЕ, четыре элемента 2-2И-ИЛИ, регистр адреса микрокоманды, память микропрограммы, элемент ИЛИ, триггер пуска, генератор импульсов, счетчик управления, причем выходы первых трех разрядов регистра микрокоманды подключены ко входу первого дешифратора, выходы четвертого и пятого разрядов регистра микрокоманды подключены к входам второго дешифратора, выходы десятого и одиннадцатого разрядов регистра микрокоманды подключены к входам третьего дешифратора, выходы разрядов регистра микрокоманды с двенадцатого по пятнадцатый подключены к первым входам соответственно первого, второго, третьего и четвертого элементов 2-2И-ИЛИ, выходы разрядов регистра микрокоманды с шестнадцатого -по девятнадцатый подключены к вторым входам соответственно (Л первого второго, третьего и четвертого элементдё 2-2И-ИЛИ, первьй, второй и третий выходы третьего дешифратора подключены к первым входам первого, второго и третьего элементов И соответственно, выходы первого , второго и третьего элементов И подключены соответственно к первому, сг .второму и третьему входам элемента ИЛИ-НЕ, прямой выход Элемента ИЛИ-HF. 9) СД подключен к третьим входам первого, второго, третьего и четвертого элементов 2-2И-ИЛИ, а инверсный выход элемента ИЛИ-НЕ подключен к четвертым входам первого, втЬрого, третьего и четвертого элементов 2-2И-ИЛИ, выходы элементов 2-2И-Ш1И подключены к входам соответствующих разрядов регистра адреса микрокоманды, выходы разрядов регистра адреса микрокоманды подключены к соответствующим разрядам адресного входа памяти микропрограмм, разряды информацион- .

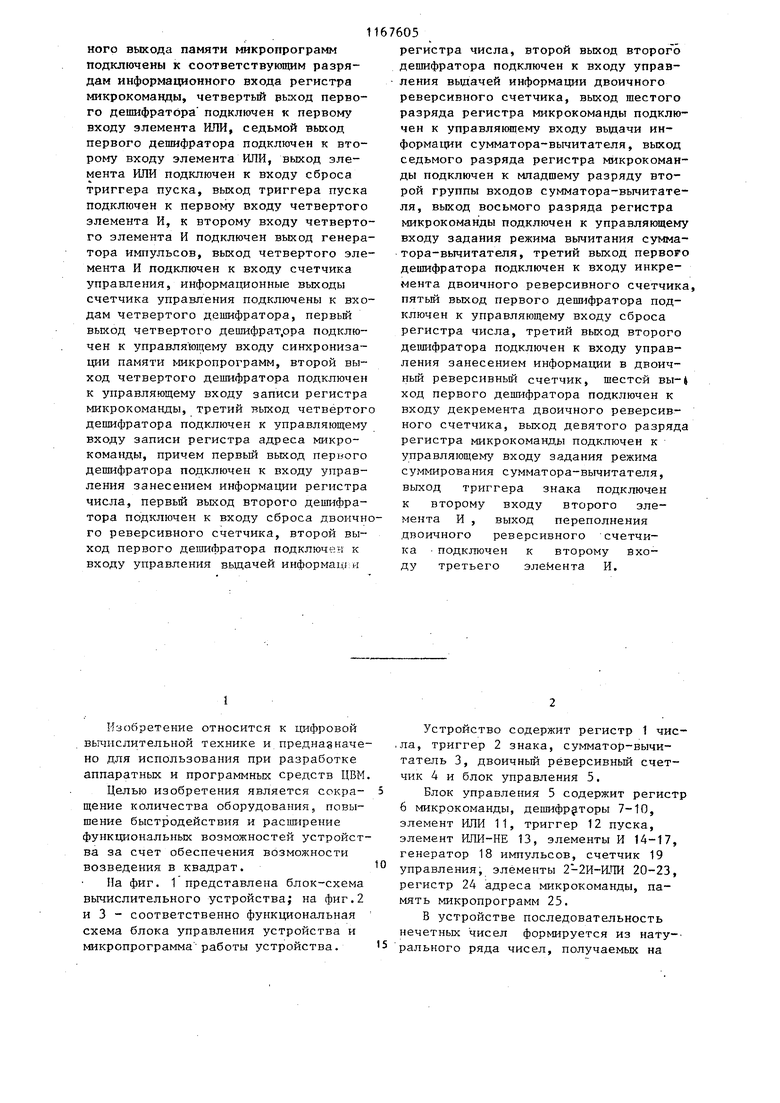

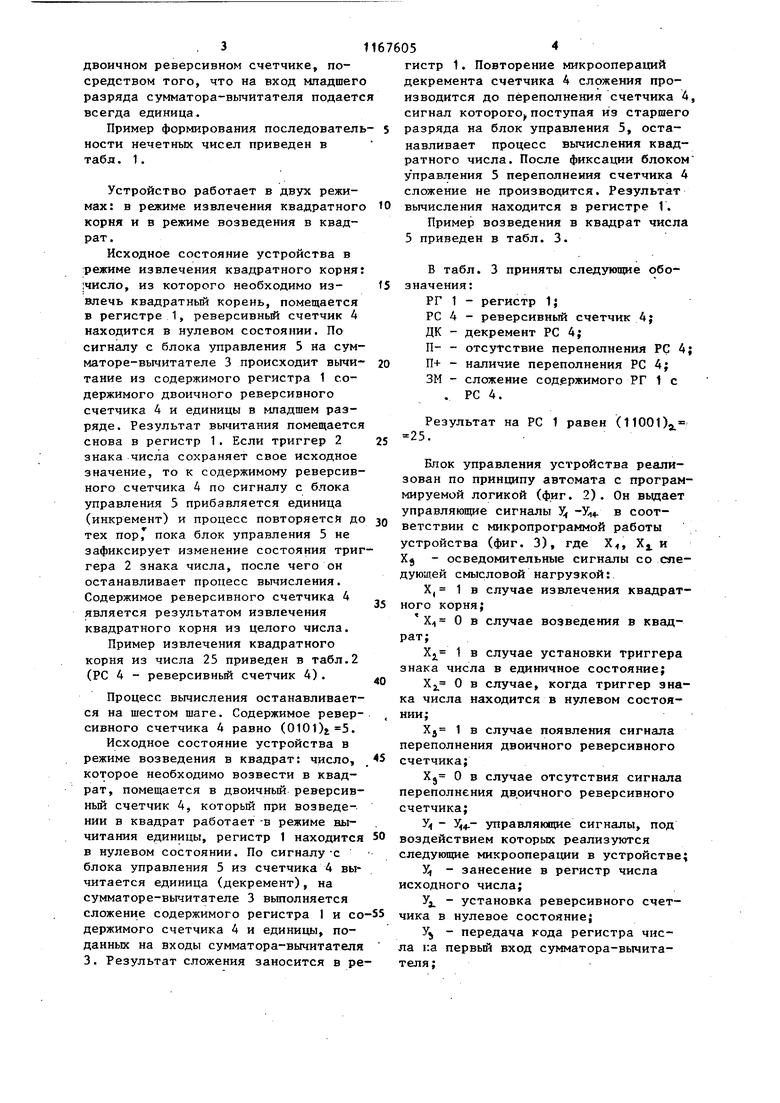

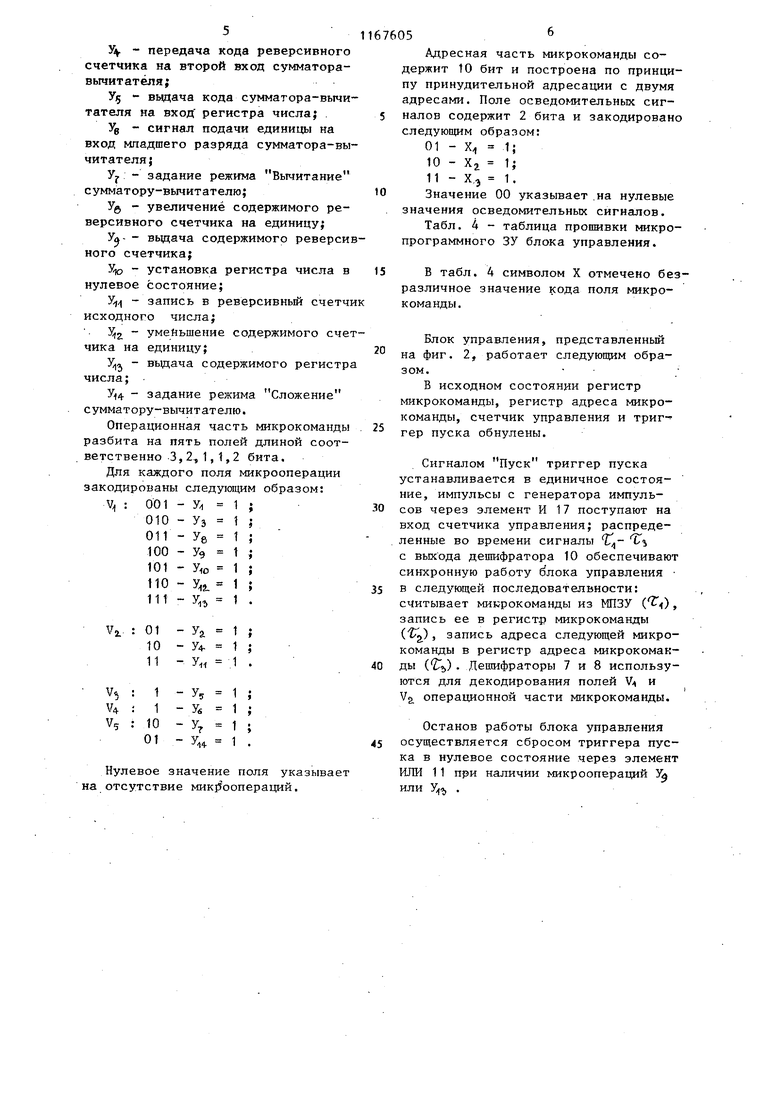

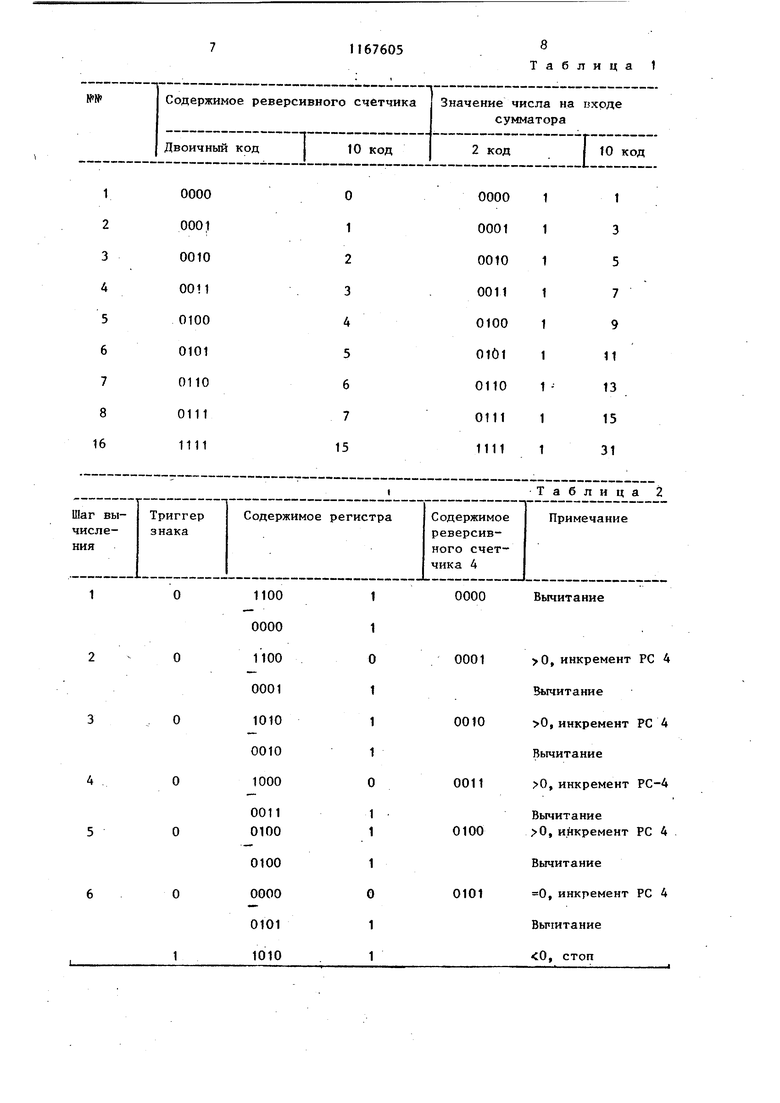

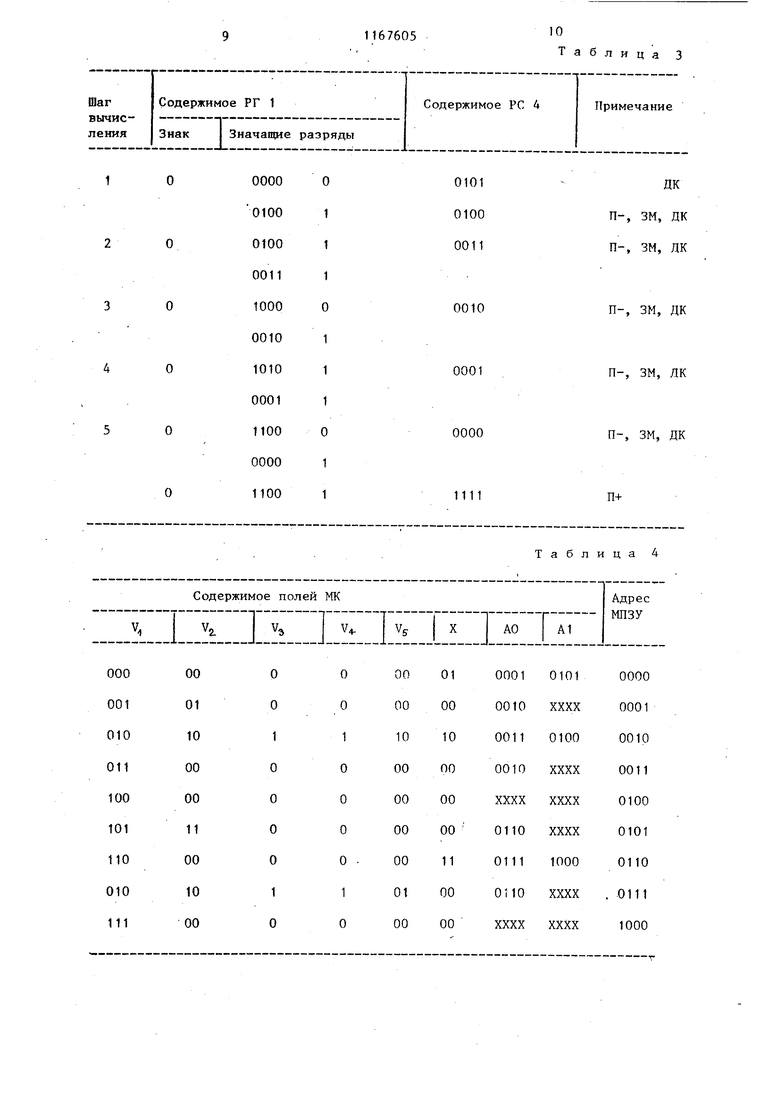

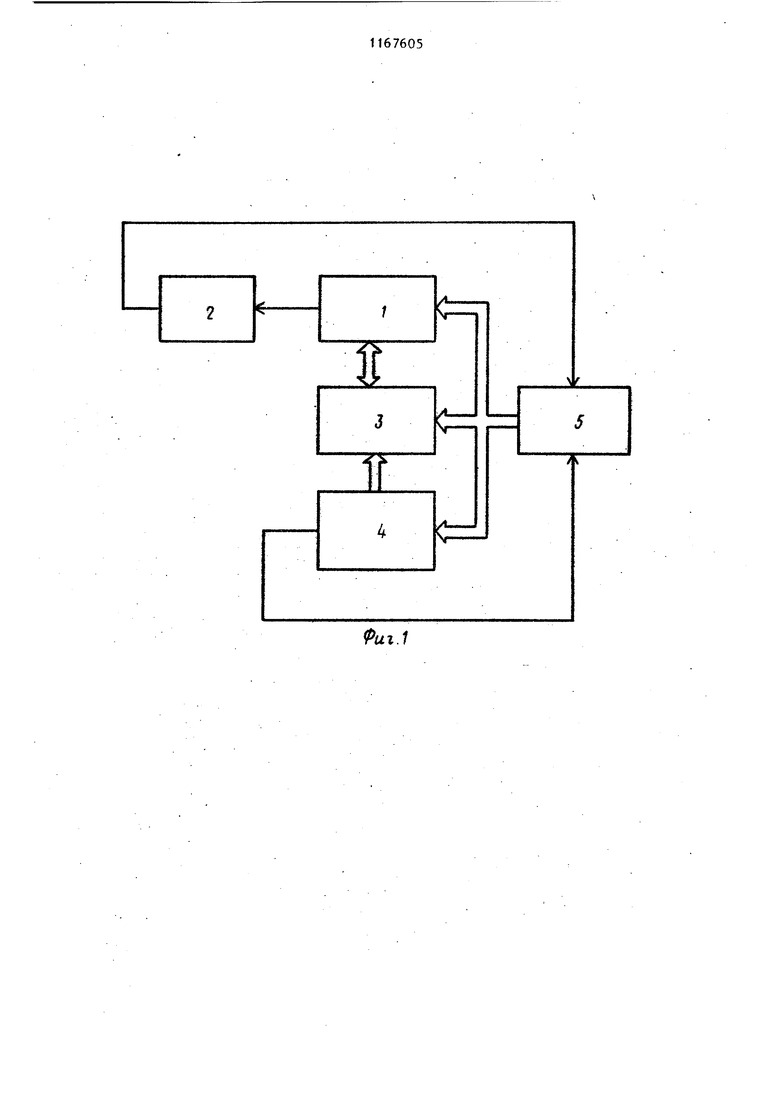

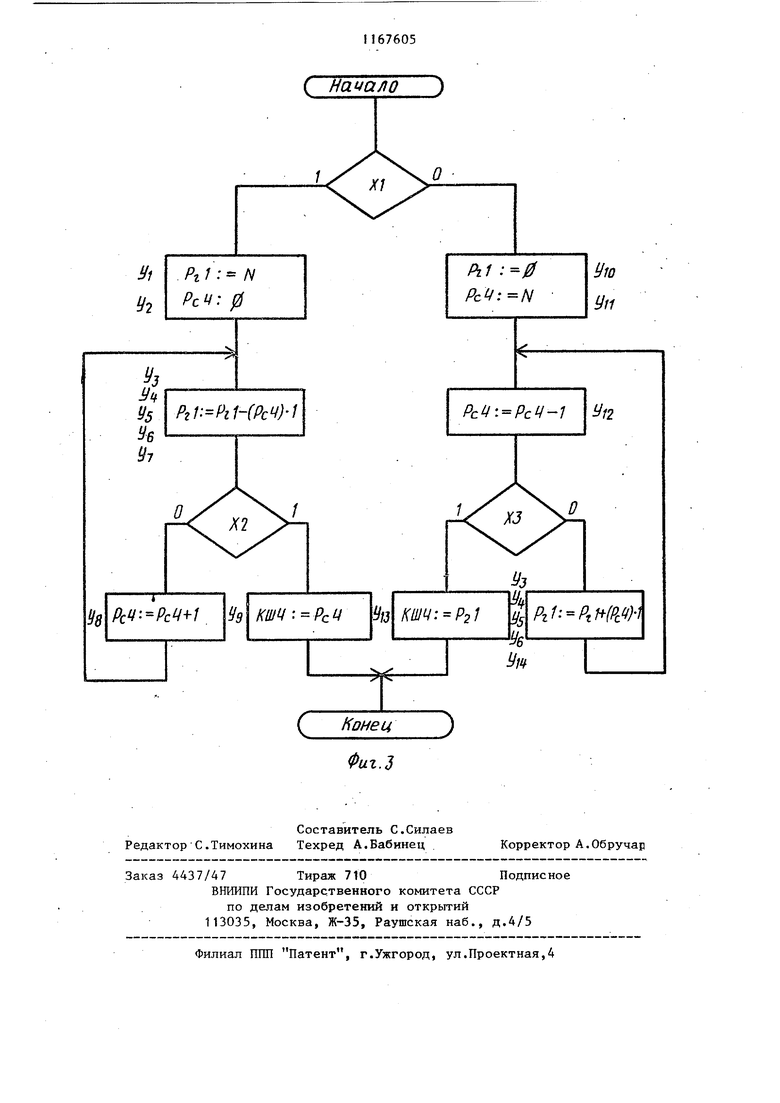

Изобретение относится к цифровой вычислительной технике и предназначе но для использования при разработке аппаратных и программных средств ЦВМ Целью изобретения является сокращение количества оборудования, повышение быстродействия и расширение функциональных возможностей устройст ва за счет обеспечения возможности возведения в квадрат, Иа фиг. 1 представлена блок-схема вычислительного устройства; на фиг.2 и 3 - соответственно функциональная схема блока управления устройства и микропрограмма работы устройства. Устройство содержит регистр 1 числа, триггер 2 знака, сумматор-вычитатель 3, двоичньй реверсивный счетчик 4 и блок управления 5. Блок управления 5 содержит регистр 6 микрокоманды, дешифр торы 7-10, элемент ИЛИ 11, триггер 12 пуска, элемент Ш1И-НЕ 13, элементы И 14-17, генератор 18 импульсов, счетчик 19 управления, элементы 2-2И-ИЛИ 20-23, регистр 24 адреса микрокоманды, память микропрограмм 25. В устройстве последовательность нечетных чисел формируется из натурального ряда чисел, получаемых на двоичном реверсивном счетчике, посредством того, что на вход младшег разряда сумматора-вычитателя подаетс всегда единица. Пример формирования последовател ности нечетных чисел приведен в табл. 1. Устройство работает в двух режимах: в режиме извлечения квадратног корня и в режиме возведения в квадрат. Исходное состояние устройства в режиме извлечения квадратного корня ;число, из которого необходимо извлечь квадратный корень, помещается в регистре 1, реверсивньй счетчик 4 находится в нулевом состоянии. По сигналу с блока управления 5 на сумматоре-вычитателе 3 происходит вычитание из содержимого регистра 1 содержимого двоичного реверсивного счетчика 4 и единицы в младшем разряде. Результат вычитания помещается снова в регистр 1. Если триггер 2 знака числа сохраняет свое исходное значение, то к содержимому реверсивного счетчика 4 по сигналу с блока управления 5 прибавляется единица (инкремент) и процесс повторяется до тех пор пока блок управления 5 не зафиксирует изменение состояния три гера 2 знака числа, после чего он останавливает процесс вычисления. Содержимое реверсивного счетчика 4 является результатом извлечения квадратного корня из целого числа. Пример извлечения квадратного корня из числа 25 приведен в табл.2 (PC 4 - реверсивный счетчик 4). Процесс вычисления останавливается на шестом шаге. Содержимое реверсивного счетчика 4 равно (0101)5. Исходное состояние устройства в режиме возведения в квадрат: число, которое необходимо возвести в квадрат, помещается в двоичный реверсивньй счетчик 4, который при возведении в квадрат работает -в режиме вычитания единицы, регистр 1 находится в нулевом состоянии. По сигналу-с блока управления 5 из счетчика 4 вычитается единица (декремент), на сумматоре-вьтитателе 3 выполняется сложение содержимого регистра 1 и со держимого счетчика 4 и единицы, поданных на входы сумматора-вычитателя 3. Результат сложения заносится в ре 054 гистр 1, Повторение микроопераций декремента счетчика 4 сложения производится до переполнения счетчика 4, сигнал которого поступая из старшего разряда на блок управления 5, останавливает процесс вычисления квадратного числа. После фиксации блоком управления 5 переполнения счетчика 4 сложение не производится. Результат вычисления находится в регистре Г. Пример возведения в квадрат числа 5 приведен в табл. 3. В табл. 3 приняты следующие обозначения:РГ 1 - регистр 1; PC 4 - реверсивный счетчик 4; ДК - декремент PC 4; П- - отсутствие переполнения PC 4; П+ - наличие переполнения PC 4; ЗМ - сложение содержимого РГ 1 с . PC 4. Результат на PC 1 равен (11001), Блок управления устройства реализован по принципу автомата с программируемой логикой (фиг. 2). Он вьодает управляющие сигналы У, -У,4. в соответствии с микропрограммой работы устройства (фиг. 3), где Х, Х и Xj - осведомительные сигналы со сяедующей смысловой нагрузкой: X, 1 в случае извлечения квадратного корня; Х О в случае возведения в квадрат;Х.| 1 в случае установки триггера знака числа в единичное состояние; Xj О в случае, когда триггер знака числа находится в нулевом состоянии;Хд 1 в случае появления сигнала переполнения двоичного реверсивного счетчика; Х5 О в случае отсутствия сигнала переполнения двоичного реверсивного счетчика; У - 4- управляющие сигналы, под воздействием которых реализуются следующие микрооперации в устройстве; У - занесение в регистр числа исходного числа; У - установка реверсивного счетчика в нулевое состояние; У - передача кода регистра чиса ка первьй вход сумматора-вычитателя;5 J - передача кода реверсивного счетчика на второй вход сумматоравычитателя;У5 - ввдача кода сумматора-вычи тателя на вход регистра числа; Yg - сигнал подачи единицы на вход младшего разряда сумматора-вы читателя; Yj - задание режима Вычитание сумматору-вычитателго; Уд - увеличение содержимого реверсивного счетчика на единицу; Ул- - вьздача содержимого реверси ного счетчика; XK - установка регистра числа в нулевое состояние; У, - запись в реверсивный счетч исходного числа; . уменьшение содержимого сче чика на единицу; У - вьщача содержимого регистр числа; yt4 - задание режима Сложение сумматору-вычитателю. Операционная часть микрокоманды разбита на пять полей длиной соответственно 3, 2, 1 , 1,2 бита. Для каждого поля микрооперации закодированы следующим образом: Нулевое значение поля указывае на отсутствие мик1Уоопераций. 5 Адресная часть микрокоманды содержит 10 бит и построена по принципу принудительной адресации с двумя адресами. Поле осведомительных сигналов содержит 2 бита и закодировано следующим образом: 01 - Х 1; 10- Xj 1; 11- X,.j 1. Значение 00 указывает .на нулевые значения осведомительных сигналов. Табл. 4 - таблица пропивки микропрограммного ЗУ блока управления. В табл. 4 символом X отмечено безразличное значение кода поля микрокоманды. Блок управления, представленньй на фиг. 2, работает следующим образом. Б исходном состоянии регистр микрокоманды, регистр адреса микрокоманды, счетчик управления и триг-гер пуска обнулены. Сигналом Пуск триггер пуска устанавливается в единичное состояние, импульсы с генератора импульсов через элемент И 17 поступают на вход счетчика управления; распределенные во времени сигналы - ТГ с вькода дешифратора 10 обеспечивают синхронную работу блока управления в следующей последовательности: считывает микрокоманды из МПЗУ (2), запись ее в регистр микрокоманды (Z) , запись адреса следующей микрокоманды в регистр адреса микрокомакды CZ,) . Деашфраторы 7 и 8 используются для декодирования полей V и Vg операционной части микрокоманды. Останов работы блока управле шя осуществляется сбросом триггера пуска в нулевое состояние через элемент ИЛИ 11 при наличии микроопераций У или У(, .

Таблица 1

Таблица 3

иг.1

( Начало )

| Устройство для извлечения квадратного корня | 1974 |

|

SU538361A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3551662, fcл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-15—Публикация

1983-12-23—Подача