1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при реализации технических средств дискретной автоматики и ЦВМ.

Известны устройства для возведения двоичных чисел в третью степень, содержащие двоичный счетчик, элементы задержки, два сумматора, группы элементов «И. Входная шина соединена через два элемента задержки с одним из входов первой группы элементов «И, другие входы которых подключены к выходам первого сумматора, а выход - к одним из 113 входов вторго сумматора. Выход второго элемента задержкн подключен к одним входам второй группы элементов «И, другие входы которых соединены с выходами двоичного счетчика, а выходы - с одним из вхохлов первого сумматора.

Известные устройства содержат большое количество оборудования.

С целью упрощения устройства, в нел входная щина соединена со входом второго сумматора и с одним из входов третьей группы элементов «И, другие входы которых соединены с выходами двоичного счетчика, а выход - с другими входами первого сумматора, выход первого элемента задержки подключен также ко входу двоичного счетчика.

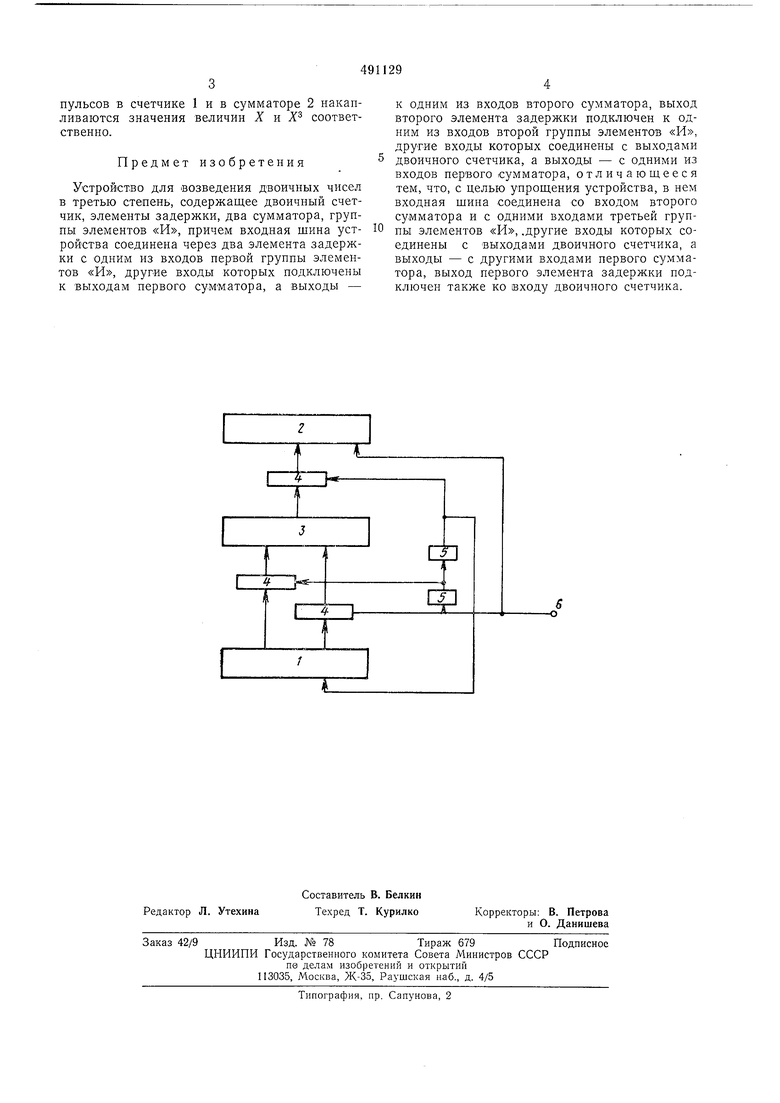

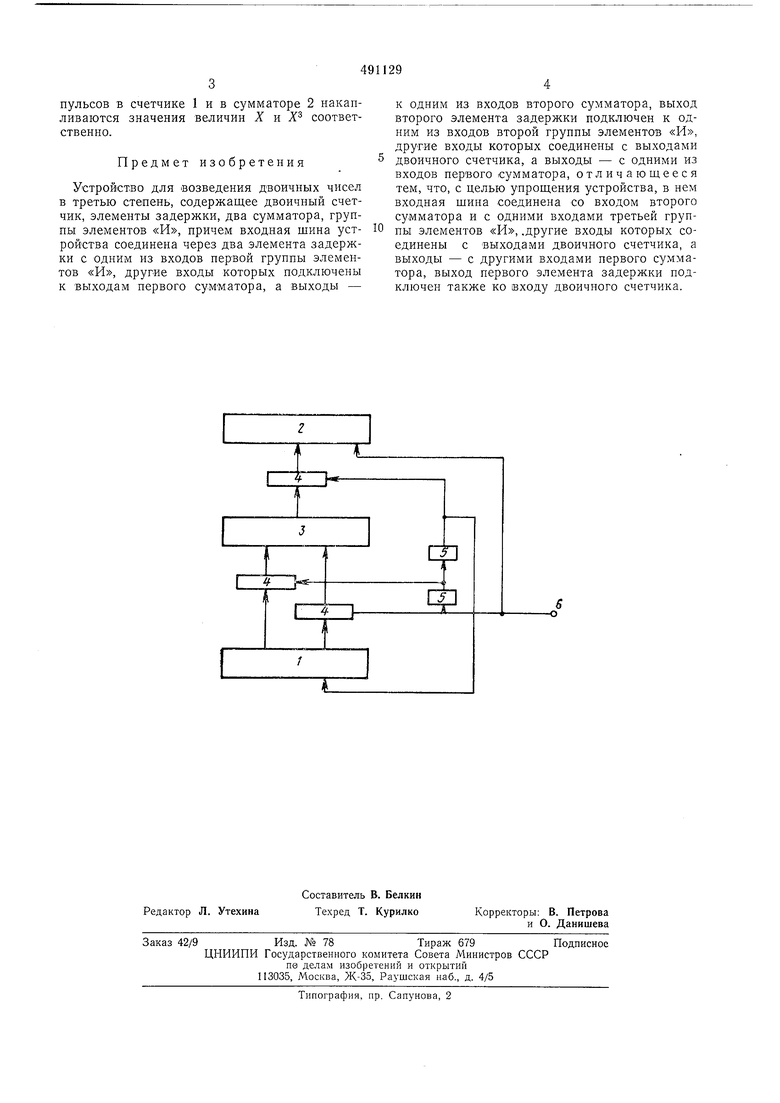

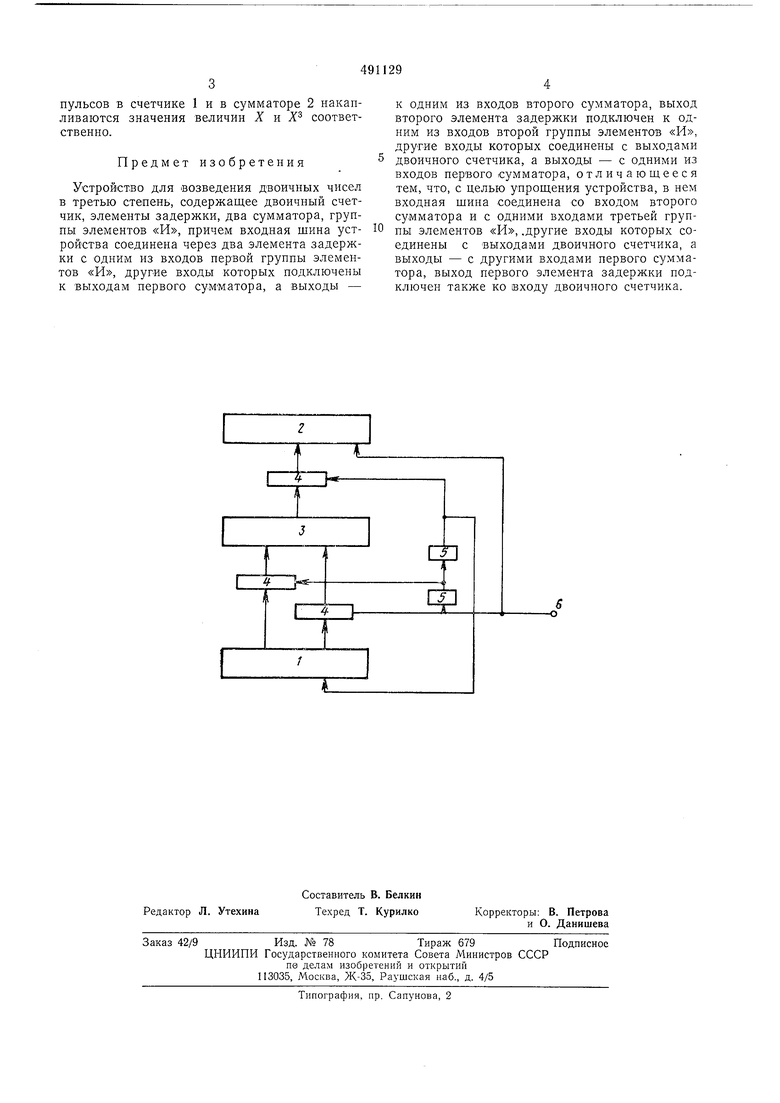

Блок-схема предложенного устройства представлена на чертеже.

Устройство содержит двоичный счетчик 1, сумматоры 2 и 3, группы схем «И 4 и элементы задержки 5.

Устроргство работает следующим образом.

Начальное состояние двоичного счетчика 1 и сумматоров 2 н 3 - нулевое. Двоичное число (X), представленное последовательностью импульсов, поступает на входную шину устройства 6. С приходом первого импульса к содержимому второго сумматора прибавляется единица, а содержимое счетчика 1 передается через группу элементов «И 4 и прибавляется к содержимому первого сумматора 3. Входной импульс проходит через второй элемент задержки 5 и открывает вторую группу элементов «И 4, через которые содержимое счетчика 1 передается на вход сумматора 3 со сдвигом на один разряд влево. Таким образом, к предыдущему значению в сумматоре 3 прибавляется утроенное содержимое счетчика 1. Затем входной импульс проходит через первый элемент задержки 5, прибавляет единицу младшего разряда к содержимому счетчика 1 и открывает первую группу элементов «И 4, разрешая передачу кода с выхода сумматора 3 на вход сумматора 2 со сдвигом на один разряд влево.

Аналогичные вычисления проводятся для каждого импульса, поступившего на входную шину устройства. После поступления X импульсов в счетчике 1 и в сумматоре 2 накапливаются значения величин X i Х соответственно.

Предмет изобретения

Устройство для 1возведения двоичных чисел в третью степень, содержащее двоичный счетчик, элементы задержки, два сумматора, группы элементов «И, причем входная шина устройства соединена через два элемента задержки с одним из входов первой группы элементов «И, другие входы которых подключены к выходам первого сумматора, а выходы -

к одним из входов второго сумматора, выход второго элемента задержки подключен к одним из входов второй группы элементов «И, другие входы которых соединены с выходами двоичного счетчика, а выходы - с одними из входов первого сумматора, отличающееся тем, что, с целью упрощения устройства, в нем входная шина соединена со входом второго сумматора и с одними входами третьей группы элементов «И, .другие входы которых соединены с выходами двоичного счетчика, а выходы - с другими входами первого сумматора, выход первого элемента задержки подключен также ко входу двоичного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в куб | 1985 |

|

SU1257640A1 |

| Устройство для возведения двоичных чисел в третью степень | 1978 |

|

SU746505A2 |

| Арифметическое устройство | 1987 |

|

SU1476459A1 |

| Устройство для возведения в степень | 1987 |

|

SU1499338A1 |

| Устройство для вычисления @ , @ , @ аргумента,заданного параллельным и число-импульсным кодом | 1980 |

|

SU999047A1 |

| Устройство для возведения двоичных чисел в степень | 1974 |

|

SU541168A1 |

| Устройство для свертки по модулю | 1991 |

|

SU1809443A1 |

| Устройство для вычисления суммы квадратов К числоимпульсных величин | 1982 |

|

SU1092500A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

f f

Авторы

Даты

1975-11-05—Публикация

1974-02-01—Подача