1

Изобретение относится к вычислительной технике и может применяться при построении специализированных вычислительных устройств и функциональных преобразователей информации.

Известно устройство для возведения чисел в степень, содержащее регистр, пять сумматоров, двоиЧНЫЙ счетчик, группы элементов И и элементы задержки и построенное по общей схеме воспроизведения полиномов методами конечных разностей. Недостатком этого устройства является большой объем аппаратурных затрат как для вычисления непосредственно искомой функции, так и для ввода начальных условий в регистр и сумматоры.

Известно также устройство для возведения в степень чисел, поступающих последовательным кодом старшими разрядами вперед, содержащее регистр числа, регистры первого, второго и третьего блоков, три сумматора, умножители па Коэффициенты три, четыре и щесть, блоки элементов И и элементы задержки. Недостатком его являются большие аппаратурные затраты и ограниченный класс решаемых задач, так как его нельзя иснользовать для возведения в степень чисел, представленных в виде последовательности импульсов.

Наиболее близким техническим рещением к предлагаемому является устройство для возведения Двоичных чисел в степень, содержащее счетчик, первый выход которого соединен с первым входом первого блока элементов И, а второй - с первым входом второго блока элементов И, выходы первого и второго блоков элементов И соединены соответственно с первым и вторым входами первого сумматора, выход которого соединен с первым входом третьего блока элементов И, второй вход которого соединен с входом счетчика, а выход - с первым входом второго сумматора, входная шина соединена с входом первого элемента задержки, выход которого соединен с входом второго элемента задержки.

Недостатком этого устройства является ограниченный класс решаемых на нем задач, так как устройство не позволяет возводить в пятую степень число, представленное в виде последовательности импульсов.

Целью изобретения является расщирение класса решаемых задач.

Это достигается тем, что в предлагаемое устройство введены третий и четвертый элементы задержки, четвертый, пятый и шестой

блоки элементов И, третий и четвертый сумматоры, причем первые входы четвертого и пятого блоков элементов И соединены соответственно с входами первого и второго элементов задержки, а вторые входы соединены

с первым и вторым выходами второго сумматора соответственно, второй вход которого соединен с входом счетчика и первыми входами шестого блОка элементов И и четвертого сумматора, второй вход которого соединен с выходом шестого блока элементов И, второй вход которого соединен с выходом третьего сумматора, первый и второй входы которого соединены соответственно с выходами четвертого и пятого блоков элементов И, а третий и четвертый входы - с первым и вторым входами первого сумматора соответственно, выход второго элемента задержки соединен с вторым входом первого блока элементов И и входом третьего элемента задерл ки, выход которого соединен с вторым входом второго блока элементов И и входом четвертого элемента задержки, выход которого соединен с первым входом четвертого сумматора.

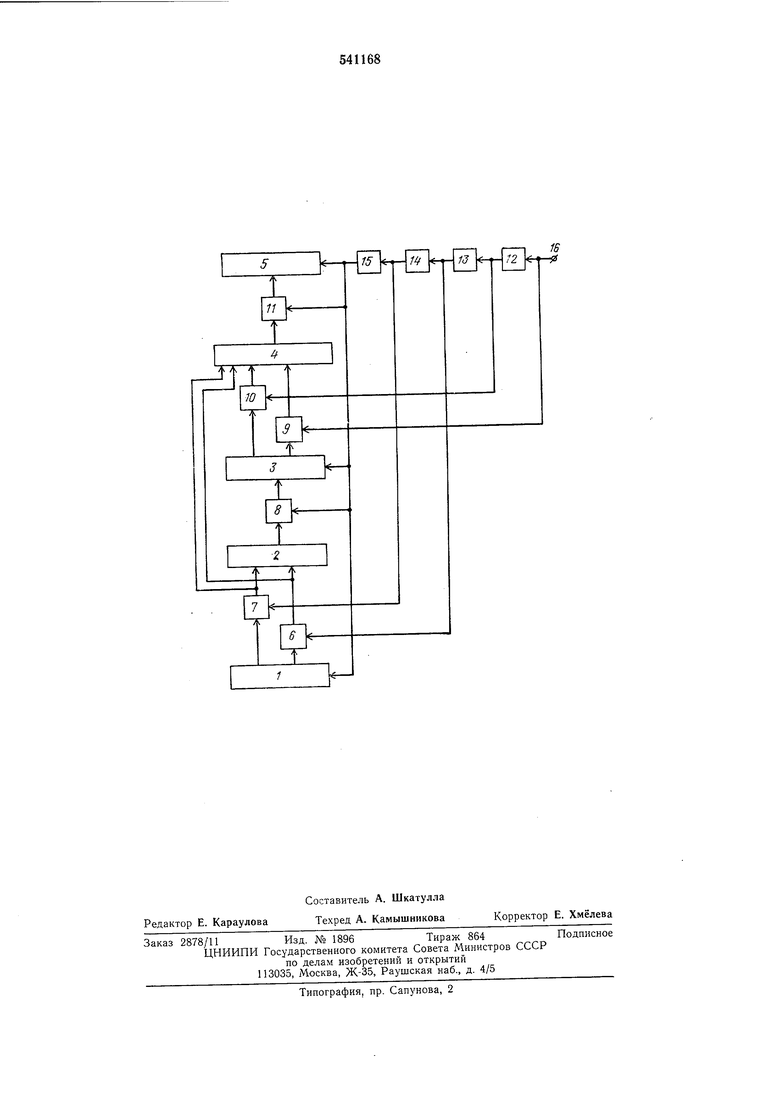

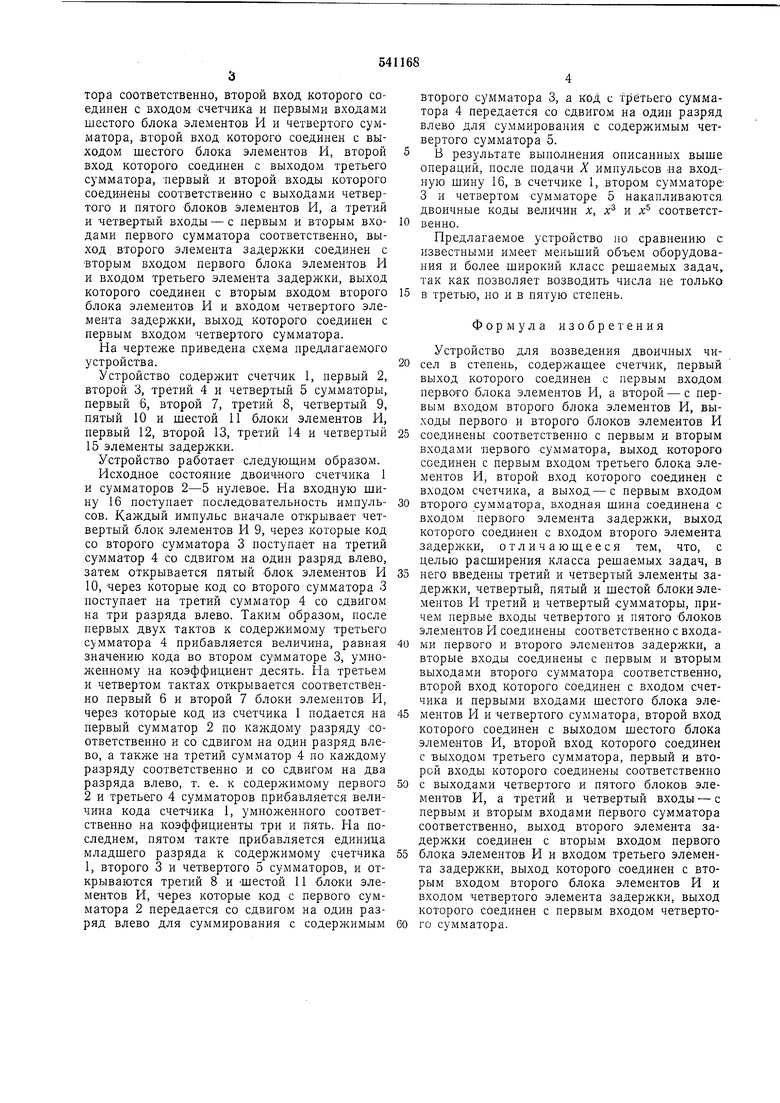

На чертеже приведена схема предлагаемого устройства.

Устройство содержит счетчик 1, первый 2, второй 3, третий 4 и четвертый 5 сумматоры, первый 6, второй 7, третий 8, четвертый 9, пятый 10 и шестой И блоки элементов И, первый 12, второй 13, третий 14 и четвертый 15 элементы задержки.

Устройство работает следуюш,им образом.

Исходное состояние двоичного счетчика 1 и сумматоров 2-5 нулевое. На входную шину 16 поступает последовательность импульсов. Каждый импульс вначале открывает четвертый блок элементов И 9, через которые код со второго сумматора 3 поступает на третий сумматор 4 со сдвигом на один разряд влево, затем открывается пятый блок элементов И 10, через которые код со второго сумматора 3 поступает на третий сумматор 4 со сдвигом на три разряда влево. Таким образом, после первых двух тактов к содержимому третьего сумматора 4 прибавляется величина, равная значению кода во втором сумматоре 3, умноженному на коэффициент десять. На третьем и четвертом тактах открывается соответственно первый 6 и второй 7 блоки элементов И, через которые код из счетчика 1 подается на первый сумматор 2 по каждому разряду соответственно и со сдвигом на один разряд влево, а также на третий сумматор 4 по каждому разряду соответственно и со сдвигом на два разряда влево, т. е. к содержимому первого 2 и третьего 4 сумматоров прибавляется величина кода счетчика 1, умноженного соответственно на коэффициенты три и пять. На последнем, пятом такте прибавляется единица младшего разряда к содержимому счетчика 1, второго 3 и четвертого 5 сумматоров, и открываются третий 8 и Шестой 11 блоки элементов И, через которые код с первого сумматора 2 передается со сдвигом на один разряд влево для суммирования с содержимым

второго сумматора 3, а КбД с третьего сумматора 4 передается со сдвигом на один разряд влево для суммирования с содержимым четвертого сумматора 5.

В результате выполнения описанных выше операций, после подачи X импульсов на входную шипу 16, в счетчике 1, втором сумматоре: 3 и четвертом сумматоре 5 накапливаются, двоичные коды величин х, к и к соответственно.

Нредлагаемое устройство по сравнению с известными имеет меньший объем оборудования и более широкий класс решаемых задач, так как позволяет возводить числа не только

в третью, но и в пятую степень.

Формула изобретения

Устройство для возведения двоичных чисел в степень, содержаш,ее счетчик, первый выход которого соединен с первым входом первого блока элементов И, а второй - с первым входом второго блОКа элементов И, выходы первого и второго блоков элементов И

соединены соответственно с первым и вторым входами первого сумматора, выход которого соединен с первым входом третьего блока элементов И, второй вход которого соединен с входом счетчика, а выход-с первым входом

второго сумматора, входная шина соединена с входом первого элемента задержки, выход которого соединен с входом второго элемента задержки, отличаюшееся тем, что, с целью расширения класса решаемых задач, в

него введены третий и четвертый элементы задержки, четвертый, пятый и шестой блоки элементов И третий и четвертый сумматоры, причем первые входы четвертого и пятого -блоков элементов И соединены соответственно с входами первох-о и второго элементов задержки, а вторые входы соединены с первым и вторым выходами второго сумматора соответственно, второй вход которого соединен с входом счетчика и первыми входами шестого блока элементов И и четвертого сумматора, второй вход которого соединен с выходом шестого блока элементов И, второй вход которого соединен с выходом третьего сумматора, первый и второй входы которого соединены соответственно

с выходами четвертого и пятого блоков элементов И, а третий и четвертый входы - с первым и вторым входами первого сумматора соответственно, выход второго элемента задержки соединен с вторым входом первого

блока элементов И и входом третьего элемента задержки, выход которого соединен с вторым входом второго блока элементов И и входом четвертого элемента задержки, выход которого соединен с первым входом четвертого сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1987 |

|

SU1499338A1 |

| Устройство для вычисления @ , @ , @ аргумента,заданного параллельным и число-импульсным кодом | 1980 |

|

SU999047A1 |

| Устройство для деления п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU807282A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Устройство для возведения в куб | 1985 |

|

SU1257640A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| Устройство для возведения двоичного числа в четвертную степень | 1976 |

|

SU595728A1 |

Авторы

Даты

1976-12-30—Публикация

1974-12-16—Подача