1

Изобретение относится к дискретным преобразователям аналоговых сигналов и может быть использовано в «ачестве преобразующего звена в аналоговых вычислительных машинах.

Известны импульсные инверторы аналоговых сигналов, содержащие компаратор один вход которого подключен к входу инвертора, а выход через линию задержки - к управляющему входу первого ключевого элемента, накопительный конденсатор, обкладки которого через соответствующие разрядные резисторы соединены с шиной нулевого потенциала, одна из обкладок накопительного конденсатора через первый ключ присоединена к источнику положительного опорного напряжения, второй ключевой элемент, вход которого подключен к источнику отрицательного опорного напряжения, аналоговый запоминающий блок, выход которого .соединен с выходом инвертора.

Известные импульсные инверторы аналогового сигнала имеют сравнительно малый диапазон преобраз-уемого сигнала.

Предложенное устройство отличается от известных тем, что в нем другой вход компаратора подключен к точке соединения накопительного конденсатора с .первым ключевым элементом. Другая обкладка накопительного конденсатора соединена с управляющим входом аналогового запоминающего блока и выходом второго ключевого элемента. Выход компаратора подключен ко входу аналогового запоминающего блока, а управляющий вход второго ключевого элемента присоединен к выходу линии задержки.

Это позволило расшир.ить диапазон входного преобразуемого сигнала.

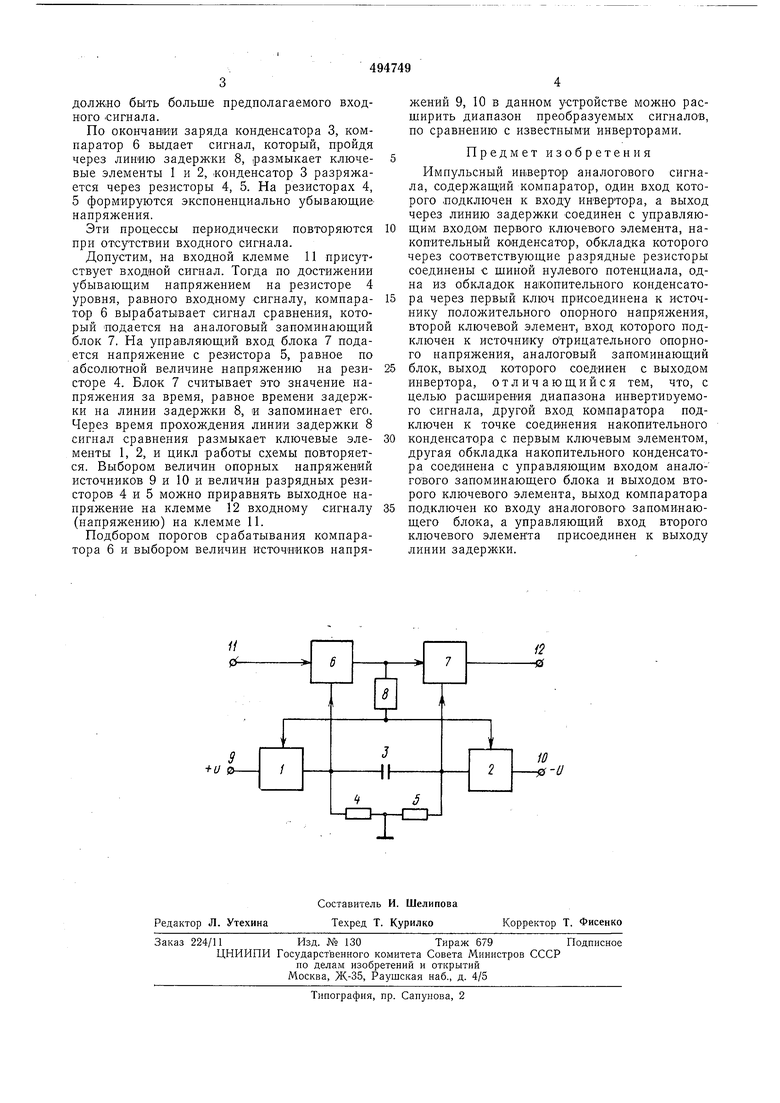

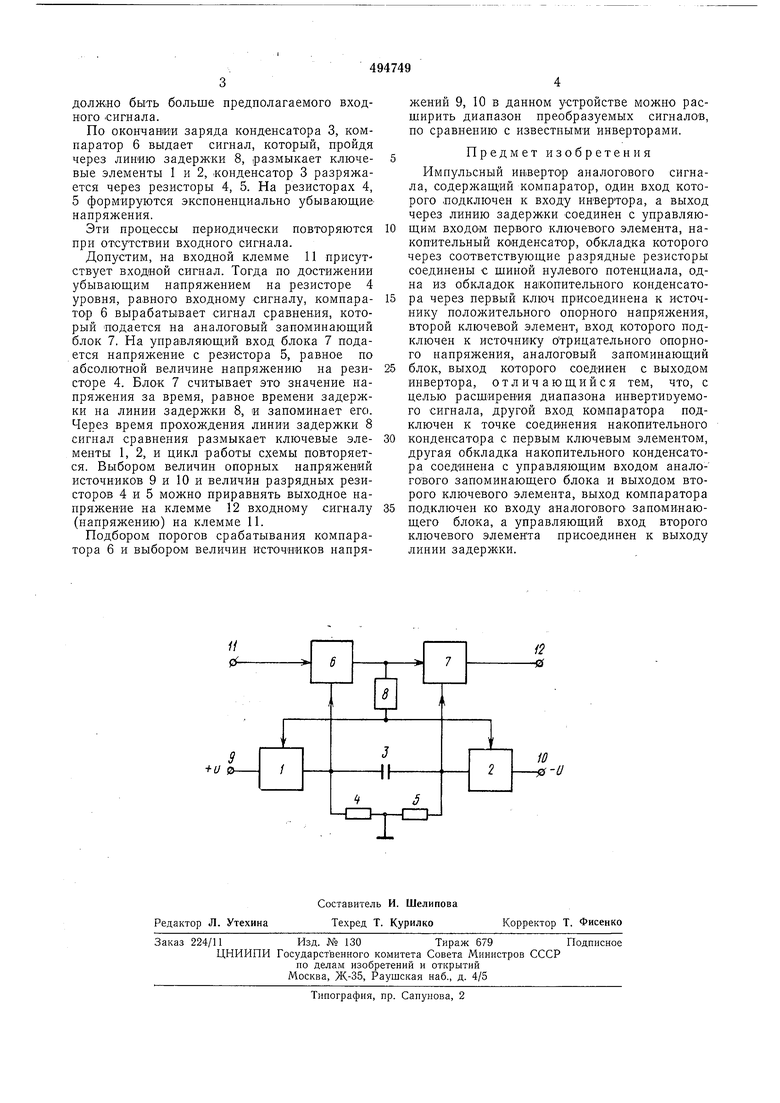

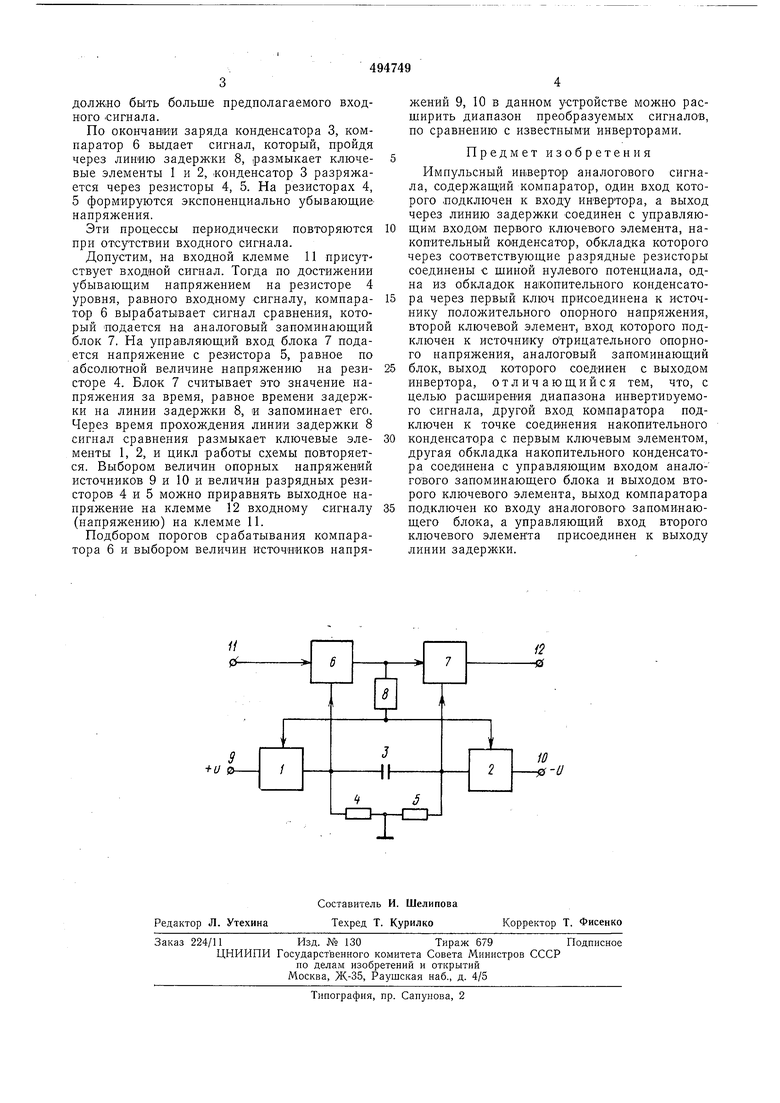

Блок-схема импульсного инвертора аналогового сигнала приведена на чептеже.

Устройство содержит первый ключевой элемент 1, второй ключевой элемент 2, накопительный конденсатор 3, разрядные резисторы 4, 5, компаратор 6, аналоговый запоминающий блок 7, линию задержки 8, источник положительного опорного напряжен.ия 9 и источник отрицательного опорного напряжения 10.

Устройство работает следующим образом.

Предположим, что в данный момент времени отсутствует входной сигнал LJ, накопителыный конденсатор 3 разряжен. Тогда, напряжение с выхода компаратора 6, соответствующее уровню «несравнение, через линию задержки 8 замыкает ключевые элементы 1 и 2 и конденсатор 3 быстро заряжается до на.пряжения, равного сумме опорных напряжений от источников 9 и 10, причем каждое из этих напряжений .по абсолю тной величине

должно быть больше предполагаемого входного .сигнала.

По окончании заряда конденсатора 3, компаратор 6 выдает сигнал, который, пройдя через линию задержки 8, размыкает ключевые элементы 1 и 2, конденсатор 3 разряжается через резисторы 4, 5. На резисторах 4, 5 формируются экспоненциально убывающие напряжения.

Эти процессы периодически повторяются при отсутствии входного сигнала.

Допустим, на входной клемме 11 присутствует входной сигнал. Тогда по достижении убывающим напряжением на резисторе 4 уровня, равного входному сигналу, компаратор 6 вырабатывает сигнал сравнения, который подается на аналоговый запоминающий блок 7. На управляющий вход блока 7 подается напряжение с резистора 5, равное по абсолютной величине напряжению на резисторе 4. Блок 7 считывает это значение напряжения за время, равное времени задержки на линии задержки 8, и запоминает его. Через время прохождения линии задержки 8 сигнал сравнения размыкает ключевые элементы 1, 2, и цикл работы схемы повторяется. Выбором величин опорных напряжений источников 9 и 10 и величин разрядных резисторов 4 и 5 можно приравнять выходное напряжение на клемме 12 входному сигналу (напряжению) на клемме 11.

Подбором порогов срабатывания компаратора 6 и выбором величин источников напряжений 9, 10 в данном устройстве можно расширить диапазон преобразуемых сигналов, по сравнению с известными инверторами.

Предметизобретения

Импульсный инвертор аналогового сигнала, содержащий компаратор, один вход которого подключен к входу инвертора, а выход через линию задержки соединен с управляющим входом нервого ключевого элемента, накопительный конденсатор, обкладка которого через соответствующие разрядные резисторы соединены с щиной нулевого потенциала, одна из обкладок накопительного конденсатора через первый ключ присоединена к источнику положительного опорного напряжения, второй ключевой элемент; вход которого подключен к источнику о грицательного опорного напряжения, аналоговый запоминающий

блок, выход которого соединен с выходом инвертора, отличающийся тем, что, с целью расширения диапазона инвертиоуемого сигнала, другой вход комиаратора подключен к точке соединения накопительного

конденсатора с первым ключевым элементом, другая обкладка накопительного конденсатора соединена с управляющим входом аналогового запоминающего блока и выходом второго ключевого элемента, выход компаратора

подключен ко входу аналогового запоминающего блока, а управляющий вход второго ключевого элемента присоединен к выходу линии задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНВЕРТОР | 2010 |

|

RU2448407C1 |

| Указатель экстремума | 1975 |

|

SU547777A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388987A1 |

| Устройство для определения моментов времени квантования сигналов | 1984 |

|

SU1167731A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU847374A1 |

| Устройство для задержки импульсных сигналов | 1980 |

|

SU921047A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU985828A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1234972A1 |

| Преобразователь разности фаз в напряжение | 1985 |

|

SU1273836A2 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841057A1 |

Авторы

Даты

1975-12-05—Публикация

1974-07-04—Подача