1

Изобретение относится к вычислительной технике, функциональным узлам вычислительных устройств.

Известно устройство, осуществляющее деление частоты на двенадцать, и содержащее пять триггеров, к входам которых подключены элементы совпадения, инвертор и логические элементы «ИЛИ.

Однако такое устройство имеет невысокую надежность.

Цель изобретения - повышение надежности работы устройства.

Для этого в предлагаемый делитель введены два дополнительных элемента совпадения и выходной элемент совпадения, причем прямая последовательность импульсов подана через элементы совпадения на входы четных триггеров и непосредственно на первый вход выходного элемента совпадения, а инверсная последовательность импульсов через элементы совпадения - на входы нечетных триггеров. Единичный выход первого триггера подключен через элементы совпадения к входам второго триггера и к единичным входам третьего и четвертого триггеров, нулевой выход первого триггера через дополнительные элементы совпадения - к входам второго триггера, через элементы совпадения - к нулевым входам третьего и четвертого триггеров и непосредственпо к второму входу выходного элемента

совпадения, единичный выход второго триггера через элементы совпадения - к входам первого и пятого триггеров, нулевой выход второго триггера через элементы совпадения-

к входам третьего триггера, единичный выход которого через элементы совпадения соединен с нулевым входом первого триггера, с входами второго триггера, с единичным входом пятого триггера и непосредственно с третьим

входом выходного элемента совпадения. Нулевой выход третьего триггера через элементы совпадения подключен к единичному входу первого триггера, к входам второго триггера и к нулевому входу нятого триггера. Единичный

и нулевой выходы четвертого триггера через элементы совпадения подключены соответственно к нулевому и единичному входам пятого триггера, единичный вход которого через элемент совпадения подключен к единичному

входу четвертого триггера, а нулевой вход через элемент совпадения - к нулевому входу четвертого триггера и непосредственно к четвертому входу выходного элемента совпадения.

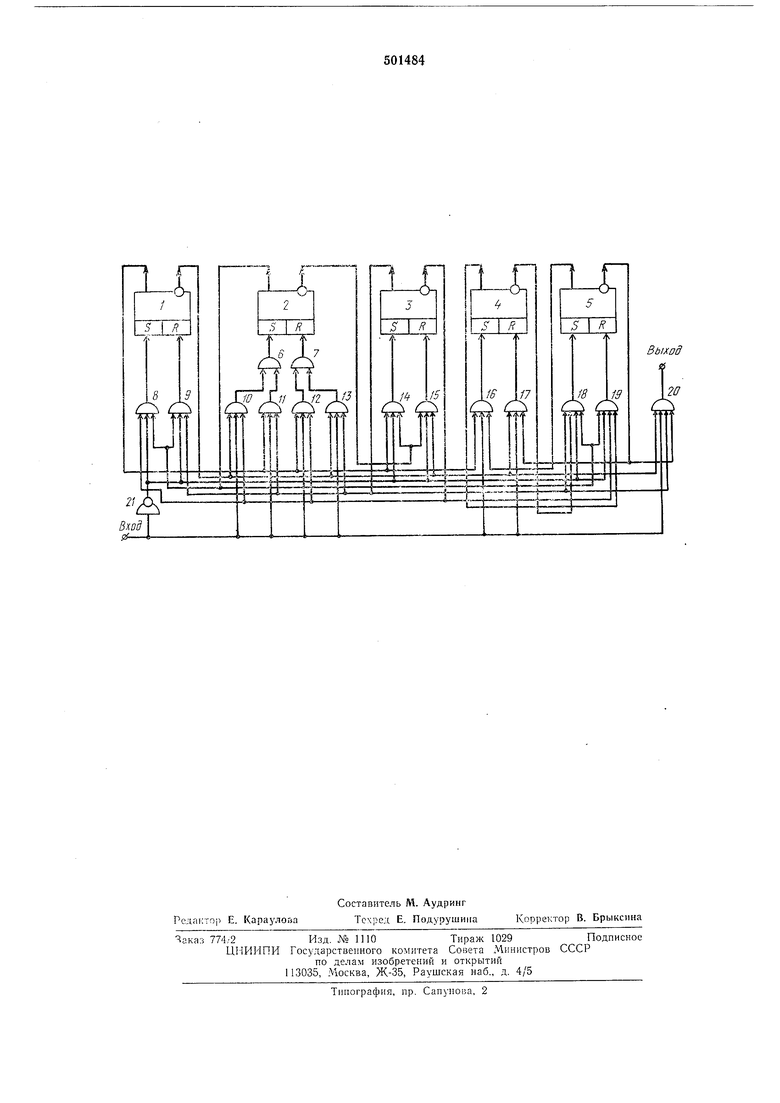

На чертеже представлена принципиальная структурная схема делителя частоты повторения импульсов на двенадцать.

В делитель входят потенциальные триггеры 1-5 с раздельными входами, состоящие из

двух схем «ИЛИ-НЕ (вход R - установка

в «О, вход 5 - установка в «1), элементы «ИЛИ 6, 7, элементы 8-19 совпадения, выходной элемент 20 совпадения и инвертор 21.

Делитель работает следующим образом.

За исходное состояние принимается наличие единичного потенциала на нулевых выходах триггеров 1-5 и на выходе инвертора 21. Первый импульс, пройдя элементы 10 и 6, изменяет состояние триггера 2. Затем появляется единичный потенциал на выходе инвертора 21. Пройдя элемент 8 совпадения, он измеряет состояние триггера 1. Второй импульс, проходит элементы 12 и 7 и возвращает триггер 2 в исходное состояние. Единичный потенциал, появивщийся на выходе инвертора 21, пройдя элемент 14 совпадения, изменяет состояние триггера 3.

Третий-импульс после прохода через элемент 11 совпадения изменяет состояние триггера 2. Затем появляется единичный потенциал на выходе инвертора 21 и, пройдя элементы 9 и 18 совпадения, изменяет состояние триггера 5 и устанавливает триггер 1 в исходное состояние. Четвертый импульс после прохода элемента 13 совпадения и элемента «ИЛИ 7 возвращает триггер 2 в исходное состояние. Единичный потенциал, появившийся на выходе инвертора 21 и прощедщий элемент 15 совпадения, устанавливает триггер 3 в исходное состояние.

Пятый импульс, пройдя элементы 10 и 6, изменяет состояние триггера 2, появившийся затем единичный потенциал на выходе .инвертора 21, пройдя элемент 8 совпадения, перебрасывает триггер I.

Шестой импульс проходит элементы 12, 7 и 16, возвращает триггер 2 в исходное состояние и изменяет состояние триггера 4. Затем появляется единичный потенциал на выходе инвертора 21 и, пройдя элемент 14 совпадения, перебрасывает триггер 3. Седьмой импульс проходит элементы 16 и 6, изменяет состояние триггера 2, затем появляется единичный потенциал на выходе инвертора 21 и, пройдя элемент 9 совпадения, устанавливая триггер 1 в исходное состояние. Восьмой импульс проходит элементы 13 и 7, возвращает триггер 2 в исходное состояние, затем появляется единичный потенциал на выходе инвертора 21 и, пройдя элемент 15 совпадения, устанавливает триггер 3 в исходное состояние.

Девятый импульс проходит элементы 10 и 6 и перебрасывает триггер 2, затем появляется единичный потенциал на выходе инвертора 21 и, пройдя элементы 8 и 19 совпадения, изме(яет состояние триггера I и возвращает триггер 5 в исходное состояние. Десятый импульс, прошедший элементы 12 и 7, переводит триггер 2 в исходное состояние, затем появляется единичный потенциал на выходе инвертора 21 и, пройдя элемент 14 совпадения, изменяет состояние триггера 3. Одиннадцатый импульс, пройдя элемент совпадения 11 и элемент «ИЛИ 6, перебрасывает триггер 2, появившийся затем единичный потенциал на выходе инвертора 21, пройдя элемент 9 совпадения, возвращает триггер 1 в исходное состояние. Двенадцатый импульс, прошедший элементы

13, 17, 7 и выходной элемент 20 совпадения, устанавливает триггеры 2 и 4 в исходное состояние и поступает на «Выход, затем появляется единичный потенциал на выходе инвертора 21 и, пройдя элемент 15 совпадения, возвращает триггер 3 в исходное состояние, при этом все устройство устанавливается в исходное состояние.

Формула изобретения

Делитель частоты повторения импульсов на

двенадцать, содержащий пять триггеров, к входам которых подключены элементы совпадения, инвертор и элементы «ИЛИ, отличающийся тем, что, с целью повышения надежности работы устройства, в него введены

два дополнительных элемента совпадения и выходной элемент совпадения, причем прямая последовательность импульсов подана через элементы совпадения на входы четных триггеров и непосредственно на первый вход выходиого элемента совпадения, а инверсная последовательность импульсов через элементы совпадепия - па входы нечетных триггеров, при этом единичный выход первого триггера нодключен через элементы совпадения к входам

второго триггера и к единичным входам третьего и четвертого триггеров, нулевой выход первого триггера через дополнительные элементы совпадения - к входам второго триггера, через элементы совпадения - к нулевым входам третьего и четвертого триггеров и непосредственно к второму входу выходного элемента совпадения, единичный выход второго триггера через элементы совпадения - к входам первого и пятого триггеров, пулевой

выход второго триггера через элементы совпадения - к входам третьего триггера, единичный выход которого через элементы совпадения соединен с нулевым входом первого триггера, с входами второго триггера, с единичным входом пятого триггера и непосредственно с третьим входом выходного элемента совпадепия, а нулевой выход третьего триггера через элементы совпадения подключен к единичному входу первого триггера, к входам

второго триггера и к нулевому входу пятого триггера, единичный и нулевой выходы четвертого триггера через элементы совпадения подключены соответственно к нулевому и единичному входам пятого триггера, единичный

вход которого через элемент совпадения подключен к единичному входу четвертого триггера, а нулевой вход через элемент совпадения - к нулевому входу четвертого триггера и непосредственно к четвертому входу выходного элемента совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты повторения импульсов | 1974 |

|

SU501483A1 |

| Делитель частоты повторения импульсов на восемнадцать | 1975 |

|

SU530465A1 |

| Делитель частоты повторения импульсов на четырнадцать | 1975 |

|

SU529562A1 |

| Устройство синхронизации | 1971 |

|

SU478429A1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU940285A1 |

| Тренажер для радиотелеграфиста | 1985 |

|

SU1325552A1 |

| Множительно-делительное устройство | 1977 |

|

SU696444A1 |

| Формирователь одиночного импульса | 1979 |

|

SU855973A1 |

| Делитель частоты повторения импульсов на пять | 1975 |

|

SU534874A1 |

| Формирователь последовательности кодов | 1974 |

|

SU526870A1 |

Авторы

Даты

1976-01-30—Публикация

1974-04-26—Подача