1

Изобретение относится к вычислительной технике и может быть использовано для обработки частотно-импульсных сигналов.

Известно дифферендируюш,ее устройство, содержащее преобразователь код-частота, реверсивный счетчик, входы которого соединены с выходами логического блока управления счетчиком, вход которого соединен с генератором управляемой частоты. В известном устройстве выходной сигнал F (t) формируется как результат усиления в /г раз разности входной частоты и частоты обратной связи

foe (О ,(i)dt,

и п

(}-YlP t)dt,

F,(t) k{F

J и о

откуда

dF(t)

rfF.v(0

т k

F,(t) Т dt dt

Р (i)

Т. e. выходной сигнал (t) пропорционален первой производной сигнала F . (t) с принциTU dF(t)

пиальной ошибкой k

которая при

dt

увеличении /е стремится к нулю. Приведенные формулы получены без учета дискретного характера частотно-импульсных сигналов и, следовательно, являются приближенными. Использование в качестве элемента сравнения

f д. (/) и FOC (О известных частотно-импульсных вычитающих устройств, обладающих характеристикой типа «люфт приводит к появлению задержки в прямой цепи устройства, непосредственно ухудшающей его динамические характеристики и, кроме того, ограничивает максимальную величину k из соображений устойчивости. Ограничение k в свою очередь тоже влияет на инерционность устройства. Следовательно, известное устройство характеризуется ограниченным быстродействием.

Целью изобретения является повыщение быстродействия дифференцирующего устройства, что достигается использованием попериодного сравнения частот F,. (t) и FQC (0. т- е. результат сравнения формируется по истечении периода меньшей из сравниваемых частот, в отличие от периода разностной частоты

в известном устройстве. Для достижения этого в описываемое устройство дополнительно введены схема сравнения периодов, интегратор, два ключа, преобразователь код-напряжение, схема сравнения, формирователь знака, аналоговый запоминающий блок и делитель, первый вход которого соединен с выходом нреобразователя код-частота, второй вход - с первым выходом схемы сравнения периодов, а выход - с первым входом схемы

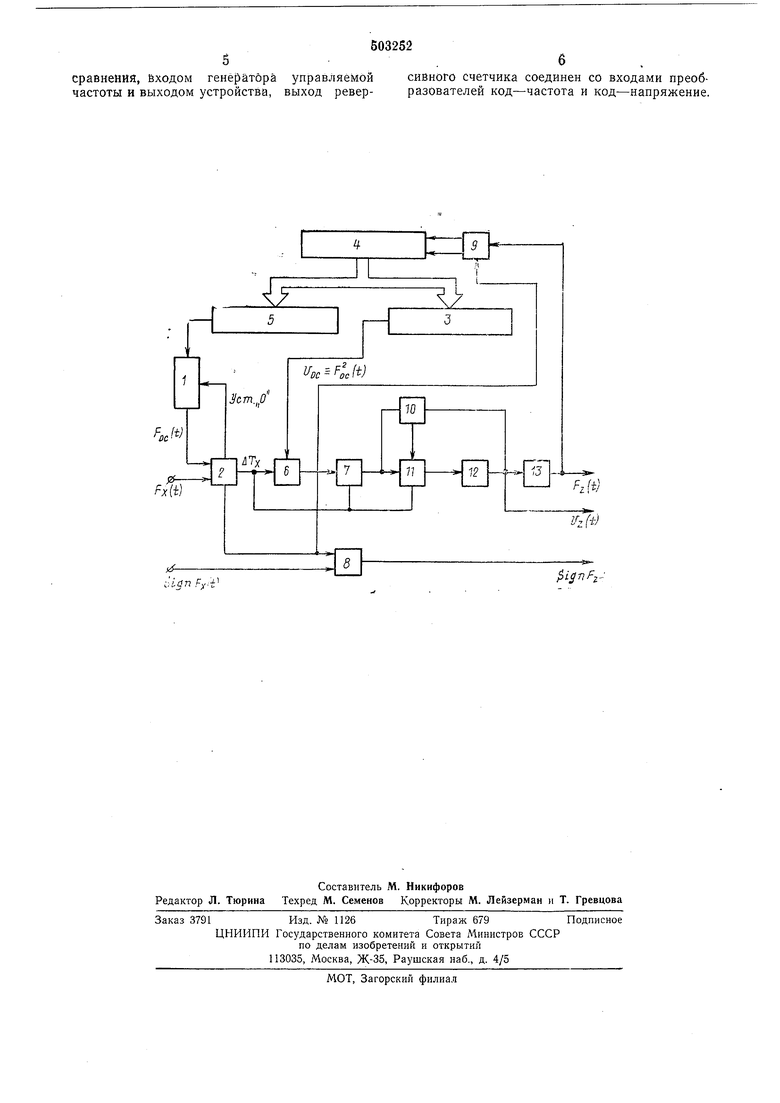

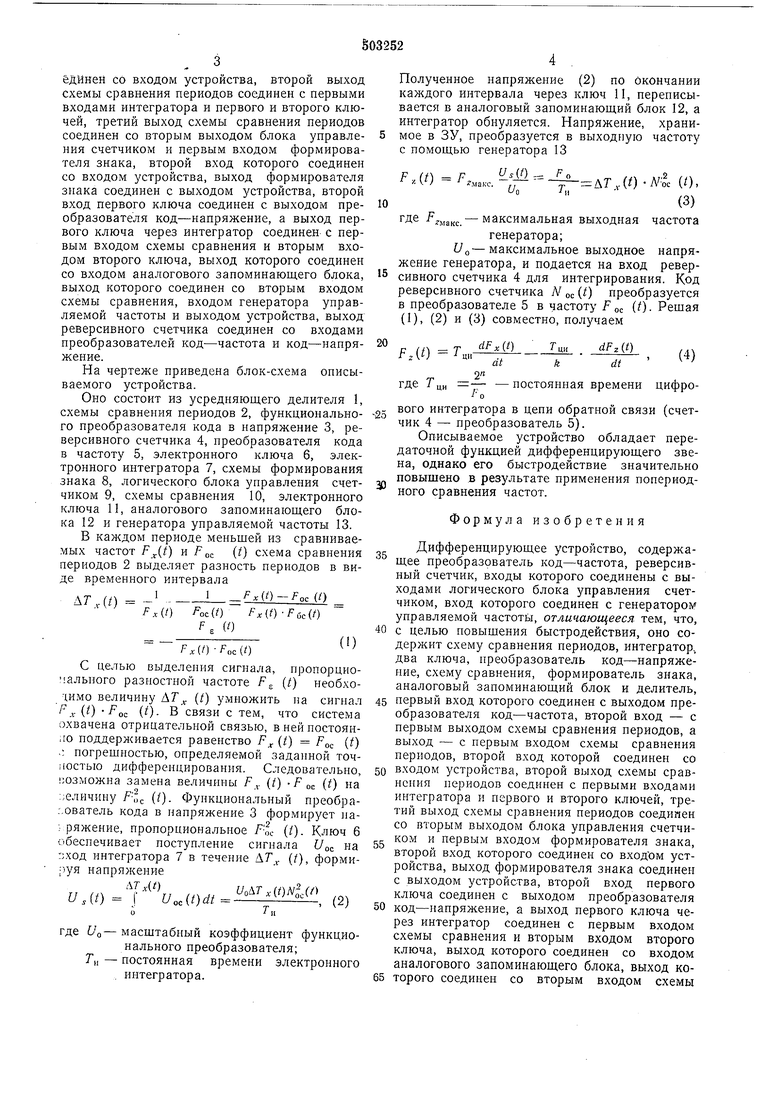

сравнения нериодов, второй вход которой соединен со входом устройства, второй выход схемы сравнения периодов соединен с первыми входами интегратора и первого и второго ключей, третий выход схемы сравнения периодов соединен со вторым выходом блока управления счетчиком и первым входом формирователя знака, второй вход которого соединен со входом устройства, выход формирователя знака соединен с выходом устройства, второй вход первого ключа соединен с выходом преобразователя код-напряжение, а выход первого ключа через интегратор соединен с первым входом схемы сравнения и вторым входом второго ключа, выход которого соединен со входом аналогового запоминающего блока, выход которого соединен со вторым входом схемы сравнения, входом генератора управляемой частоты и выходом устройства, выход реверсивного счетчика соединен со входами преобразователей код-частота и код-напряжение. На чертеже приведена блок-схема описываемого устройства. Оно состоит из усредняющего делителя 1, схемы сравнения периодов 2, функционального преобразователя кода в напряжение 3, реверсивного счетчика 4, преобразователя кода в частоту 5, электронного ключа 6, электронного интегратора 7, схемы формирования знака 8, логического блока управления счетчиком 9, схемы сравнения 10, электронного ключа 11, аналогового запоминающего блока 12 и генератора управляемой частоты 13. В каждом периоде меньшей из сравниваемых частот Fj.(t) и FOC (О схема сравнения периодов 2 выделяет разность периодов в виде временного интервала J./ лгСО- ос (О АГ.ЛО Fx(t} -РОС (ОF(t),(t) РАП F,,c(t) С целью выделения сигнала. пропорцио ального разностной частоте F (/) необхо( величину (/) умножить на сигнал /-,- (О /ос (О- В связи с тем, что система охвачена отрицательной связью, в ней постоянло поддерживается равенство Р, (t) f ос (О ,; погрещностью, определяемой заданной точностью дифференцирования. Следовательно, ;озможна замена величины F . (/) -foe (О на :;еличину F-f, (/). Функциональный преобра..ователь кода в напряжение 3 формирует на: ряжение, пропорциональное FOC (/). Ключ 6 обеспечивает поступление сигнала f/oc на т;ход интегратора 7 в течение ДГ (/), формируя напряжение Ar,v(/) и,Т (t)Nl(f) (О и. ;(ОЛ где бо- масщтабный коэффициент функционального преобразователя; Г„ - постоянная времени электронного интегратора. Полученное напряжение (2) по окончании каждого интервала через ключ 11, переписывается в аналоговый запоминающий блок 12, а интегратор обнуляется. Напряжение, хранимое в ЗУ, преобразуется в выходную частоту с помощью генератора 13 р (t ри s(t) Л-ос (О, АГ.,(0 Г у. (ч - / ftiaicc. ,7 (3) где /o.jiaKc -максимальная выходная частота генератора; и о-максимальное выходное напряжение генератора, и подается на вход реверсивного счетчика 4 для интегрирования. Код реверсивного счетчика Л ос (О преобразуется в преобразователе 5 в частоту F„с (О- Решая (I), (2) и (3) совместно, получаем f.W 7ш где Гци - постоянная времени вого интегратора в цепи обратной связи (счетчик 4 - преобразователь 5). Описываемое устройство обладает передаточной функцией дифференцирующего звена, однако его быстродействие значительно повышено в результате применения попериодного сравнения частот. Формула изобретения Дифференцирующее устройство, содержащее преобразователь код-частота, реверсивный счетчик, входы которого соединены с выходами логического блока управления счетчиком, вход которого соединен с генератором управляемой частоты, отличающееся тем, что, с целью повышения быстродействия, оно содержит схему сравнения периодов, интегратор, два ключа, преобразователь код-напряжение, схему сравнения, формирователь знака, аналоговый запоминающий блок и делитель, первый вход которого соединен с выходом преобразователя код-частота, второй вход - с первым выходом схемы сравнения периодов, а выход - с первым входом схемы сравнения периодов, второй вход которой соединен со входом устройства, второй выход схемы сравнения периодов соединен с первыми входами интегратора и первого и второго ключей, третий выход схемы сравнения периодов соединен со вторым выходом блока управления счетчиком и первым входом формирователя знака, второй вход которого соединен со входом устройства, выход формирователя знака соединен с выходом устройства, второй вход первого ключа соединен с выходом преобразователя код-напряжение, а выход первого ключа через интегратор соединен с первым входом схемы сравнения и вторым входом второго ключа, выход которого соединен со входом аналогового запоминающего блока, выход которого соединен со вторым входом схемы S сравнения, входом генератора управляемой частоты и выходом устройства, выход ревер.6 сивного счетчика соединен со входами преобразователей код-частота и код-напряжение.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

| ЦИФРОВОЙ ВИБРОМЕТР | 1973 |

|

SU398835A1 |

| Цифровой измеритель симметричных составляющих трехфазной сети | 1982 |

|

SU1056081A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Аналого-цифровой преобразователь действующего значения напряжения | 1987 |

|

SU1585898A1 |

| Цифровой измеритель относительной разности скоростей | 1977 |

|

SU717657A1 |

| Частотно-импульсный функциональный преобразователь двух переменных | 1972 |

|

SU437076A1 |

| Цифровой феррозондовый магнитометр | 1982 |

|

SU1114997A1 |

| Следящая система | 1985 |

|

SU1290251A1 |

| Аналого-цифровой преобразователь температуры | 1979 |

|

SU855412A1 |

Авторы

Даты

1976-02-15—Публикация

1974-01-31—Подача